lcd panel with transistors on the back free sample

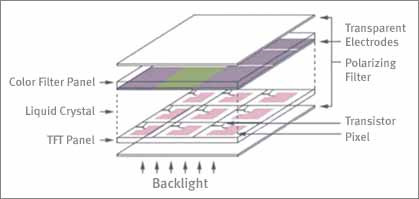

A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display that uses thin-film-transistor technologyactive matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven (i.e. with segments directly connected to electronics outside the LCD) LCDs with a few segments.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968. In 1971, Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated a 2-by-18 matrix display driven by a hybrid circuit using the dynamic scattering mode of LCDs.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).active-matrix liquid-crystal display (AM LCD) using CdSe TFTs in 1974, and then Brody coined the term "active matrix" in 1975.high-resolution and high-quality electronic visual display devices use TFT-based active matrix displays.

The liquid crystal displays used in calculators and other devices with similarly simple displays have direct-driven image elements, and therefore a voltage can be easily applied across just one segment of these types of displays without interfering with the other segments. This would be impractical for a large display, because it would have a large number of (color) picture elements (pixels), and thus it would require millions of connections, both top and bottom for each one of the three colors (red, green and blue) of every pixel. To avoid this issue, the pixels are addressed in rows and columns, reducing the connection count from millions down to thousands. The column and row wires attach to transistor switches, one for each pixel. The one-way current passing characteristic of the transistor prevents the charge that is being applied to each pixel from being drained between refreshes to a display"s image. Each pixel is a small capacitor with a layer of insulating liquid crystal sandwiched between transparent conductive ITO layers.

The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. However, rather than fabricating the transistors from silicon, that is formed into a crystalline silicon wafer, they are made from a thin film of amorphous silicon that is deposited on a glass panel. The silicon layer for TFT-LCDs is typically deposited using the PECVD process.

Polycrystalline silicon is sometimes used in displays requiring higher TFT performance. Examples include small high-resolution displays such as those found in projectors or viewfinders. Amorphous silicon-based TFTs are by far the most common, due to their lower production cost, whereas polycrystalline silicon TFTs are more costly and much more difficult to produce.

The twisted nematic display is one of the oldest and frequently cheapest kind of LCD display technologies available. TN displays benefit from fast pixel response times and less smearing than other LCD display technology, but suffer from poor color reproduction and limited viewing angles, especially in the vertical direction. Colors will shift, potentially to the point of completely inverting, when viewed at an angle that is not perpendicular to the display. Modern, high end consumer products have developed methods to overcome the technology"s shortcomings, such as RTC (Response Time Compensation / Overdrive) technologies. Modern TN displays can look significantly better than older TN displays from decades earlier, but overall TN has inferior viewing angles and poor color in comparison to other technology.

Most TN panels can represent colors using only six bits per RGB channel, or 18 bit in total, and are unable to display the 16.7 million color shades (24-bit truecolor) that are available using 24-bit color. Instead, these panels display interpolated 24-bit color using a dithering method that combines adjacent pixels to simulate the desired shade. They can also use a form of temporal dithering called Frame Rate Control (FRC), which cycles between different shades with each new frame to simulate an intermediate shade. Such 18 bit panels with dithering are sometimes advertised as having "16.2 million colors". These color simulation methods are noticeable to many people and highly bothersome to some.gamut (often referred to as a percentage of the NTSC 1953 color gamut) are also due to backlighting technology. It is not uncommon for older displays to range from 10% to 26% of the NTSC color gamut, whereas other kind of displays, utilizing more complicated CCFL or LED phosphor formulations or RGB LED backlights, may extend past 100% of the NTSC color gamut, a difference quite perceivable by the human eye.

The transmittance of a pixel of an LCD panel typically does not change linearly with the applied voltage,sRGB standard for computer monitors requires a specific nonlinear dependence of the amount of emitted light as a function of the RGB value.

In-plane switching was developed by Hitachi Ltd. in 1996 to improve on the poor viewing angle and the poor color reproduction of TN panels at that time.

Initial iterations of IPS technology were characterised by slow response time and a low contrast ratio but later revisions have made marked improvements to these shortcomings. Because of its wide viewing angle and accurate color reproduction (with almost no off-angle color shift), IPS is widely employed in high-end monitors aimed at professional graphic artists, although with the recent fall in price it has been seen in the mainstream market as well. IPS technology was sold to Panasonic by Hitachi.

Most panels also support true 8-bit per channel color. These improvements came at the cost of a higher response time, initially about 50 ms. IPS panels were also extremely expensive.

IPS has since been superseded by S-IPS (Super-IPS, Hitachi Ltd. in 1998), which has all the benefits of IPS technology with the addition of improved pixel refresh timing.

In 2004, Hydis Technologies Co., Ltd licensed its AFFS patent to Japan"s Hitachi Displays. Hitachi is using AFFS to manufacture high end panels in their product line. In 2006, Hydis also licensed its AFFS to Sanyo Epson Imaging Devices Corporation.

It achieved pixel response which was fast for its time, wide viewing angles, and high contrast at the cost of brightness and color reproduction.Response Time Compensation) technologies.

Less expensive PVA panels often use dithering and FRC, whereas super-PVA (S-PVA) panels all use at least 8 bits per color component and do not use color simulation methods.BRAVIA LCD TVs offer 10-bit and xvYCC color support, for example, the Bravia X4500 series. S-PVA also offers fast response times using modern RTC technologies.

When the field is on, the liquid crystal molecules start to tilt towards the center of the sub-pixels because of the electric field; as a result, a continuous pinwheel alignment (CPA) is formed; the azimuthal angle rotates 360 degrees continuously resulting in an excellent viewing angle. The ASV mode is also called CPA mode.

A technology developed by Samsung is Super PLS, which bears similarities to IPS panels, has wider viewing angles, better image quality, increased brightness, and lower production costs. PLS technology debuted in the PC display market with the release of the Samsung S27A850 and S24A850 monitors in September 2011.

TFT dual-transistor pixel or cell technology is a reflective-display technology for use in very-low-power-consumption applications such as electronic shelf labels (ESL), digital watches, or metering. DTP involves adding a secondary transistor gate in the single TFT cell to maintain the display of a pixel during a period of 1s without loss of image or without degrading the TFT transistors over time. By slowing the refresh rate of the standard frequency from 60 Hz to 1 Hz, DTP claims to increase the power efficiency by multiple orders of magnitude.

Due to the very high cost of building TFT factories, there are few major OEM panel vendors for large display panels. The glass panel suppliers are as follows:

External consumer display devices like a TFT LCD feature one or more analog VGA, DVI, HDMI, or DisplayPort interface, with many featuring a selection of these interfaces. Inside external display devices there is a controller board that will convert the video signal using color mapping and image scaling usually employing the discrete cosine transform (DCT) in order to convert any video source like CVBS, VGA, DVI, HDMI, etc. into digital RGB at the native resolution of the display panel. In a laptop the graphics chip will directly produce a signal suitable for connection to the built-in TFT display. A control mechanism for the backlight is usually included on the same controller board.

The low level interface of STN, DSTN, or TFT display panels use either single ended TTL 5 V signal for older displays or TTL 3.3 V for slightly newer displays that transmits the pixel clock, horizontal sync, vertical sync, digital red, digital green, digital blue in parallel. Some models (for example the AT070TN92) also feature input/display enable, horizontal scan direction and vertical scan direction signals.

New and large (>15") TFT displays often use LVDS signaling that transmits the same contents as the parallel interface (Hsync, Vsync, RGB) but will put control and RGB bits into a number of serial transmission lines synchronized to a clock whose rate is equal to the pixel rate. LVDS transmits seven bits per clock per data line, with six bits being data and one bit used to signal if the other six bits need to be inverted in order to maintain DC balance. Low-cost TFT displays often have three data lines and therefore only directly support 18 bits per pixel. Upscale displays have four or five data lines to support 24 bits per pixel (truecolor) or 30 bits per pixel respectively. Panel manufacturers are slowly replacing LVDS with Internal DisplayPort and Embedded DisplayPort, which allow sixfold reduction of the number of differential pairs.

Backlight intensity is usually controlled by varying a few volts DC, or generating a PWM signal, or adjusting a potentiometer or simply fixed. This in turn controls a high-voltage (1.3 kV) DC-AC inverter or a matrix of LEDs. The method to control the intensity of LED is to pulse them with PWM which can be source of harmonic flicker.

The bare display panel will only accept a digital video signal at the resolution determined by the panel pixel matrix designed at manufacture. Some screen panels will ignore the LSB bits of the color information to present a consistent interface (8 bit -> 6 bit/color x3).

With analogue signals like VGA, the display controller also needs to perform a high speed analog to digital conversion. With digital input signals like DVI or HDMI some simple reordering of the bits is needed before feeding it to the rescaler if the input resolution doesn"t match the display panel resolution.

The statements are applicable to Merck KGaA as well as its competitors JNC Corporation (formerly Chisso Corporation) and DIC (formerly Dainippon Ink & Chemicals). All three manufacturers have agreed not to introduce any acutely toxic or mutagenic liquid crystals to the market. They cover more than 90 percent of the global liquid crystal market. The remaining market share of liquid crystals, produced primarily in China, consists of older, patent-free substances from the three leading world producers and have already been tested for toxicity by them. As a result, they can also be considered non-toxic.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

Richard Ahrons (2012). "Industrial Research in Microcircuitry at RCA: The Early Years, 1953–1963". 12 (1). IEEE Annals of the History of Computing: 60–73. Cite journal requires |journal= (help)

K. H. Lee; H. Y. Kim; K. H. Park; S. J. Jang; I. C. Park & J. Y. Lee (June 2006). "A Novel Outdoor Readability of Portable TFT-LCD with AFFS Technology". SID Symposium Digest of Technical Papers. AIP. 37 (1): 1079–82. doi:10.1889/1.2433159. S2CID 129569963.

Kim, Sae-Bom; Kim, Woong-Ki; Chounlamany, Vanseng; Seo, Jaehwan; Yoo, Jisu; Jo, Hun-Je; Jung, Jinho (15 August 2012). "Identification of multi-level toxicity of liquid crystal display wastewater toward Daphnia magna and Moina macrocopa". Journal of Hazardous Materials. Seoul, Korea; Laos, Lao. 227–228: 327–333. doi:10.1016/j.jhazmat.2012.05.059. PMID 22677053.

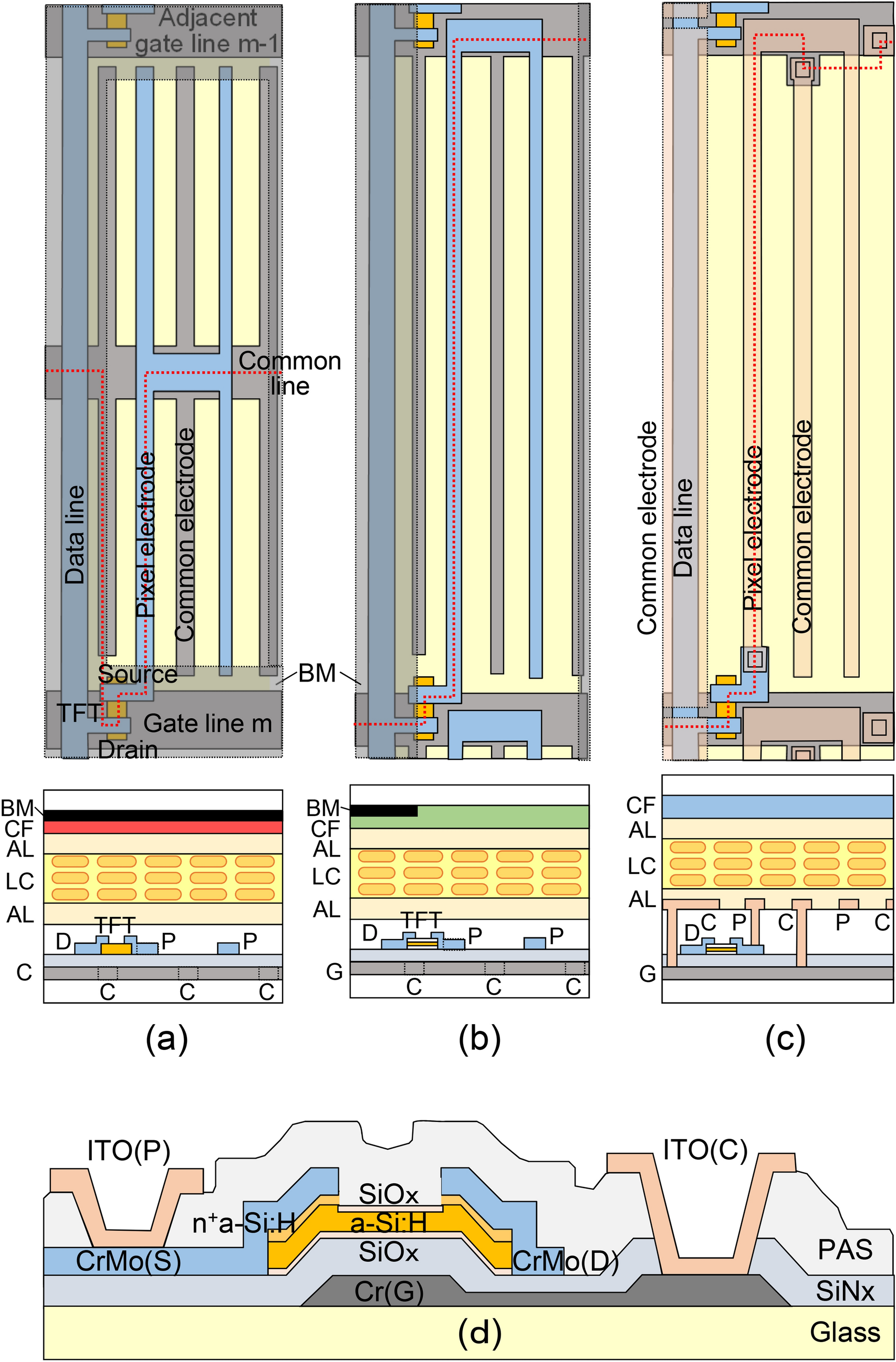

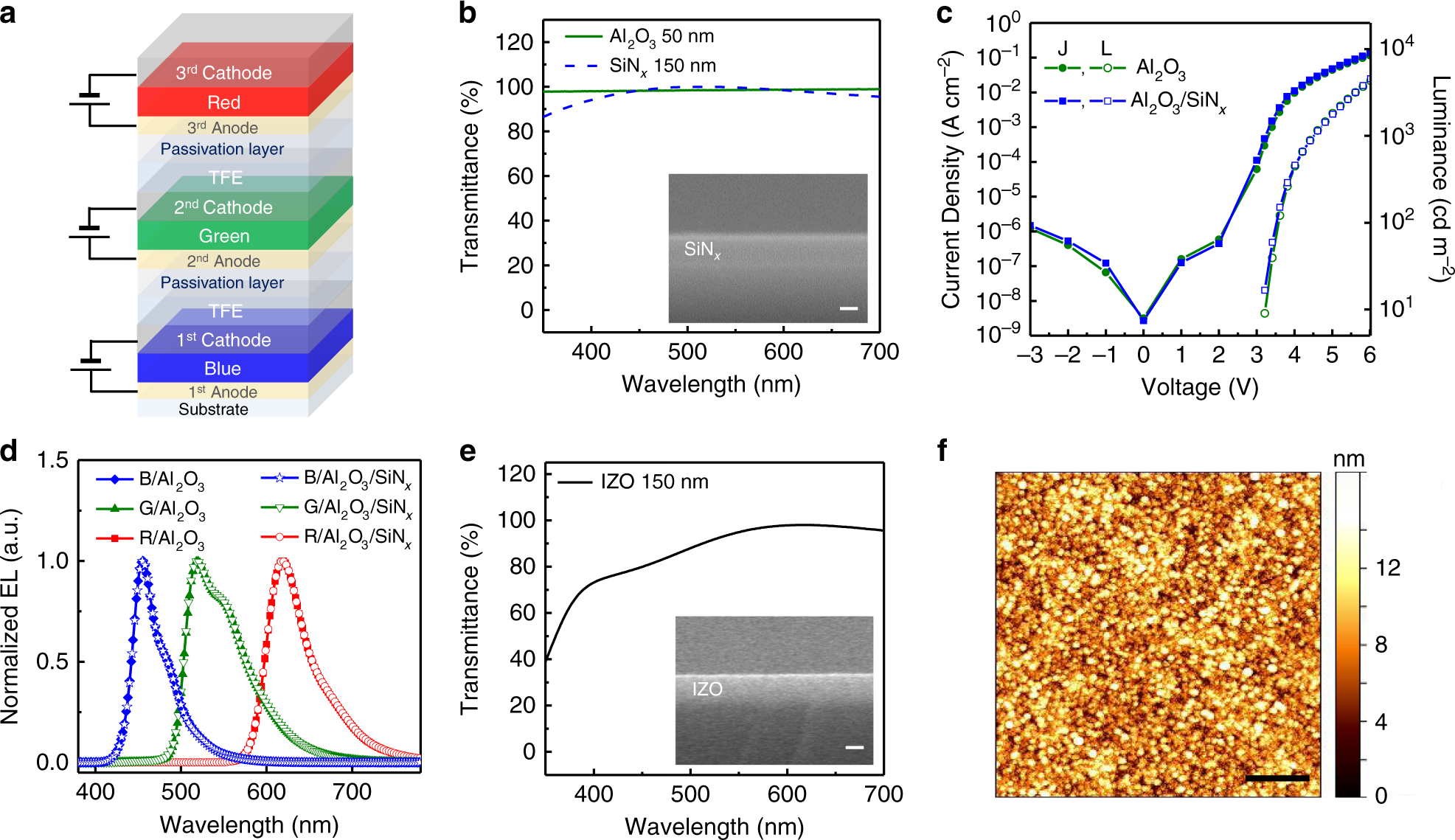

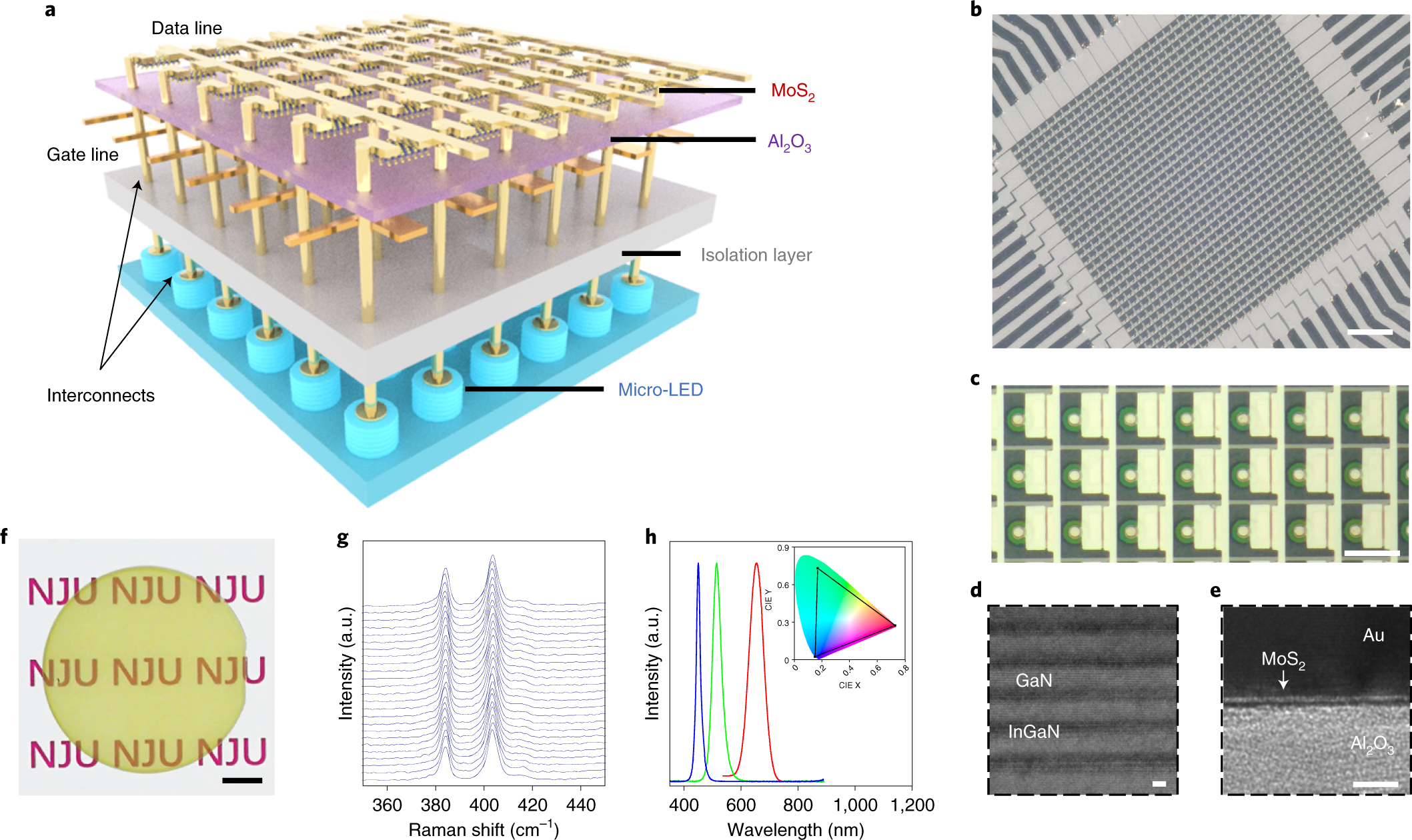

Figures 3a–d show optical and SEM (scanning electron microscopy) images of the fabricated CL and CLSE pixel structures. Each structure has the same pixel size (80 μm × 240 μm) and minimum pattern size (5 μm). As shown in Fig. 3d, the white line patterns are the ITO interdigitated pixel and common electrodes. They are well connected to the source electrode and gate line via through holes, and the common electrodes at both ends cover the underlying data lines to prevent electrical noise from being applied to the LC layer. As will be shown later, this noise shield electrode (SE) is what makes the black matrix above the data line unnecessary

Optical and SEM (scanning electron microscopy) images of fabricated (a, b) CL and (c, d) CLSE pixel structures. The five white line patterns in (d) are the ITO interdigitated pixel and common electrodes. (e) Images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel. (f) The three-black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM) and (g) optical images of pixels without BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines).

Figure 3e shows images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel fabricated in our laboratory, (f) the three black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM), and (g) optical images of panel areas without the BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines). As can be seen in the image from the normal direction, the brightness and contrast of the display area with the top BM and middle BM patterns are almost the same, but the contrast of the display area without the BM is relatively lower because of the lower darkness level of the LC off pixels indicating “HITACHI”. As shown in Fig. 3g, this is due to light leaking through the aperture between the data line and adjacent common lines. Therefore, in the CL structure, the BM on the drain line is necessary to obtain a high contrast ratio by shielding light leakage. This is the same as in the conventional structure. On the contrary, there is no light leakage along the gate line through the gaps between the gate line and edges of the pixel/common electrodes, as is clearly shown in Fig. 3g. This is a unique advantage of the CL structure because the conventional structure must shield these gaps with the BM to prevent light leakage. The suppression of light leakage along the gate line in the CL structure is due to the driving scheme (see Fig. 2b,a for a comparison with the conventional structure). During the holding period (tOFF) in the conventional structure, regardless of the pixel voltage, Vp (including Vp = 0), nonzero Vgp and Vgc are always applied to keep the TFT off, and these voltages are applied to the LC layer, inducing light leakage as reported in

Figure 4a shows the gate voltage (Vg) dependence of the panel brightness, while the inset shows that of the TFT current (transfer characteristics). The gray curves are for the conventional IPS TFT-LCD with the TFT before enhancement, the common line, and the matrix BM (MBM) shown at the top of Fig. 3f. The blue curves are for the proposed CL structure with the enhanced TFT and the stripe BM (SBM) shown in the middle of Fig. 3f. In this case, enhanced TFT characteristics were obtained by using an MNOS TFT without back-channel oxidation that was enhanced by the BTS process. In both structures, the threshold voltages for panel brightness, defined by extrapolating the straight part of the brightness curves, reflect those of the TFT transfer curves defined as Vg at a drain current of 10−12 A, and they are well matched to be 4 V and 9 V, respectively. The maximum brightness for the CL structure is 137% higher than that for the conventional structure, which is due to the increase in the aperture ratio from 38 to 52% that results from the elimination of the common line and the BM covering the gate line.

(a) Dependence of panel brightness and TFT current on gate voltage for the conventional pixel structure of 38% aperture ratio (AR) with matrix black matrix (MBM) over both drain and gate lines and proposed CL pixel structure of 52% AR with strip black matrix (SBM) over only the drain lines. Transfer characteristics before and after bias temperature stress (BTS) treatment are shown in the inset. (b) Charging and (c) holding characteristics of enhanced TFT of the CL structure with gate as a common line. Vg and Vd in the TFT ON state are 30 V and +/−7 V, respectively.

To estimate the charging and holding characteristics of the MNOS-enhanced TFT in the panel, the gate TFT ON and OFF time dependences of the panel brightness were measured (Fig. 4b,c). The charging characteristics in Fig. 4b are plotted as a function of tON at tOFF = 16.6 ms, Vg = 30 V, and Vd = ± 7 V. The holding characteristics in Fig. 4c are plotted as a function of tOFF at tON = 34 μs. 95.1% charging at tON = 34 μs and 95.3% holding at tOFF = 16.6 ms indicate that the enhanced TFT has sufficient charging and holding performance to drive a standard VGA (640 × 480 pixels) panel (the number of scanning lines is estimated as tOFF/tON = 16.6/0.034 = 488).

To confirm the driving conditions for the CL structure without the BM along the gate line (with the SBM), the tOFF dependence of the contrast ratio (CR) in the CL panel was further investigated as shown in Fig. 5a, where CR is plotted as a function of tOFF for the CL panels with the matrix BM (MBM) and the strip BM (SBM). The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. The SBM and MBM panels keep CR higher than 240 with tOFF > 16.6 ms, the frame period of a display panel without flicker being noticeable to the human eye. both panels decrease CR when tOFF is less than 16.6 ms; the CR of the SBM panel decreases faster than the CR of the MBM panel. As shown in the inset, the decrease in CR was due to the increase in dark-state brightness with decreasing tOFF as light leakage increases along the gate line. This light leakage is induced by the voltage Vgp = Vgc = VgON = 30 V applied only for 34 μs during the TFT ON (charging) state, which is 1/488th the duration, tOFF = 16.6 ms, of the TFT OFF (holding) state with Vgp = Vgc = VgOFF = 0 V, but the ratio increases with decreasing tOFF and becomes effective enough to switch on LC layer and induce light leakage. However, it should be stressed again that the CL panel with the normal holding (TFT OFF) time of 16.6 ms does not suffer from the light leakage along the gate line, so the aperture ratio can be increased by removing the BM along the gate line.

(a) Contrast ratio (CR) for CL panels with matrix BM (MBM) and stripe BM (SBM) plotted as a function of tOFF. The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. Vd (= VLC) dependence of (b) brightness and (c) contrast ratio of the CLSE panel. Insets of (b): optical images indicating the elimination of the BM from the CLSE structure (upper left) and the MBM in the conventional structure (lower right). Insets of (c): CLSE panel composed of different areas with three different pixel structures and aperture ratios (ARs), i.e., CLSE structure without BM (60%), CL structure with SBM (52%), and conventional structure with MBM (38%).

Figure 5b,c shows the Vd (= VLC) dependence of the brightness and contrast ratio of the CLSE panel without a BM along the drain line and along the gate line. As shown in the optical images in the insets of Fig. 5c, the CLSE panel has different areas with three different pixel structures and aperture ratios (ARs), i.e., the CLSE structure without the BM (60%), the CL structure with the SBM (52%), and the conventional structure with the MBM (38%). The optical images in the inset of Fig. 5b clearly indicate the elimination of the BM from the CLSE structure and the MBM in the conventional structure. The ratios of the bright area in the CLSE and conventional pixels shown in the red dotted square appear higher than the aperture ratios because the pixel and common electrodes are invisible due to the brightness. The brightness and contrast ratio in each area increase with increasing Vd; the ratios for the CLSE structure without the BM are approximately 160% those of the conventional structure with the MBM, reflecting the difference in aperture ratio.

Figure 6 indicates the effect of bias temperature stress (BTS) on the TFT characteristics. As the stressing time, tS, of the positive gate stress voltage, Vst = + 77 V, increases from 0 to 3600 s, the transfer (Id-Vg) curve shifts in the positive direction (Fig. 6a). Vth is defined as Vg at which Id = 10−12 A and ΔVth is defined as the Vth shift from the initial value via BTS. As shown in Fig. 6b, ΔVth increases logarithmically with increasing tS: ΔVth = 2.17 + 4.93 × log (tS). The mechanism behind the gate-stress-induced Vth shift is electron tunnel injection from the a-Si:H semiconductor into the SiOx gate insulator. For confirmation, ΔVth of MNOS TFTs with different SiOx thicknesses is plotted as a function of the electric field applied to the SiOx layer in Fig. 6c. Here, the thickness of the SiOx was varied (5, 10, 20, 50 nm), while the SiN thickness was fixed at 200 nm. The electric field applied to SiOx, Eox, was calculated using the following equation,

Effect of bias temperature stress (BTS) on TFT characteristics. (a) The transfer (Id–Vg) curve shifts in the positive direction with positive gate bias stress of Vst = + 77 V over the duration of 0–3600 s. (b) ΔVth, defined as the Vth shift from the initial value via BTS, increases logarithmically with increasing tS, following ΔVth = 2.17 + 4.93 × log (tS). (c) ΔVth of MNOS TFTs with different SiOx thicknesses from 5 to 50 nm as a function of the electric field applied to the SiOx layer.

where εo = 3.5 and do are the electrical permittivity and thicknesses of SiOx and εn = 7 and dn = 200 nm are those of SiN. ΔVth linearly increases at a threshold electric field at 4.6 MV/cm on the same straight line regardless of the thickness of SiOx. From these results, we concluded that the Vst-induced Vth shift mechanism is Fowler–Nordheim type tunneling injection

Figure 7a shows the effect of back-channel oxidation (BCO) and passivation (PAS) on the Id-Vg characteristics of the MNOS TFT. The Id-Vg curve with Vth = 5.1 V is further enhanced to Vth = 10.9 V after BCO, although there is a slight degradation of the slope of the current increase in the sub-threshold region. The slope recovers after PAS without any change to the enhanced characteristics

(a) Effect of back-channel oxidation (BCO) and passivation (PAS) on Id–Vg characteristics of MNOS TFT. (b) Vth and Vth standard deviation, σVth, after BTS and after BCO without BTS treatments and (c) SiOX thickness as a function of position along gate-line, x.

The advantage of BCO over BTS is the uniformity of the enhanced characteristics; Fig. 7b shows the distribution of the enhanced Vth as a function of position along gate-line, x, for the MNOS TFTs connected with a 90-mm-long gate line in the TFT substrate after BTS and BCO treatments. The average value of Vth and the standard deviation, σVth, for pristine TFTs before BTS or BCO, are 5.1 V and 0.35 V, respectively. After BCO, Vth is uniformly enhanced, with an average Vth = 11 V and σVth = 0.4 V without increasing σVth. On the other hand, after BTS, Vth is nonuniformly enhanced with an average Vth = 9.3 V and σVth of 1.4 V. In particular, Vth increases linearly as a function of position along gate-line, x. As the gate SiOx thickness linearly decreases, from (54 nm) to (47 nm) with increasing x as shown in Fig. 7c, the increase in ΔVth after BTS with x is due to increase in the electric field applied to SiOx as shown in Fig. 6c and Eq. 1.

It has been shown that the Vth of the MNOS TFT is independent of the gate SiOx thickness when the thickness is more than 5 nm8a, Vth of the MNOS TFT with the BCO treatment becomes almost independent of the BCO SiOx thickness. As shown in the inset, the thickness of BCO SiOx composed of oxidized a-Si:H linearly increases with BCO processing time, and the Vth increase almost saturates at a BCO SiOx thickness greater than 5 nm. Therefore, the enhanced MNOS TFT after BCO has a uniformly high Vth that is robust to thickness fluctuations of the gate and BCO SiOx layers. BCO also has an advantage over BTS in terms of the stability of Vth as shown in Fig. 8b, which plots the annealing time dependence of Vth for BCO and BTS. In this experiment, the stoichiometry (x) of the gate SiOx was 1.78 for BTS and 1.78 and 1.9 for BCO. The annealing temperature in the N2 atmosphere was 200 °C. In the case of BTS, Vth decreased to the pristine value after approximately 5 h of annealing, while Vth decreased more slowly in the case of BCO. In particular, the annealing time required for Vth to fall to 7 V was 7.5 times longer than that of BTS. Increasing the stoichiometry (x) of the gate SiOx dramatically improved the BCO-enhanced Vth to as much as 11 V, which was stably maintained after 24 h of annealing at 200 °C.

(a) Dependence of Vth on thickness of back-channel oxidized (BCO) SiOX. The inset shows the SiOx thickness dependence on the BCO process time for RF powers of 200 W and 500 W. (b) Stability of Vth as a function of annealing time for three different TFTs with gate SiOx stoichiometry, x = 1.78 and bias temperature stress (BTS), x = 1.78 and BCO, and x = 1.9 and BCO. The temperature of annealing in the N2 atmosphere was 200 °C. (c) Band diagram of back-channel oxidized MNOS TFT. The red arrows show the electric dipoles at the SiOX/a-Si:H and a-Si:H/BCO SiOX interfaces.

A schematic band model for the MNOS TFT with the BCO treatment and the sectional structure of the interface between the a-Si:H and gate and BCO SiOx are shown in Fig. 8c. The uniformly high Vth that is independent of SiOx thickness is due to the dipoles generated at the channel and back-channel interfaces between a-Si:H and SiOx8 of reference

By continuing to use AliExpress you accept our use of cookies (view more on our Privacy Policy). You can adjust your Cookie Preferences at the bottom of this page.

This website is using a security service to protect itself from online attacks. The action you just performed triggered the security solution. There are several actions that could trigger this block including submitting a certain word or phrase, a SQL command or malformed data.

Chances are, you are reading these words on a smartphone or computer screen. For around the last 10 years, these types of screens have been based on a display technology composed of so-called thin film transistors. These are inorganic transistors which require very little power, and they have proven themselves very capable, given their widespread adoption—but they have some limits which researchers have been busy trying to overcome.

"We explore new ways to improve upon thin film transistors, such as new designs or new methods of manufacture," said Gyo Kitahara, a PhD student from the Department of Applied Physics. "Organic thin film transistors, for example, have a bright future in LCD screen devices. Compared to the inorganic kind currently used, we expect the organic kind to be useful in low-cost, large-area, lightweight and wearable electronic products, especially by using printing-based production technologies."

The idea of organic thin film transistors itself is not new, but the ability to print such devices, which would allow for a design revolution, has eluded industry and academics, until now. Professor Tatsuo Hasegawa of the Department of Applied Physics, Kitahara, and their team came up with a way to print organic semiconductor films, the basis of these transistors, on a special surface that is highly solution-repellent, or lyophobic. This means ordinarily the surface would repel the materials required to print the structure of the transistor, which seems counterintuitive as to why such a surface would be useful at all. But lyophobic surfaces are responsible for creating transistor structures that are finely tuned for high performance. So how did the researchers overcome their repellent nature?

"We made use of a fluidic property you probably see every time you wash your hands with soap," said Kitahara. "Soap bubbles can hold a shape by lowering the surface tension of liquid. We presume that the soap-film mechanism should be effective for formation of a thin liquid layer on lyophobic surfaces in spite of the repellent forces. Solid semiconductor films can be formed and grown via the formation of thin liquid layers during the printing processes."

With this hurdle of how to print organic transistors overcome, other researchers can build on the team"s findings and find ways to scale this method up. With a proliferation of large, flexible, or wearable devices, Hasegawa"s team dreams of seeing a convergence between the real world and virtual world in ways we"ve never seen before.

"After having experimented by trial and error, we eventually found that the use of a special U-shaped metal-film pattern seems to be effective for uniform film growth thanks to the way it creates a thin liquid layer on lyophobic surfaces," said Kitahara. "We anticipated the results beforehand to some extent, but the success of these findings was finally demonstrated and obtained after overcoming several difficulties, which brought great pleasure and happiness to me."

If you ended up on this page doing normal allowed operations, please contact our support at support@mdpi.com. Please include what you were doing when this page came up and the Ray ID & Your IP found at the

Many Apple products use liquid crystal displays (LCD). LCD technology uses rows and columns of addressable points (pixels) that render text and images on the screen. Each pixel has three separate subpixels—red, green and blue—that allow an image to render in full color. Each subpixel has a corresponding transistor responsible for turning that subpixel on and off.

Depending on the display size, there can be thousands or millions of subpixels on the LCD panel. For example, the LCD panel used in the iMac (Retina 5K, 27-inch, 2019) has a display resolution of 5120 x 2880, which means there are over 14.7 million pixels. Each pixel is made up of a red, a green, and a blue subpixel, resulting in over 44 million individual picture elements on the 27-inch display. Occasionally, a transistor may not work perfectly, which results in the affected subpixel remaining off (dark) or on (bright). With the millions of subpixels on a display, it is possible to have a low number of such transistors on an LCD. In some cases a small piece of dust or other foreign material may appear to be a pixel anomaly. Apple strives to use the highest quality LCD panels in its products, however pixel anomalies can occur in a small percentage of panels.

In many cases pixel anomalies are caused by a piece of foreign material that is trapped somewhere in the display or on the front surface of the glass panel. Foreign material is typically irregular in shape and is usually most noticeable when viewed against a white background. Foreign material that is on the front surface of the glass panel can be easily removed using a lint free cloth. Foreign material that is trapped within the screen must be removed by an Apple Authorized Service Provider or Apple Retail Store.

If you are concerned about pixel anomalies on your display, take your Apple product in for closer examination at an Apple Store, Apple Authorized Service Provider, or an Independent Repair Provider. There may be a charge for the evaluation. Genuine Apple parts are also available for out-of-warranty repairs through Self Service Repair.*

Liquid crystal display devices, whether passive or active, customarily embody thin, parallel, spaced glass panels with an intermediate liquid crystal layer.

Initially, soda lime glass panels were used in producing passive LCD devices. It was observed that, when such panels were employed, degradation of the liquid crystal occurred at normal operating temperatures. This was due to sodium ion migration to the glass surface, and an exchange of sodium for hydrogen ions in water contaminating the liquid crystal. To avoid this, it has been proposed to apply a silica film to the surface of the glass panel. This film acts as a barrier layer to stop sodium ion migration from the glass, and thus prevent exposure of the liquid crystal layer to the sodium ions.

Another approach to controlling sodium has been to use a BaO—Al2O3—B2O3—SiO2 glass available from Corning Incorporated as Code 7059. This glass is nominally free of alkali metal oxides. This means that the glass has no intentionally added alkali metal compound in its batch, but may contain up to about 0.1% Na+ as an impurity. Use of this glass avoids contamination of the liquid crystal.

In the active device, the back panel, or active plane, has thin film transistors formed on the glass by photolithographic steps, together with attached circuitry. The front panel, or color plane, has transparent colored dots or stripes in the case of a full color display. Combined with the inverted design of thin film transistors, Code 7059 glass also provides sufficient protection for the active elements in an active matrix LCD device while the amorphous silicon transistors are being fabricated on the glass at temperatures under 400° C. Sodium contamination would lead to transistor instability over time.

However, use of polysilicon thin film transistors is becoming increasing popular for active matrix LCDs. This practice involves processing temperatures that are substantially higher than the temperatures required for the amorphous silicon, and that approach the strain point of the glass. At these temperatures, sodium, which is present as an impurity, begins to create a problem again. As a result, it again becomes necessary to provide a barrier layer on the glass panel to prevent migration.

Fabrication of the active plane, or active matrix, involves the use of multiple photolithographic steps which require precise alignment. This requires that the panels not only have precise dimensions as formed, but that such precise dimensions be retained during subsequent processing steps. However, these processing steps may involve thermal exposure at or near temperatures where a glass may undergo structural rearrangement and/or dimensional relaxation. Accordingly, it has become common practice to subject glass panels to a compaction process after formation and before further thermal processing.

Compaction involves reheating a glass body to a temperature below the glass softening point, but equal to or above the maximum temperature reached in a subsequent processing step. This achieves structural rearrangement and dimensional relaxation in the glass prior to, rather than during, the subsequent processing. Preliminary compaction is imperative where it is necessary to maintain precise alignment and/or flatness in a glass body during subsequent photolithographic processing, as in the manufacture of flat panel display devices.

It is economically attractive to compact glass sheets in stacks. However, this necessitates interleaving, or separating, adjacent sheets with a release material to avoid sticking. At the same time, it is necessary to maintain the sheets extremely flat, and with an optical-quality surface finish.

The panels used in an LCD device must, of course, be of optical quality. Strict cleanliness is a requirement during all processing. Any marring of the surface, such as surface scratches, indentations, or the like, must be avoided.

Currently, sheets of graphite are inserted between glass panels to serve as a parting agent during the compaction process. They must be removed at completion of the process. This is not only an added step, but on occasion leads to scratches that must be removed by polishing.

It has been proposed in U.S. Pat. No. 5,073,181 (Foster et al.) to substitute a monolayer of submicron silica particles as a parting layer. However, this is also a non-permanent layer that must be removed before further processing. Hence, it could not function as a barrier layer to sodium migration.

It would, therefore, be desirable to apply a permanent surface film on at least one side of a glass panel during formation of the panel, or prior to further processing. This film would have to remain on the panel and not interfere with processing or operation of an LCD display, either passive or active. The film should be inert, transparent and refractory. It should serve as a parting agent to prevent glass adhesion during compaction, and also as a barrier layer to prevent sodium migration which would result in liquid crystal, or thin film transistor, degradation. Finally, it should improve the scratch resistance of the surface. It is a basic purpose of the present invention to provide a method of producing a glass panel for an LCD device that has such features.

My invention resides in a method of producing a glass panel for a LCD device wherein the glass is nominally alkali-free, that is, may have an alkali metal content no greater than about 0.1% by weight, and wherein the method comprises depositing on at least one surface of a clean panel a continuous, permanent, transparent, barrier layer film from an atmosphere of an atomized, or ionized, inert refractory material, or reactive precursor, the film being greater than 50 nm, but not over 500 nm, in thickness, and, after depositing the transparent film on the clean glass panel, stacking a plurality of the clean glass panels to form a stack of adjacent panels, the total film thickness between each pair of adjacent panels in the stack being greater than loonm and subjecting the stack to a heat treatment to compact the glass, the permanent, barrier layer film on the clean glass panel functioning both as a barrier to sodium ion migration and as a parting agent during the compacting heat treatment.

The invention further resides in a method of compacting a plurality of clean glass panels in a stack wherein the glass is nominally alkali-free, that is, may have an alkali metal content no greater than about 0.1% by weight, and wherein a surface on each glass panel opposes a surface on an adjacent glass panel, the method comprising depositing on at least one surface of each glass panel a continuous, permanent, transparent, barrier layer film from an atmosphere of an atomized, or ionized, inert refractory material, or reactive precursor, the film being greater than 50 nm, but not over 500 nm, in thickness, stacking the filmed panels so that at least one of each pair of adjacent surfaces has a film, and the total film thickness between each pair of adjacent surfaces is greater than 100 nm and subjecting the stack to a compaction thermal cycle, the permanent barrier layer film on the clean glass panel functioning both as a barrier to sodium ion migration and as a parting agent during the compaction thermal cycle.

In preferred embodiments, the inert refractory material deposited is silica, the film is deposited by chemical vapor deposition, preferably while the glass panel is being drawn, and the film is deposited on both sides of the panel.

U.S. Pat. No. 4,485,146 (Mizuhashi et al.) discloses a soda-lime glass substrate that contains 10 to 20% of an alkali component in its composition. The patent teaches that the known silica layer is not usually sufficient as a barrier layer. In lieu thereof, the patent teaches a silica layer in which hydrogen is bonded to silicon in an amount up to 25 molar %.

U.K. Application No. 2,144,733A (Kawahara et al.) teaches a silica barrier layer film to prevent sodium migration. A glass sheet is dipped in an aqueous solution of H2SiF6 that is saturated with silica and has boric acid added. A thin preliminary layer of silica can be applied by vacuum deposition or sputtering.

U.K. Application No. 2,163,146A (Porter) teaches producing a barrier layer of silica up to 50 nm thick by pyrolyzing a silane gas on a glass surface at a temperature above 600° C. in the presence of a gaseous electron donating compound.

U.S. Pat. Nos. 4,828,880 and 4,995,893 (Jenkins et al.) teach a modification of the Porter method wherein a gaseous mixture of a silane, an unsaturated hydrocarbon and carbon dioxide is pyrolyzed on a glass surface at a temperature of 600-750° C.

U.S. Pat. No. 3,208,839 (Nordberg) teaches a method of reshaping a glass body wherein adherence of the glass to the reshaping means is prevented by applying a thin, continuous, uniform film of colloidal, refractory metal oxide to the glass and baking to resist mechanical removal. The patent is not concerned with alkali migration and hence provides no disclosure relevant thereto.

An article in IEEE ELECTRON DEVICE LETTERS, Vol. EDL-7, No. 11, November, 1986 by J. R. Troxell et al. describes a new technology for forming polycrystalline silicon thin-film transistors on a nominally alkali-free alkaline earth aluminosilicate glass. The glass was one disclosed in U.S. Pat. No. 4,180,618 (Alpha et al.). A silicon nitride barrier layer film was applied to the glass, with a silica buffer layer being subsequently applied to maintain electrical isolation between transistor devices.

FIG. 1 of the attached drawing is a side elevational view of an individual glass panel 10 having a deposited film 12 applied over both upper surface 14 and lower surface 16. It will be understood that panel 10 could as well have film 12 deposited on only one surface if the film is of sufficient thickness. A panel coated on both surfaces is generally preferred.

FIG. 2 is a side elevational view of a stack 20 which is composed of three glass panels 10 stacked between two high-temperature stacking pads 24. Glass panels 10 are coated on both sides, as shown in FIG. 1.

If single-side coated panels are used, care must be taken in stacking to insure that a film 12 is present at each interface. The third panel, either bottom or top, must have a film on both surfaces to avoid sticking to the stacking pad 24. Alternatively, it would be necessary to provide a film on the stacking pad, or make the stacking pad from a refractory material such as fused silica.

The term “nominally free of alkali metal oxides”, as used herein, means a glass that has no intentionally added alkali metal compound in its batch, but may contain up to about 0.1% Na+ as an impurity. As noted earlier, barrier layer films were employed on soda lime glass panels for LCD devices to minimize sodium ion migration. The advent of nominally alkali-free glasses presumably dispensed with such need.

With the use of higher temperature processing for AMLCD devices, the need for a barrier layer film again arose, even for nominally alkali-free glasses. The present invention addresses that need.

I have now found that, under certain conditions, inert, refractory oxide films can perform the dual functions of a barrier layer and a parting agent. Thus, a properly deposited film can initially function as a parting agent to prevent glass sticking in a compaction process. Subsequently, the film further functions as a barrier layer to prevent alkali migration during subsequent production steps and during operation of the LCD.

The film provides its greatest value if applied during drawing of glass panels in sheet form, or immediately thereafter. A continuously drawn sheet may be coated as it leaves the sheet forming member. Alternatively, the continuous sheet may be severed into individual sheets. These may then be suspended and carried through a coating apparatus. In either case, sides of the sheet may be simultaneously coated, or the coating may be applied to only one side if desired

Currently, sheets for active matrix LCD use are drawn by a downflow method. In this method, streams of molten glass overflow from a reservoir, flow down the converging sides of a sheet forming member, and join to form a single sheet as they leave the member. The method and apparatus have been fully described in United States Patents. These include U.S. Pat. No. 3,149,949 (Dockerty et al.) and U.S. Pat. Nos. 3,338,696 and 3,682,609 (Dockerty).

By using an immediate coating procedure, there is less tendency for dust, glass chips and similar debris to adhere to the film. To the extent that contamination does occur, it is more easily and safely cleaned. Chemical durability of the film is also important since the film may be exposed to harsh chemical environments in subsequent processing. The film is generally more resistant to attack than the unprotected glass.

A particular benefit is the fact that the film has no detrimental effect in the completed display device. Hence, not only does it offer continuous protection, but there is no need for a removal step. This minimizes handling by eliminating the step of removing sheets or particles of parting agent. It thereby minimizes possible surface scratches. The hard, refractory nature of the film also resists some surface marring that otherwise might inadvertently occur.

The deposited film may be composed of any inert, refractory material or combination of materials. The term “inert” indicates no chemical reaction with the glass during deposition, or in subsequent operations, other than the formation of chemical bonds at a surface, such as 14. It also indicates a general lack of chemical attack by or on materials used in the device, or in its production. The term “refractory” signifies a material that undergoes no appreciable chemical or physical change at the temperatures encountered in the compaction process. This process employs temperatures close to the glass strain point, for example, a temperature of 580° C. for one hour when Code 7059 glass is compacted.

Refractory materials suitable for barrier layer use include silica, alumina, silicon nitride, titania, tantala and tin oxide. The latter three oxides are less desirable because they have high refractive indices. Application of such an oxide on the outer surface of a glass sheet leads to high reflectivity, a condition not desirable in a display device.

Silicon nitride has been proposed as a barrier to sodium migration. However, a silicon nitride film tends to be electrically conductive when ion implanted, whereby current leakage through the film, or between polysilicon transistor devices, can occur. Therefore, a silicon nitride film can not be used alone where electrical isolation is required. Rather, it must be used in conjunction with an electrically insulating film such as silica.

Further, silicon nitride is difficult to deposit by atmospheric pressure chemical vapor deposition (APCVD) during the glass drawing process. Both alumina and silica can be deposited by APCVD. In general, I prefer a silica film both because of ease of deposition and because of its excellent compatibility with thin film transistors.

The film must be deposited from an atmosphere containing atomic sized species, that is individual atoms or ions, rather than particles of larger size. Accordingly, physical vapor deposition, such as sputtering, or electron beam evaporation, or chemical vapor deposition are preferred processes. The latter (CVD) is favored for coating a sheet as it is drawn. Films formed from atomic sized species tend to be more compact, and hence better alkali diffusion barriers. Also, being more dense, they are more resistant to being marred and attacked chemically.

Film thickness may vary from 50 to 500 nm. Thicker films require longer application times, and hence are more expensive to produce. Therefore, I prefer films not over about 100 nm thick.

However, such thin films may have some tendency to stick during compaction unless coated on both sides of the glass so that filmed surfaces face each other in a stack of panels. When the glass is coated as it is being drawn, or is suspended for coating, such double side coating occurs inherently. In any event, the total of the film thicknesses between adjacent glass surfaces must be greater than 100nm to insure against sticking.

An initial survey was made by preparing a stack of glass test pieces, each piece being one inch (2.5 cm) on a side and 1.2 mm thick. The glass employed was Code 7059 glass. In the stack, some uncoated samples were arranged to interface with each other. Others were arranged to interface with four different test pieces, each having a different protective film. All samples were thoroughly cleaned.

1. A 60 nm thick titania film was deposited from an atmosphere created by pyrolyzing a mixture of TiCl4 and O2 in a chamber with the glass at a temperature of 320° C.

4. A 400 nm thick tin oxide film was deposited by chemical vapor deposition from an atmosphere of tetramethyl tin and oxygen with the glass at 525° C.

The arrangement of cleaned test pieces in the stack, excluding top and bottom, heat resistant, stacking pads, is shown in TABLE I. Coated test pieces of Samples 1-4 were arranged so that the film coated sides were adjacent to each other.

This test stack was subjected to a time-temperature cycle somewhat more severe than the commercial compaction schedule for Code 7059 glass to provide a margin of safety. The schedule was 675° C. for ninety minutes. When the stack was cooled and disassembled, it was found that all uncoated glass interfaces adhered to each other. None of the film interfaces showed any adhesion, except the TiO2-coated one in a limited area.

In a further test, RF magnetron sputtering from a rectangular alumina target was employed. This deposited a 100 nm thick alumina film on each side of 1″×3″ (2.5×7.6 cm), Code 7059 glass substrates that were 1.2 mm thick. 1″×1″ (2.5 cm×2.5 cm) test pieces were cut and thoroughly cleaned. Uncoated pieces of Code 7059 glass of the same size were cut and thoroughly cleaned. The glass test pieces were arranged in stacks as shown in TABLE II.

The stack were then subjected to simulated compaction cycles. Two temperatures were used, 600°, approximating the recommended one, the other 60° C. higher. Similarly, two pressures of 54 and 1150 g/in2 (g/6.5 cm2), as applied to the top of a stack, were used. Times varied from 1.5 to 3.3 hours.

When the stacks were cooled and disassembled, it was observed that no adhesion occurred at the Al2O3/Al2O3 interfaces. Examination at 50X under an optical microscope revealed no damage to the surfaces. However, all of the uncoated interfaces fused together, some quite extensively. The Al2O3/glass interfaces showed a slight degree of adhesion. This indicated that a single layer of 100 nm thick Al2O3 at an interface could not safely be relied on to prevent adhesion.

In a further test, atmospheric pressure chemical vapor deposition (APCVD) of silica from the reaction of silane with oxygen was utilized. Cleaned glass substrates, 25 mm×75 mm×1.2 mm Code 7059, were introduced into a belt furnace where they were heated to 500° C. As the belt passed under the slot coater, the reactants flowed over the hot glass where they mixed and reacted to form a film of silica. Belt speed and reactant flow were adjusted so that a 50 nm thick film was formed on the top side of the glass. The back side of the glass was coated by turning the substrate over and running it through the coating furnace again.

A second set of silica films on Code 7059 glass was prepared by plasma enhanced chemical vapor deposition (PECVD). These films were deposited on one side of the glass to a thickness of approximately 200 nm.

Samples 1″×1 ″ (2.5 cm×2.5 cm) were cut from the above film coated glass, along with samples of uncoated Code 7059 glass. All the samples were thoroughly cleaned and stacked in Class 1000 cleanroom conditions. The samples were arranged in the stack as shown in TABLE III.

The stack was subjected to a temperature of 652° C. for 2 hours in air with a pressure of 1150 g/in2. When the stack had cooled and been disassembled, the following results were found. The APCVD silica films did not adhere together, but they did adhere to the bare Code 7059 glass. The bare Code 7059 glass samples also adhered together.

The PECVD films did not adhere together and also did not adhere to the bare Code 7059 glass. The reason for the sticking of the APCVD silica to bare glass while the PECVD silica did not is taken to be the difference in film thickness. The APCVD film thickness is less than the 100 nm limit pointed out in the example above (TABLE II) while the thickness of the PECVD silica is greater than 100 nm.

The foregoing experiments led to a pilot run on a larger scale. In this run, 320 mm×320 mm×1.1 mm Code 7059 glass panels were provided with 100 nm thick alumina films on both sides of the panel by electron beam evaporation. Two stacks of ten panels each were assembled, after cleaning, and placed between temperature resistant support plates. The stacks were heat treated at 580° C. for one hour in a lehr. The panels in one stack were all coated. Those in the other stack were arranged as shown in TABLE IV.

Each stack was cooled and disassembled. The second stack exhibited no adhesion at the Al2O3/A2O3 interfaces; some adhesion at some Al2O3/glass interfaces; complete adhesion at uncoated/uncoated interfaces.

In the other stack, adhesion occurred in spite of the coatings. When these panels were separated and examined, two types of defects were observed where adhesion had occurred. One type of defect appeared as a relatively large blob of foreign material on the order of 525×75 microns. The other type was a small particle of about 15 microns diameter embedded in the surface.

It is my belief that the defects observed resulted from erratic or uneven evaporation of the material, and that the results should be disregarded. The results do suggest that electron beam evaporation must be closely monitored if used as a means of depositing a protective film.

It is necessary to employ standard cleanroom conditions. Thus, all particles must be eliminated from the coated glass surfaces to prevent sticking or surface marring. Also, dust must be excluded from the atmosphere of the locale where stack assembly takes place.

The invention has been described with respect to protection of Code 7059 glass sheets. However, it will be readily apparent that the invention is equally applicable to protection of other glasses that are essentially alkali-free, but may contain sodium as an impurity in amounts up to about 0.1% of the glass composition. Examples of such glasses, having particular utility because of their relatively high strain points, are those disclosed in U.S. Pat. Nos. 5, 116,787 and 5,116,789 (Dumbaugh, Jr. et al.).

Let us start with the basics first; refresh the knowledge about TN and LCD displays in general, later we will talk about TFTs (Thin Film Transistors), how they differ from regular monochrome LCD displays. Then we will go on to the ghosting effect, so we will not only discuss the technology behind the construction of the TFT, but also some phenomena, like the ghosting effect, or grayscale inversion, that are important to understand when using an LCD TFT display.

Next, we will look at different technologies of the TFT LCD displays like TN, IPS, VA, and of course about transmissive and transflective LCD displays, because TFT displays also can be transmissive and transflective. In the last part we will talk about backlight.

Let us start with a short review of the most basic liquid crystal cell, which is the TN (twisted nematic) display. On the picture above, we can see that the light can be transmit through the cell or blocked by the liquid crystal cell using voltage. If you want to learn more about monochrome LCD displays and the basics of LCD displays, follow this link.

What is a TFT LCD display and how it is different from a monochrome LCD display? TFT is called an active display. Active, means we have one or more transistors in every cell, in every pixel and in every subpixel. TFT stands for Thin Film Transistor, transistors that are very small and very thin and are built into the pixel, so they are not somewhere outside in a controller, but they are in the pixel itself. For example, in a 55-inch TV set, the TFT display contains millions of transistors in the pixels. We do not see them, because they are very small and hidden, if we zoom in, however, we can see them in every corner of each pixel, like on the picture below.

On the picture above we can see subpixels, that are basic RGB (Red, Green, Blue) colors and a black part, with the transistors and electronic circuits. We just need to know that we have pixels, and subpixels, and each subpixel has transistors. This makes the display active, and thus is called the TFT display. TFT displays are usually color displays, but there are also monochrome TFT displays, that are active, and have transistors, but have no colors. The colors in the TFT LCD display are typically added by color filters on each subpixel. Usually the filters are RGB, but we also have RGBW (Red, Green, Blue, White) LCD displays with added subpixels without the filter (White) to make the display brighter.

What is interesting, the white part of the RGB and RGBW screen will look exactly the same from a distance, because the lights are mixed and generate white light, but when we come closer to the screen, we will not see white light at all.

Going a little bit deeper, into the TFT cell, there is a part inside well known to us from the monochrome LCD display Riverdi University lecture. We have a cell, liquid crystal, polarizers, an ITO (Indium Tin Oxide) layer for the electrodes, and additionally an electronic circuit. Usually, the electronic circuit consists of one transistor and some capacitors to sustain the pixel state when we switch the pixel OFF and ON. In a TFT LCD display the pixels are much more complicated because apart from building the liquid crystal part, we also need to build an electronic part.

That is why TFT LCD display technologies are very expensive to manufacture. If you are familiar with electronics, you know that the transistor is a kind of switch, and it allows us to switch the pixel ON and OFF. Because it is built into the pixel itself, it can be done very quickly and be very well controlled. We can control the exact state of every pixel not only the ON and OFF states, but also all the states in between. We can switch the light of the cells ON and OFF in several steps. Usually for TFT LCD displays it will be 8-bit steps per color, so we have 256 steps of brightness for every color, and every subpixel. Because we have three subpixels, we have a 24-bit color range, that means over 16 million combinations, we can, at least theoretically, show on our TFT LCD display over 16 million distinct colors using RGB pixels.

Now that we know how the TFT LCD display works, we can now learn some practical things one of which is LCD TFT ghosting. We know how the image is created, but what happens when we have the image on the screen for a prolonged time, and how to prevent it. In LCD displays we have something called LCD ghosting. We do not see it very often, but in some displays this phenomenon still exists.

If some elements of the picture i.e., your company logo is in the same place of the screen for a long period of time, for couple of weeks, months or a year, the crystals will memorize the state and later, when we change the image, we may see some ghosting of those elements. It really depends on many conditions like temperature and even the screen image that we display on the screen for longer periods of time. When you build your application, you can use some techniques to avoid it, like very rapid contrast change and of course to avoid the positioning the same image in the same position for a longer time.

You may have seen this phenomenon already as it is common in every display technology, and even companies like Apple put information on their websites, that users may encounter this phenomenon and how to fix it. It is called image ghosting or image persistence, and even Retina displays are not free of it.

Another issue present in TFT displays, especially TN LCD displays, is grayscale inversion. This is a phenomenon that changes the colors of the screen according to the viewing angle, and it is only one-sided. When buying a TFT LCD display, first we need to check what kind of technology it is. If it is an IPS display, like the Riverdi IPS display line, then we do not need to worry about the

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey