igzo tft display quotation

A driving method of pixel circuit using amorphous indium gallium zinc oxide (a-IGZO) thin-film transistor (TFT) is proposed to improve the image quality of active matrix light-emitting diode displays. The proposed pixel circuit employs a diode-connected structure to compensate for variation in threshold voltage (Vth) of the a-IGZO TFT. In addition, the proposed driving method adopts negative bias annealing to suppress the Vth shift. The annealing time is optimized based on the experimental observation of the minimum Vth shift. After a stress time of 30000 s, the measurement results show that the Vth shift is reduced by 29.6%, using an optimized annealing time of 5% of one frame time. In addition, the maximum deviation in the emission current using the proposed driving method was measured to be less than 4.32% after a stress time of 30 000 s.

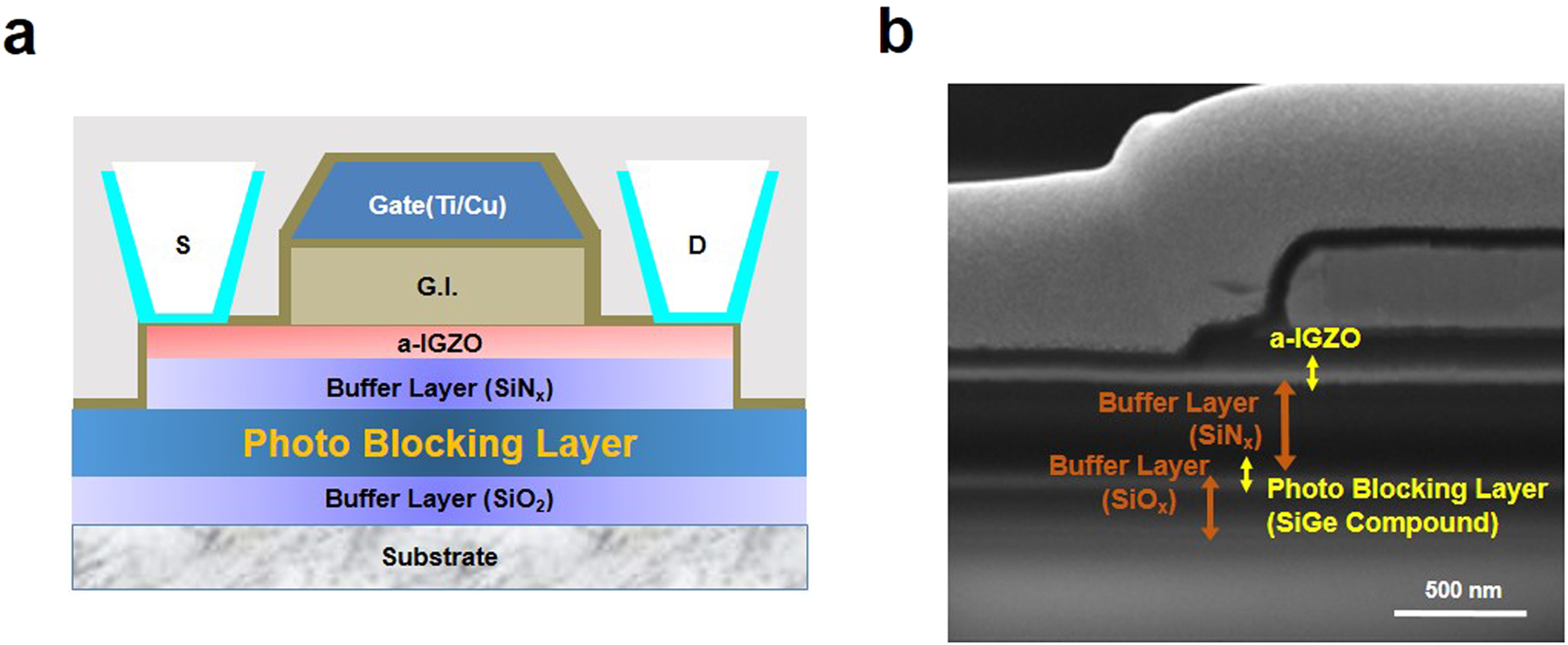

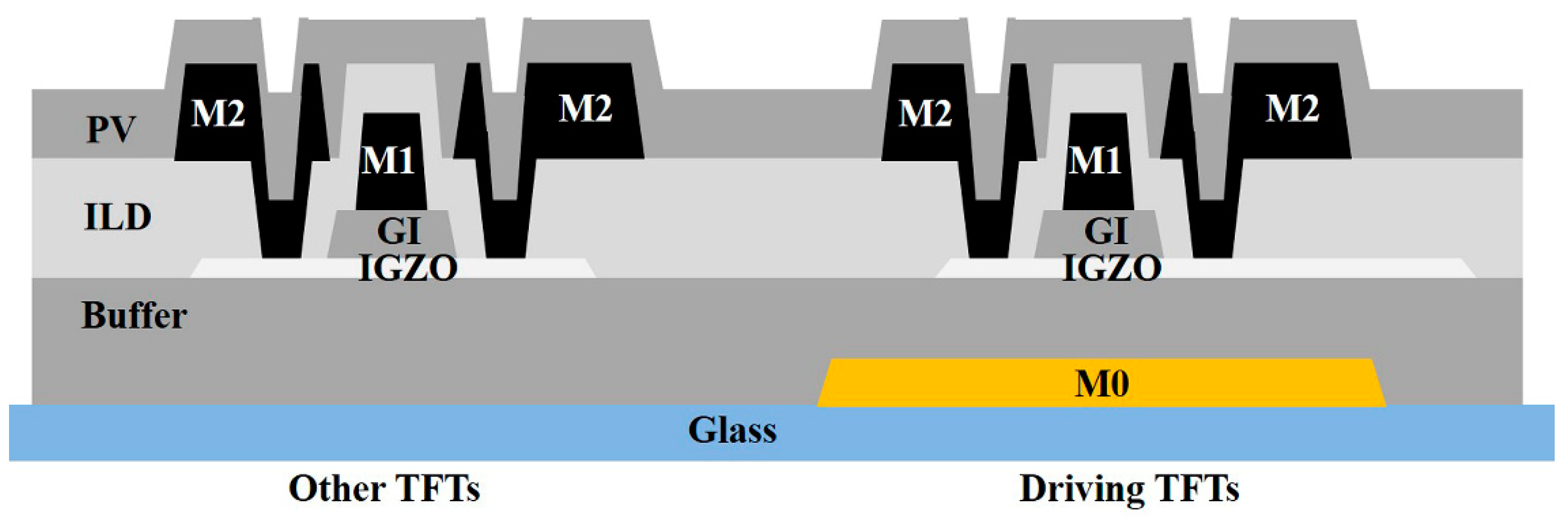

a-IGZO-based TFT fabricated via CL-ES process shows the same mask number to that of BCE process (Fig. 1). Compared with a-IGZO-based TFT with BCE structure, a-IGZO-based TFT with CL-ES structure shows two advantages: (1) a-IGZO-based backplane produced using CL-ES process deposits gate insulator, a-IGZO nano-layer, and ES nano-layer sequentially, then forms a ESL nano-mask through dry-etch method. This newly formed ESL nano-mask with 100 nm can prevent the exposure of a-IGZO nano-film to etchant, stripper, or photoresist. Therefore, the contamination at inter-layer interfaces is effectively prevented [25]. (2) At the same time, a-IGZO nano-film is not protected by ES layer but bombarded by CF4 plasma during the ESL nano-mask formation, thus becomes a conductor. This naturally forms the Ohmic contact between S/D electrode of following process and a-IGZO semiconductor. For another part, a simultaneous etching of S/D and a-IGZO nano-layer can be one overlay allowance of ESL-(a-IGZO+S/D metallization) layer, which could decrease the two overlay process error of the a-IGZO-ESL and ES-S/D metallization layer in the conventional ESL process (Fig. 2). The overlay number of the a-IGZO, ES, and S/D layer is reduced, which resulted in the decrease in the size of TFT device that lowered the parasitic capacitance. The outcome planar structure is similar to the BCE structure (Fig. 3a, b).

(Color online) Schematics of simultaneous formation method for TFT channel and S/D electrode in CL-ES process. a The first step that forms gate electrode. b The second step that forms etch-stopper layer. c The third step that forms S/D photo pattern. d The fourth step that forms S/D electrode and active pattern

Figure 3 shows the SEM images of a-IGZO-based TFTs with CL-ES structure (Fig. 3a, c) and BCE structure (Fig. 3b, d). From the top view, it is difficult to identify the differences between CL-ES structure and BCE structure (Fig. 3a, b). From the side view, an ES nano-layer can be found between the a-IGZO nano-layer and the S/D electrode layer in CL-ES structure (Fig. 3c). Meanwhile, a passivation layer can be found on the top of a-IGZO nano-layer in BCE structure (Fig. 3d). In the presented CL-ES process, an a-IGZO nano-layer with a thickness of 30 nm is deposited. Moreover, the damage during wet etching is negligible. For BCE process, a 70-nm a-IGZO nano-layer is deposited, as a-IGZO layer needs compensation for etching loss. The difference between the thicknesses of a-IGZO nano-layers in CL-ES and BCE structures can be observed in the SEM images (Fig. 3c, d).

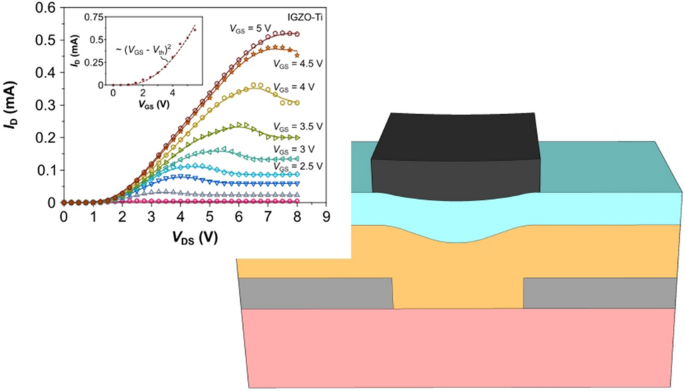

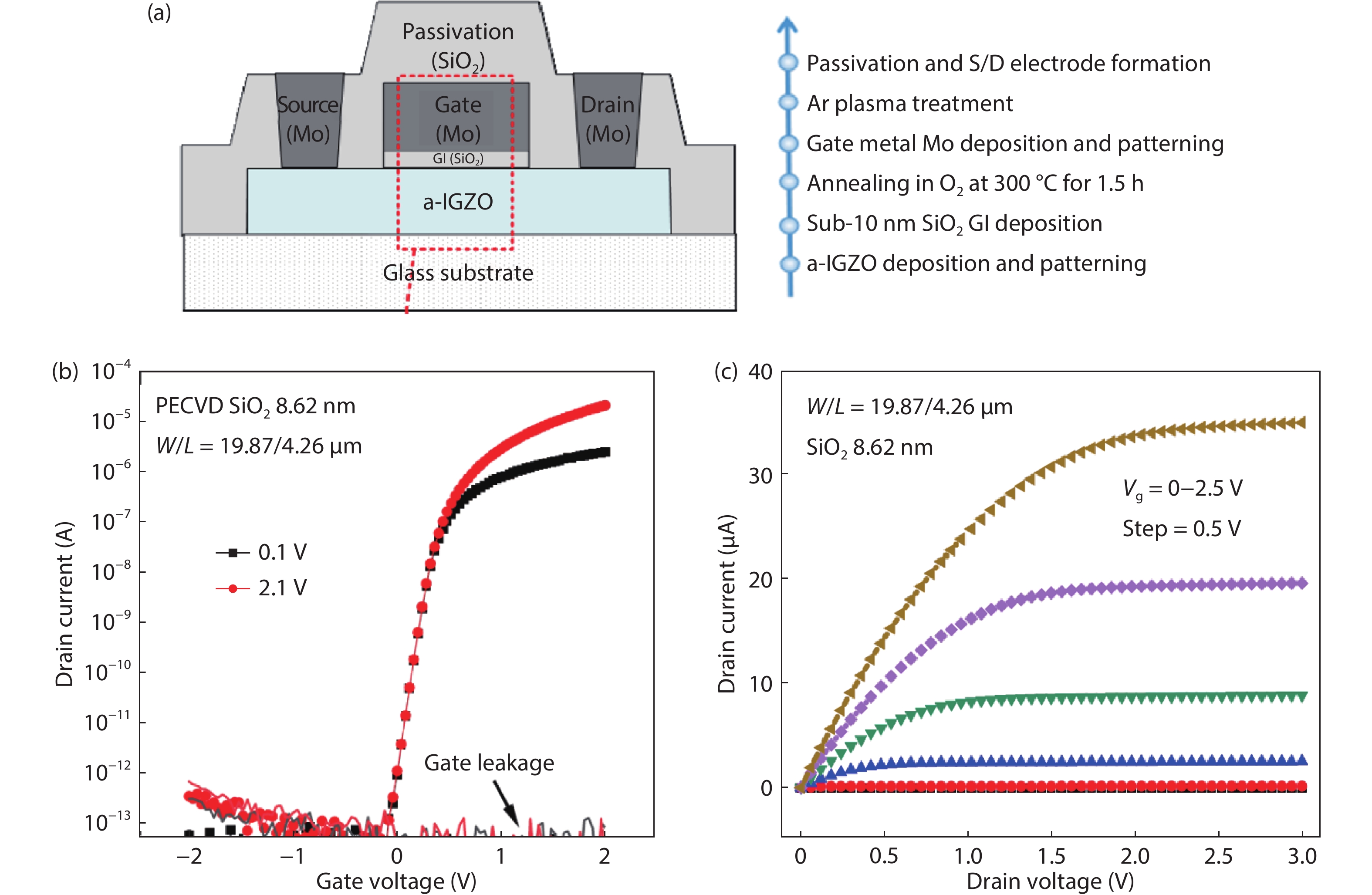

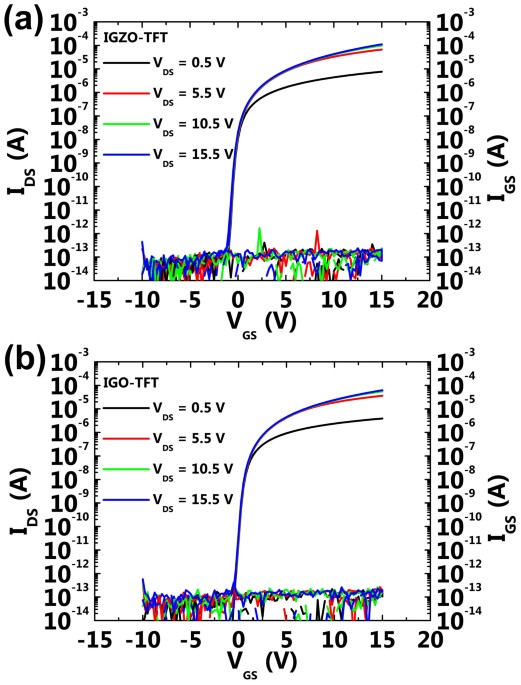

The I-V characteristics of a-IGZO-based TFT with CL-ES structure and BCE structure are compared (Fig. 4). The saturation electron mobility, threshold voltage, subthreshold voltage swing (SS) value, and more characteristic values are summarized in Table 1. Note that the values summarized in Table 1 are the average number derived from the center and edge of an 8.5 generation glass substrate. The a-IGZO-based TFT with CL-ES structure realizes Vth of − 0.8 V, SS value of 0.18 V/dec, and saturation electron mobility of 8.05 cm2/V s. In the a-IGZO-based TFT with BCE structure, the corresponding results are Vth of + 0.5 V, SS value of 0.77 V/dec, and saturation electron mobility of 6.03 cm2/V s. Compared to the BCE structure, CL-ES structure shows an improved device performances. However, the on-current characteristic of the a-IGZO-based TFT device with CL-ES structure is lower than that with BCE-structured device. This is due to the fact that TFT channel structures are different in CL-ES and BCE structures. Generally, BCE-structured TFT channel length are the distance between S/D metal electrodes, and the measured channel length in this study is 5 um [21]. In CL-ES structure, electrodes are in contact with the a-IGZO nano-film that is stretched at the side of ESL nano-mask. Therefore, the channel length is decided by the distance between the a-IGZOs defined at the etch-stopper’s sides, but not determined by the distance between the electrodes. The channel length of the present CL-ES-structure device is measured to be 10 um.

(Color online) Comparison of I-V characteristic of a-IGZO TFTs with CL-ES and BCE structure on the center (a) and edge (b) of 8.5 generation glass substrate

As shown in Table 1, the measured values of Ion/Ioff ratio (~ 106, see Table 1) are approximately 10 times smaller than the typical value (> 107) of a-IGZO-based TFTs. This is because the measuring equipment used here is for the 8.5 generation mass production. Long cables are necessary for these measurements, as the size of the industrial equipment is large. The long cables resulted in an increased measurement noise. In the following reliability testing, smaller-scale measuring equipment is utilized, and the individual TFT devices is used as specimen for measurement. In this way, the measured Ion/Ioff ratios are all upper 107 (see below).

CL-ES process is carefully designed to prevent a-IGZO channel layer being exposed to etchant, photoresist, or stripper. During the process that produces CL-ES process, gate insulator, a-IGZO nano-layer, and ES nano-layer, each inter-layer interface is in contact with only DI water for cleaning purpose. Hence, the chemical contamination is negligible in insulator layer and a-IGZO nano-layer [25, 26]. However, the BCE process not only exposes channel layer to the chemicals but also involves Cu ion diffusion contamination, as the a-IGZO channel is directly exposed to Cu metal. This is also avoided in device with CL-ES structure. The channel region of the a-IGZO nano-film is well protected by ESL nano-mask. The low chemical contamination in CL-ES process may lead to a low carrier trap density at the interface between a-IGZO nano-layer and insulator layer, resulting in an excellent SS value. This low chemical contamination of a-IGZO-based TFT device via CL-ES process also helps improve the uniformity and reproducibility of a-IGZO TFT, which are highly important in industrial production [27, 28].

Figure 5 shows the measured I-V characteristic of TFTs with CL-ES structure and BCE structure derived from 42 measuring points on an 8.5 generation substrate. a-IGZO-based TFT with CL-ES structure has a Vth range of 0.72 V, while that of BCE-structured device is 2.14 V (Table 1). In other words, the uniformity of device performance is significantly improved by CL-ES structure.

(Color online) a CL-ES structure. b BCE structure’s TFTs I-V transfer characteristic. c 42 measuring points. d the photo of TFT. All measured on an 8.5 generation substrate

Figure 6a, b show the I-V characteristic shift of CL-ES-structured device and BCE-structured device obtained in NBTIS testing, respectively. The NBTIS testing results are summarized in Table 2. Under the stress condition described in the Table 2, the Vth shift of CL-ES-structured device and BCE-structured device are − 0.51 and − 3.88 V, respectively. Additionally, the on-current shift, off-current shift, and SS value variance of the CL-ES-structured device are all lower than those of the BCE-structured device (Table 2); this is because a-IGZO-based device with CL-ES-structure can effectively prevent the contamination of a-IGZO and lower carrier trap density of a-IGZO TFT channel. Especially, when looking at the result from first 1000 s of stress, no SS value change is observed in CL-ES-structured device. This phenomenon is comparable to the 0.16 V/dec increase in SS value of BCE-structured device, as it shows that defect sites, which can form carrier traps on the surface of a-IGZO nano-film constituting CL-ES TFT back channel, are not additionally created by electrical and illumination stress. These results fully prove that CL-ES-structured device is much more stable than BCE-structured device. Figure 6c, d show the I-V curve shift of CL-ES- and BCE-structured TFTs obtained from PBTS testing. The detailed PBTS testing results are summarized in Table 3. Both CL-ES-structured TFT and BCE-structured TFT have decreased in ion current during PBTS evaluation. This is caused by the shift in Vth to the positive direction. During PBTS evaluation, residual ion current ratio [(last ion/initial ion) × 100] of the CL-ES-structured TFT with relatively smaller Vth positive shift (+ 1.94 V) is in the level of 88.2%. When compared to the BCE-structured TFT"s residual ion current ratio of 41.3%, CL-ES-structured TFT is significantly superior. This shows the important capacity difference during designing of gate drive on array (GOA) circuit. Different from NBTIS, SS value of CL-ES-structured TFT does not have significant variation ((∆SS 0.06 V/dec), or rather decreases (∆SS − 0.86) like as BCE-structured TFT. This is perhaps due to the carriers, accumulate in the inner space and interface between gate insulator and a-IGZO nano-film by positive gate bias, filling the carrier trap site at the early stage, causing decrease in carrier trap phenomenon. Moreover, the threshold voltage shift phenomenon occurs by carrier charge trapped near the interface between gate insulator and a-IGZO nano-film. Small threshold voltage shift of CL-ES-structured TFT represents that the interface and the inner space of a-IGZO are remarkably clean. In conclusion, PBTS testing also suggests that CL-ES structure and process lead to a better device reliability.

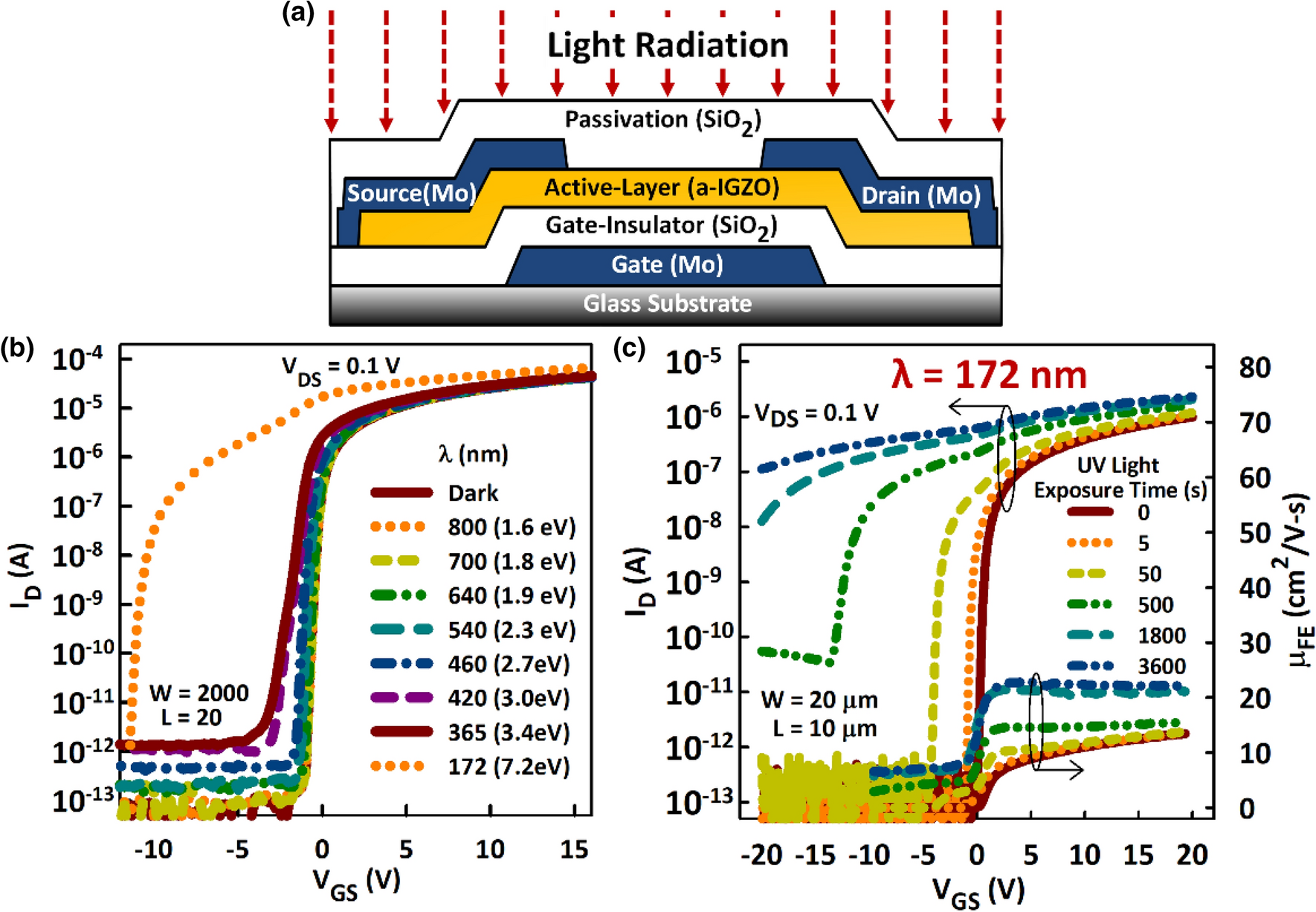

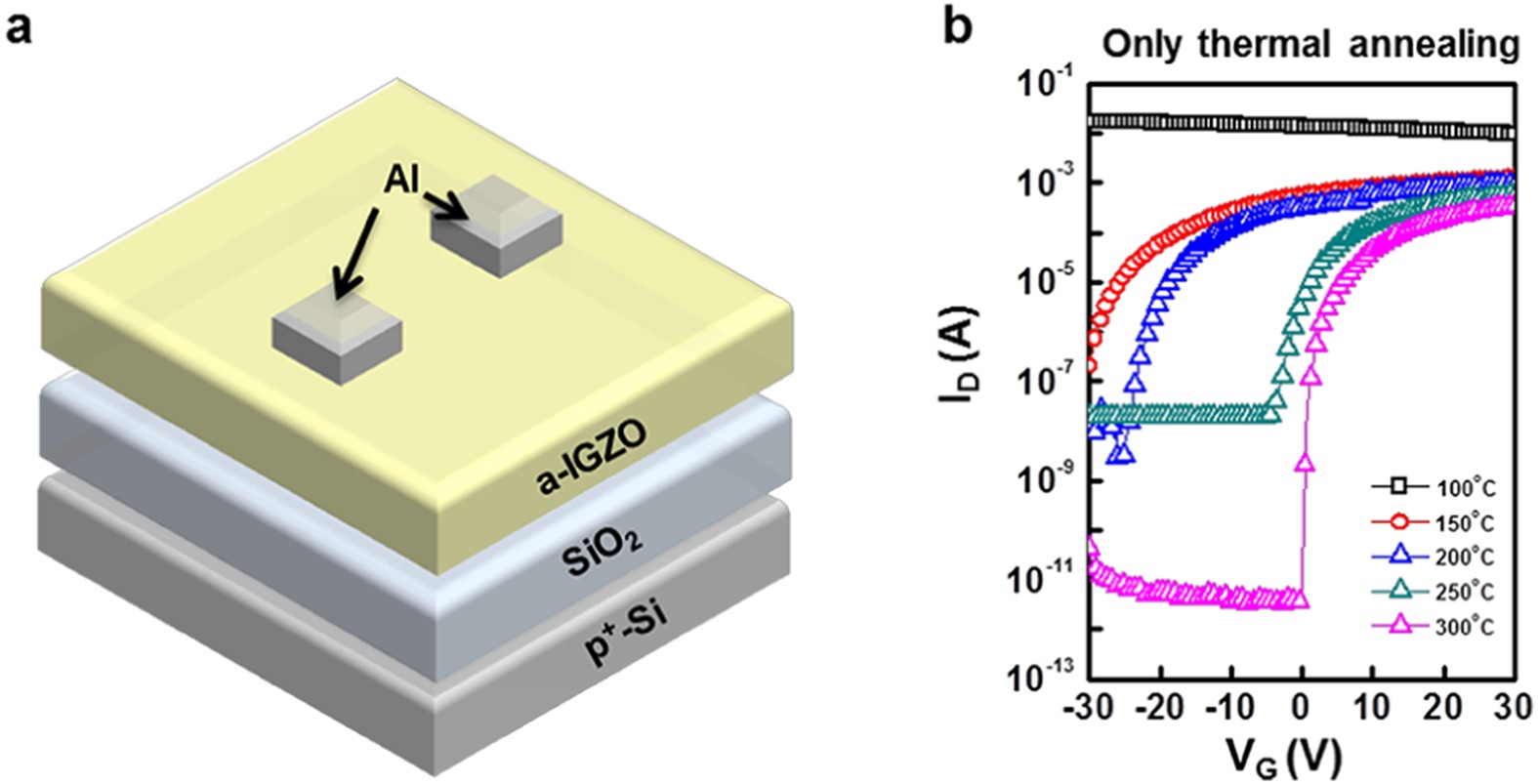

Effect of light radiation. Figure 1b shows the effects of monochromatic light on the performance of the a-IGZO TFTs. The wavelength of the light (λ) is varied from 800 to 172 nm, which corresponds to photon energy of 1.6 to 7.2 in electron volts (eV), and the transfer characteristics are measured after light irradiation for 500 s. Although small, the negative ΔVTH after irradiation with photon energies less than 3.0 eV suggests photoexcitation from sub-gap statesTH is apparent for photon energies in the range of 3.0–3.4 eV and indicates the onset of band-to-band excitation. The photon energy of the deep UV light (~ 7.2 eV) is large enough to induce substantial negative ΔVTH (Fig. 1b). For a clear understanding of the effects of light in the a-IGZO TFTs, we therefore use the deep UV light (λ = 172 nm) in all investigations that follow. The negative ΔVTH induced by deep UV light is accompanied by an increase in SS and the formation of a ‘hump’ in the transfer characteristics, which increases with exposure time (Fig. 1c). Also, quite noticeable is that the µFE doubles after radiating the TFTs with deep UV for 3,600 s, consistent with a photo-induced increase in free carrier concentration.

TFT characteristics used to determine the flat band parameters before and after deep UV light (λ = 172 nm) radiation. (a) Transfer (ID–VGS) characteristics. (b) Capacitance–voltage (C–VGS) characteristics. (c) Extracted surface potential (ψS) as a function of VGS. The flat band voltage (VFB), which is taken as the VGS corresponding to ψS = 0 eV, decreases from 0.36 to − 5.89 V after deep UV radiation.

These photoinduced changes in µFE, SS, nFB, VFB, EF–EC, Nit, and dNgap/dE are all consistent with accumulation/trapping of net positive charge at the gate-insulator/a-IGZO interface and creation of defects in the a-IGZO layer. The increase in SS indicates formation of the defects and given that µFE increased and EF moved closer to EC, some of these defects must be in the bulk of the a-IGZO and donor-like. The defects must also be positively charged (ionized), as the value of Nit changed from a negative to a positive number, making the increase in nFB a sum of band-to-band and sub-gap photoexcitation.

The photoinduced negative ΔVTH is quite repeatable over many samples with varying channel dimensions. In particular, the ΔVTH is independent of L (Supplementary Fig. S1) and rigid such that recovery in the dark is almost negligible at temperatures ≤ 100 °C (Fig. 3). At 150 °C, the transfer characteristics recover slowly and fail to return to the initial state even if the TFTs stay in the dark for a few days (Fig. 3c). Complete recovery is only achievable after annealing at 250 °C in vacuum for two or more hours. Therefore, the ionized donor-like defects generated by light radiation must be metastable states

Recovery of transfer characteristics of a-IGZO TFTs at (a) 100 °C, (b) 130 °C, and (c) 150 °C after deep UV light (λ = 172 nm) radiation for 500 s. Recovery only occurs at temperature > 100 °C. (d) Threshold voltage shift (ΔVTH) as a function of recovery time from the deep UV light radiation stress. (e) Plot of the average time constant (τ) as an inverse function of temperature (Arrhenius plot). The activation energy for the recovery process (Eτ = 0.99 eV) is obtained from the slope of the straight line.

The nature of these defects is investigated by XPS depth profile analysis of thin-film stacks (glass/SiO2/a-IGZO/SiO2) before and after UV exposure (Fig. 4). The O 1 s spectrum is deconvoluted into four energy peaks: O–M, VO, O–H, and Si–O. Peak O–M, which is centered at 529.9 eV, is attributed to O2− ions binding with In, Ga, and Zn atoms—and thus represents the quantity of the oxygen atoms in a fully oxidized stoichiometric environment. Peak O–H is related to metal–OH (hydroxyl) bonds and centered at 532.1, whereas peak Si–O is related to Si–O bonds and centered at 532.4. The VO peak at 531.2 eV stems from the deficiently bonded oxygen in the a-IGZO layer containing nonstoichiometric oxide species, such as In2O3−x, Ga2O3−x, and ZnO1−x, which are associated with VO2.

XPS results showing O 1 s spectra of thin-film stacks (glass/SiO2/a-IGZO/SiO2) before (a–c) and after (d–f) deep UV light exposure at the top surface (a and d), in the bulk (b and e), and at the bottom surface (c and f) of the a-IGZO film. The O 1 s spectrum is deconvoluted into four energy peaks: M–O, VO, O–H, and Si–O. Peak O–M, which is centered at 529.9 eV, is attributed to O2− ions binding with In, Ga, and Zn atoms—and thus represents the quantity of the oxygen atoms in a fully oxidized stoichiometric environment. The VO peak at 531.2 eV stems from the deficiently bonded oxygen in the a-IGZO layer containing nonstoichiometric oxide species, such as In2O3−x, Ga2O3−x, and ZnO1−x, which are associated with VO. Peak O–H is related to metal–OH (hydroxyl) bonds and centered at 532.1 eV, while Peak Si–O is related to Si–O bonds and centered at 532.4 eV.

While the number of Si–O and OH-related defects is negligible in the bulk (Fig. 4b), a significant amount is present at the top (Fig. 4a) and bottom (Fig. 4c) surfaces of the pristine a-IGZO film as expected. The amount of VO is also larger at the surfaces compared to the bulk. Similar situations have been reported before, identifying VO as a surface feature, confined within 0.5 nm of the top surface of the filmO defects in the bulk (Fig. 4e) and at the bottom surface (Fig. 4f) of the a-IGZO, a substantial amount is created at the top surface (Fig. 4d), where the area percentage increases from 10 to 24% (Table 2). The area percentage of the Si–O peak also increases from 15 to 28% at the top surface, indicating the diffusion of Si atoms into the a-IGZO layer, possibly from the broken weak Si–O bonds at the top interface. It should be pointed out that a large overlap exists between the energy peaks O–H (532.1 eV) and Si–O (532.4 eV), making it difficult to separate the two. To ensure a reasonable peak ratio, we fixed the full width half-maximum of all components to 1.

The use of optical electron paramagnetic resonance (EPR) experiments has shed light on the nature of VO in ZnO single crystalsO bind two electrons in their electrically neutral state (VO0) but can also exist in a singly ionized (VO+) and doubly ionized (VO2+) state. The increase in the concentration of VO states at the top surface of the a-IGZO film after light radiation indicates photo-creation of the VO. However, this increase is too small to account for ΔVTH > 10 V after light radiation (Fig. 1c). A plausible explanation would be the photoionization of existing and newly created VO0 to VO2+ states—a process which donates two electrons to EC.

Hydrogen also plays a role in the instability of the a-IGZO TFTs. In fact, a high concentration of hydrogen (in the order of 1020 cm−3) has been observed in a-IGZO thin films, without intentional exposure of the films to hydrogen during their depositionO sites in a-IGZO films, forming stable + 1 charge states as donorsC, they will be hard to detect by XPS. However, a significant increase in the amount of hydrogen after UV light radiation is detected by ToF–SIMS depth profiling of the SiO2/IGZO/SiO2 structures used in this study. The increase is mainly confined to the top surface of the a-IGZO layer as can be seen in Supplementary Fig. S3d. Additionally, ToF–SIMS also detected a smaller amount of gallium, zinc, and oxygen at the top interface compared to the bulk (Supplementary Fig. S3), which is consistent with a larger population of defects at the top interface.

Hydrogen impurities generate two types of defects, depending on whether they are bonded to an oxygen (OH) or to a metal (M-H) site. The OH defects have negative formation energy, implying a spontaneous formation whenever hydrogen is present. These defects do not generate states in the gap but act as donors until a high electron concentration is achieved, after which hydrogen starts to bind itself to metal sites, forming acceptors which compensate for the surplus of electrons in the a-IGZO. As the M-H bond requires an electron to form, it thus helps to limit the carrier concentration in a-IGZO, and forms states just above the EVS3).

The XPS analysis has reviewed that the top surface of the a-IGZO layer is the most affected by light radiation, showing a sizeable increase in the number of VO and Si–O defects. Additionally, calculations for In2O3 crystals have shown that VO can behave as shallow donors when located at the surface rather than in the bulk5/2, Ga2p3/2, and Zn2p3/2 peaks is mainly confined to the top half of the a-IGZO film (Supplementary Fig. S2) and a linear plot of the transfer characteristics in Fig. 1c shows two different slopes for negative and positive VGS (Supplementary Fig. S4), which clearly indicates the presence of two logical channels with two different resistances. Taking all this into consideration, the formation of the subthreshold hump in the transfer characteristics after deep UV radiation can thus be explained by the creation of shallow donors at the top surface of the a-IGZO film. This will create a parasitic channel (backchannel) with a conductance that is higher than that of the a-IGZO bulk (frontchannel)

Figure 5 shows how this conductive backchannel is manifested as a hump in the transfer characteristics of the a-IGZO TFTs post radiation. In Fig. 5a, the transfer characteristics are divided into three regions, labeled I, II, and III. In region I, the a-IGZO layer is depleted of electrons due to the strong negative VGS and only holes remain in the channel. In a-IGZO, it is difficult to induce holes with negative VGS, owing to the large concentration of VO located less than 1 eV above EVDS, resulting in a small hole current and lowering of the source barrier for electron injection (Fig. 5b)5c). In region III, both the front and backchannel are conducting, and ID is the sum of the currents flowing in the two channels (Fig. 5d).

In region III, the current due to the backchannel is lower than that of the bulk (front) (Fig. 5a) because the latter is thicker than the former. TCAD simulation of the TFT transfer characteristics with (Fig. 6a) and without (Fig. 6b) a highly conductive top surface of the a-IGZO film, also yielded the same results (Fig. 6c), verifying the hump formation mechanism. Here, a 2 nm-thick a-IGZO layer with a donor concentration (ngd) of 7 × 1018 cm−3 is used to represent the highly conductive a-IGZO top surface (Fig. 6b). ngd of the bulk is 1 × 1017 cm−3. Other density of states parameters have the same values as those reported in6d) indicates that a highly conductive backchannel is responsible for the negative ΔVTH. Consistent with the mechanism for the “hump”, only the backchannel is conductive when the VGS is negative (e.g., VGS = − 10 V) as shown in Fig. 6e. When the VGS is positive (e.g., VGS = 10 V), conduction occurs in both the backchannel and frontchannel (Fig. 6f).

TCAD simulation of the effect of deep UV light radiation on a-IGZO TFTs. (a and b) Schematics representing the TFT models used to simulate TFT characteristics (a) before and (b) after deep UV light radiation. A 2 nm thick a-IGZO film with a donor concentration (ngd) of 7 × 1018 cm-3 is used to simulate the photoionization of neutral oxygen vacancies at the top surface of the a-IGZO film. ngd for the bulk is 1 × 1017 cm-3. (c) Simulated transfer characteristics. (d) Line profile of the electron concentration (ne) from the top to the bottom surface when VGS = 10 V. (e and f) Images showing the distribution of ne in the a-IGZO with a conductive backchannel when (e) VGS = − 10 V and (f) VGS = 10 V. The presence of a conductive top surface induces a negative ΔVTH and the “hump”.

It is important to note that the hump starts at the same point (at approximately VGS = 0 V), regardless of the UV light exposure time, although it progressively stretches into the negative VGS direction with increasing exposure time (Supplementary Fig. S4). This is consistent with the increase in the number of photoionized VO at the top surface of the a-IGZO film and the consequent increase in the backchannel current with UV exposure time. In other words, the negative ΔVTH is mostly due to defects generated at the top surface of the a-IGZO film. Application of negative VGS during light illumination pushes the EF towards EV and increases the concentration of holes, favoring the formation of these defects, which is why the effect is larger under NBIS.

It is expected for one to suspect that the results presented herein show defect generation only at the top surface because absorption of light with high photon energy (~ 7.2 eV) is limited to the top surface. However, the penetration depth for λ = 172 in a-IGZO has been reported to be 30 nm for intensity 8 times smaller than the one used herein0) of 400 mW/cm2, the transmitted light intensity (It) can be estimated from

to be approximately ~ 54 mW/cm2, which is too high to eliminate absorption at the bottom surface of the a-IGZO. Here, α is the absorption coefficient, which is assumed to be approximately 106 cm−1 for λ = 172 nm based on the extrapolation of previously published resultsO states that are intrinsic to the top surface of the a-IGZO films.

Thermodynamic calculations have estimated the formation energy of the VO0 in a-IGZO to be approximately 4 eVO to be present in large amounts in native films, consistent with the bulk of the a-IGZO films presented herein (Fig. 4c). However, 4 eV is less than the photon energy of the deep UV light (~ 7.2 eV), making their photo-creation possible. Furthermore, VO can be created from centers with weak or broken bonds in the presence of light, due to the release of energy from electron–hole recombination. Similarly, ε(0/2 +) can be greatly reduced through recombination of the electrons bound to the VO0 with photogenerated holes, resulting in VO2+.

The above-mentioned mechanism is similar to the Staebler Wronski effect in a-Si:H-3 has been detected in a-IGZOO-related species are apparent at the top surface of the a-IGZO films presented herein.

Having identified the backchannel as the source of most of the light instability, owing to the defects that occupy the top surface of the a-IGZO, the effect of applying a back bias to reduce the instability is investigated. Double gate TFT structures with transparent top gates that fully (Fig. 8a) or partially (Fig. 8e) cover the channel region are used in the investigation. A transparent material (IZO) is intentionally used for the top gates to isolate the effect of the electrical back bias from that of light-shielding. Three bias conditions are investigated: (1) Top gate (TG) sweep, where the TG is swept from − 15 to 15 V, while grounding the bottom gate (BG) (see inset of Fig. 8f). (2) BG sweep, where the BG is swept from − 15 to 15 V, while grounding the TG (see inset of Fig. 8g). (3) Double gate (DG) sweep, where the TG and BG are shorted and swept from − 15 to 15 V (see inset of Fig. 8h).

Effect of back bias on deep UV light (λ = 172 nm) instability in a-IGZO TFTs. (a and e) Double gate TFT structures used for the investigation with a (a) full and (e) partial back gate (top gate). A transparent top gate (TG) material (IZO) is used to separate the bias from the light-shielding effect. (c to h and f to h) Evolution of transfer characteristics with light exposure time under three bias conditions: (b) and (f) Top gate (TG) sweep, where the TG is swept while grounding the bottom gate as shown by the inset of (f). (c) and (g) BG sweep, where the BG is swept while grounding the TG as shown by the inset of (g). (d) and (h) Double gate (DG) sweep, where TG and BG are shorted as shown by the inset of (h). Grounding or applying a positive back bias after radiation suppresses light instability in a-IGZO TFTs.

Extracted TFT parameters can be found in Supplementary Fig. S5. The DG TFT results are interesting and support the light instability mechanism described above. First, the existence of a full TG bias suppresses the negative ΔVTH, for all bias conditions (see Fig. 8b–d and Supplementary Fig. S5a). However, the off-state leakage current (IOFF) significantly increases after UV light radiation (Fig. 8 and Supplementary Fig. S5b). This indicates that IOFF is the result of photogenerated holes drifting from the D to the S. While a grounded or negatively biased TG suppresses electrons from the conductive backchannel, which is the reason for the negligible ΔVTH, it promotes hole induction, consistent with the high IOFF. IOFF is also high during the DG sweep (grounded TG) because the hole layer is simply shifted towards the frontchannel, which is negatively biased. Grounding or negatively biasing the TG does not make a big difference with regards to the size of the off-state current because hole induction by VGS is difficult in a-IGZO, owing to the large concentration of VO located less than 1 eV above EV

Second, negative ΔVTH and increase in SS occur after UV light radiation for 3600 s when a partial TG is implemented (Fig. 8f and Supplementary Fig. S5c). However, the negative ΔVTH is not as large as that of a single gate TFT (Fig. 1c), indicating partial suppression of the conductive backchannel electrons by the partial TG. Additionally, the SS increases without the formation of a hump during the TG sweep (Fig. 8f) because there is only one channel (the backchannel) involved, supporting the mechanism for the “hump”. However, suppression of the effect of the conductive backchannel electrons can be seen during the BG (Fig. 8g) or DG (Fig. 8h) sweep with a partial TG but evidence of it just starting to appear is apparent. The increase in the on-state current (ION) after UV light radiation during the TG sweep (Fig. 8f) is consistent with a photoinduced increase in the conductance of the offset regions. Note that the increase in ION after UV light radiation is almost negligible when a full TG is implemented (Supplementary Fig. S5b). Consequently, the change in field-effect mobility after UV light radiation is exceedingly small when a full TG is used (Supplementary Fig. S5d).

These results provide further evidence showing that defects occupying the top surface of the a-IGZO are the source of the light instability in a-IGZO TFTs and that their effect can be suppressed by applying a back bias. This is especially important in applications such as transparent displays where the use of light shields is not possible. Although back biasing does not prevent the off-state currents from increasing, this is not expected to be a problem as they do not exceed 100 pA and they quickly recover at room temperature when the holes recombine. An alternative to applying a back bias, for instance in single gate inverted staggered TFTs (Fig. 1a), would be to reduce the thickness of the a-IGZO film. By doing this, the bottom (front) gate will not only have control of the backchannel, but the total number of defects is also reduced9, using an a-IGZO film thickness of 7 nm results in negligible ΔVTH.

Threshold voltage shift (ΔVTH) in inverted staggered (single gate) a-IGZO TFTs as a function of deep UV light (λ = 172 nm) exposure time. Reducing the thickness of the a-IGZO from 20 to 7 nm almost completely suppresses the deep UV light instability. a-IGZO film thickness reduction enhances the bottom gate control over the back (top) channel and also decreases the total number of defects.

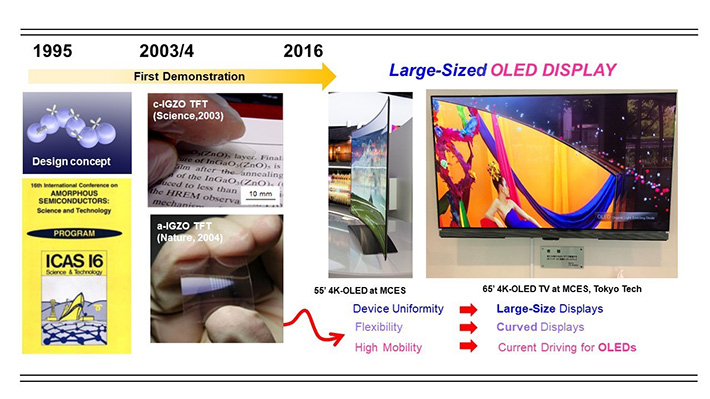

Liquid crystal displays (LCD) began to replace cathode-ray tube-based televisions in the early 2000s. The pixels in these LCDs were, until 2012, driven exclusively by thin-film transistors (TFTs) that use amorphous hydrogenated silicon (a-Si:H) as the semiconducting channel. But as demand grew for ever larger displays, with better viewing and energy performance, a need for improved TFTs emerged. TFTs block light coming from the display, so they need to be small, which lowers their current-driving ability. Additionally, there was a push to move away from LCD technology and into organic light emitting diodes (OLEDs) in order to capitalize on their better performance, which includes direct emission and richer colours, but OLEDs need to be driven by large amounts of current, at levels a-Si:H TFTs cannot accommodate. What was needed was a new technology that could be used to create TFTs with a high charge carrier mobility, which could drive large currents.

Charge carrier mobility tells us how quickly charge carriers (electrons and holes) can move through a semiconductor, and determines the amount of current we can drive through a TFT of a given size. This is limited by the nature of the path that charge carriers take though a material. This path can be thought of in terms of the atomic orbitals and how they interconnect to make up the conduction and valence bands — the energetic levels at which the electrons and holes are free to move around. The sp3 hybridized orbitals in silicon are highly directional, and in the crystalline state the silicon–silicon bonds properly overlap, providing an efficient path to travel through. However, in amorphous silicon, structural disorder leads to disconnects and conduction cannot occur through the orbitals in the same way. Instead, the charge carriers have to hop across the orbitals, which leads to mobilities of at most 1 cm2 V–1 s–1 — about 2–3 orders of magnitude lower than in crystalline silicon.

After a few years verifying the validity of the hypothesis, we started research on transparent oxide TFTs. To develop high-mobility TFTs using transparent conductive oxides, the major issue was their high carrier concentrations (the TFTs can’t be turned off). Indium oxide is a typical transparent conductive oxide with a large mobility, but reducing its excessive carrier concentration is difficult due the ease with which oxygen vacancies form. We tested InGaO3(ZnO)m epitaxial films, where m = 4 and 5, as I believed the unique local structure around Ga3+ would help lower the carrier concentration. As expected, the carrier concentration in epitaxial InGaO3(ZnO)4 reduced to a suitable level, and when applied in TFTs showed excellent performance, with a mobility of approximately 80 cm2 V–1 s–1. We then fabricated thin films using amorphous InGaZnO4 (a-IGZO). The electron concentrations in the resulting a-IGZO thin films, which were deposited on glass substrates at room temperature, were below 1016 cm–3 and the TFTs exhibited mobilities of approximately 10 cm2 V–1 s–1 — an order of magnitude larger than that of a-Si:H TFTs. We also found that TFTs fabricated on plastic substrates offered almost identical performance (Fig. 1). At this point we applied for patents and then submitted our paper to Nature, which was published in 2004.

Demonstrations of IGZO TFT-based displays began to emerge in 2007, when Samsung Electronics first reported a-IGZO TFT-based high-definition LCDs. Demonstrations of IGZO TFT-based backplane LCDs in smart phones and tablet computers then appeared around 2012. Arguably the most striking application emerged in 2015, when LG Display demonstrated large-sized OLED televisions. Here the a-IGZO TFT was indispensable because of the need for high mobility and simple formation over large areas.

I believe the success of IGZO transistors is due to a number of factors. First is their high mobility, which is an order of magnitude higher than a-Si:H, and the excellent controllability of their carrier concentration. Second, the production process is almost the same as a-Si:H, except for the deposition of the channel layer (chemical vapour deposition is used for a-Si:H whereas sputtering is used for IGZO), making integration into current manufacturing workflows relatively painless. Third, synthesizing large-sized high-quality sputtering targets is relatively easy, which also makes thin-film deposition on large-sized substrates a relatively simple task. With these attributes, IGZO transistors provide a promising backplane technology to drive the future of flat panel displays.

AbstractIn this paper, we analyze application of amorphous Indium‐Gallium‐Zinc‐Oxide thin film transistors (a‐InGaZnO TFTs) to voltage‐driven pixel electrode circuit that could be used for 4.3‐in. wide video graphics array (WVGA) full color active‐matrix organic light‐emitting displays (AM‐OLEDs). Simulation results, based on a‐InGaZnO TFT and OLED experimental data, show that both device sizes and operational voltages can be reduced when compared to the same circuit using hydrogenated amorphous silicon (a‐Si:H) TFTs. Moreover, the a‐InGaZnO TFT pixel circuit can compensate for the threshold voltage variation (ΔV TH ) of driving TFT within acceptable operating error range.

We succeeded in G8 factory for mass production of Indium–Gallium–Zink–Oxide thin‐film transistor (IGZO‐TFT) for the first time in the world. The initial TFT process was an etching stop‐type TFT, but now, we are mass producing channel etching‐type TFTs. And, its application range is smartphones, tablets, PCs, monitors, TV, and so on. In particular, because of recent demands for high‐resolution and narrow frame, our IGZO display has been advanced in technology development with gate driver in…Expand

A. Kumar, A.K. Goyal, N. Gupta, Review—thin-film transistors (TFTs) for highly sensitive biosensing applications: a review. ECS J. Solid State Sci. Technol. 9, 115022 (2020)

M.C. Yu, D.B. Ruan, P.T. Liu, T.C. Chien, Y.C. Chiu, K.J. Gan, S.M. Sze, High performance transparent a-IGZO thin film transistors with ALD-HfO2Gate insulator on colorless polyimide substrate. IEEE Trans. Nanotechnol. 19, 481–485 (2020)

R.P. Singh, M. Khosla, I. Saini, N. Kumar, Design and analysis of IGZO based junctionless thin film transistor using SOI technology. Silicon 13, 2309 (2020)

G.J. Lee, J. Kim, J.H. Kim, S.M. Jeong, J.E. Jang, J. Jeong, High performance, transparent a-IGZO TFTs on a flexible thin glass substrate. Semicond. Sci. Technol. 29, 035003 (2014)

J. Sheng, T.H. Hong, H.M. Lee, K.R. Kim, M. Sasase, J. Kim, H. Hosono, J.S. Park, Amorphous IGZO TFT with high mobility of 70 cm2/(V s) via vertical dimension control using PEALD. ACS Appl. Mater. Interfaces 11, 40300–40309 (2019)

K. Ide, M. Kikuchi, M. Sasase, H. Hiramatsu, H. Kumomi, H. Hosono, T. Kamiya, Why high-pressure sputtering must be avoided to deposit a-In-Ga-Zn-O films, in Proceedings of AM-FPD 2016—23rd International Workshop on Active-Matrix Flatpanel Displays and Devices: TFT Technologies and FPD Materials (2016), pp. 298–301

E. Lee, T.H. Kim, S.W. Lee, J.H. Kim, J. Kim, T.G. Jeong, J.H. Ahn, B. Cho, Improved electrical performance of a sol–gel IGZO transistor with high-k Al2O3 gate dielectric achieved by post annealing. Nano Converg. 6, 1–8 (2019)

C.Y. Chen, J. Kanicki, High field-effect-mobility a-Si: H TFT based on high deposition-rate PECVD materials. IEEE Electron Device Lett. 17, 437–439 (1996)

J. Chen, H. Ning, Z. Fang, R. Tao, C. Yang, Y. Zhou, R. Yao, M. Xu, L. Wang, J. Peng, Reduced contact resistance of a-IGZO thin film transistors with inkjet-printed silver electrodes. J. Phys. D Appl. Phys. 51, 165103 (2018)

R.A. Sporea, K.M. Niang, A.J. Flewitt, S.R.P. Silva, Novel tunnel-contact-controlled IGZO thin-film transistors with high tolerance to geometrical variability. Adv. Mater. 31, 1902551 (2019)

C.Y. Lin, K. Tang, C.M. Leu, Y.H. Yeh, Flexible IGZO thin-film transistors and inverter circuits with diode-connected transistors fabricated on transparent polyimide substrates. Microsyst. Technol. 6, 1–4 (2019)

Indium Gallium Zinc Oxide (IGZO) is a key transparent semi-conductive material for new generation TFT technology. It can replace Si layer as channel material in TFT. With excellent property, it is used to manufacture high-performance LCD and OLED displays, helping achieve higher resolution, lower power consumption and lower noise.Symbol:IGZO

This work proposes a new pixel structure based on amorphous indium-gallium-zinc-oxide thin-film transistors (a-IGZO TFTs) and a parallel addressing scheme for high-resolution active-matrix organic light-emitting diode (AMOLED) displays. The proposed circuit compensates for the nonuniformity of luminance that is caused by shifts in the threshold voltage (${{V}}_{{\rm{TH}}}$) and mobility of driving TFTs. Measurement results verify that the parallel addressing scheme successfully extends the compensation time and accurately detects the ${{V}}_{{\rm{TH}}}$ of the driving TFT. Moreover, the proposed circuit reduces the variations of OLED luminance from more than 83% to less than 13% when the ${{V}}_{{\rm{TH}}}$ and mobility of driving TFT shifts by 1 V and 30%, respectively, and the ${{V}}_{{\rm{TH}}}$ of OLED varies from 0 to 0.9 V.

A thin-film transistor (TFT) is a special type of field-effect transistor (FET) where the transistor is thin relative to the plane of the device.substrate. A common substrate is glass, because the traditional application of TFTs is in liquid-crystal displays (LCDs). This differs from the conventional bulk metal oxide field effect transistor (MOSFET), where the semiconductor material typically is the substrate, such as a silicon wafer.

TFTs can be fabricated with a wide variety of semiconductor materials. Because it is naturally abundant and well understood, amorphous or polycrystalline silicon was historically used as the semiconductor layer. However, because of the low mobility of amorphous siliconcadmium selenide,metal oxides such as indium gallium zinc oxide (IGZO) or zinc oxide,organic semiconductors,carbon nanotubes,metal halide perovskites.

Because TFTs are grown on inert substrates, rather than on wafers, the semiconductor must be deposited in a dedicated process. A variety of techniques are used to deposit semiconductors in TFTs. These include chemical vapor deposition (CVD), atomic layer deposition (ALD), and sputtering. The semiconductor can also be deposited from solution,printing

Some wide band gap semiconductors, most notable metal oxides, are optically transparent.electrodes, such as indium tin oxide (ITO), some TFT devices can be designed to be completely optically transparent.head-up displays (such as on a car windshield).The first solution-processed TTFTs, based on zinc oxide, were reported in 2003 by researchers at Oregon State University.Universidade Nova de Lisboa has produced the world"s first completely transparent TFT at room temperature.

The best known application of thin-film transistors is in TFT LCDs, an implementation of liquid-crystal display technology. Transistors are embedded within the panel itself, reducing crosstalk between pixels and improving image stability.

As of 2008LCD TVs and monitors use this technology. TFT panels are frequently used in digital radiography applications in general radiography. A TFT is used in both direct and indirect capturemedical radiography.

The most beneficial aspect of TFT technology is its use of a separate transistor for each pixel on the display. Because each transistor is small, the amount of charge needed to control it is also small. This allows for very fast re-drawing of the display.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET in which germanium monoxide was used as a gate dielectric. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. In 1966, T.P. Brody and H.E. Kunig at Westinghouse Electric fabricated indium arsenide (InAs) MOS TFTs in both depletion and enhancement modes.

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard J. Lechner of RCA Laboratories in 1968.dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).electroluminescence (EL) in 1973, using CdSe.active-matrix liquid-crystal display (AM LCD) using CdSe in 1974, and then Brody coined the term "active matrix" in 1975.

A breakthrough in TFT research came with the development of the amorphous silicon (a-Si) TFT by P.G. le Comber, W.E. Spear and A. Ghaith at the University of Dundee in 1979. They reported the first functional TFT made from hydrogenated a-Si with a silicon nitride gate dielectric layer.research and development (R&D) of AM LCD panels based on a-Si TFTs in Japan.

By 1982, Pocket TVs based on AM LCD technology were developed in Japan.Fujitsu"s S. Kawai fabricated an a-Si dot-matrix display, and Canon"s Y. Okubo fabricated a-Si twisted nematic (TN) and guest-host LCD panels. In 1983, Toshiba"s K. Suzuki produced a-Si TFT arrays compatible with CMOS integrated circuits (ICs), Canon"s M. Sugata fabricated an a-Si color LCD panel, and a joint Sanyo and Sanritsu team including Mitsuhiro Yamasaki, S. Suhibuchi and Y. Sasaki fabricated a 3-inch a-SI color LCD TV.

The first commercial TFT-based AM LCD product was the 2.1-inch Epson ET-10Hitachi research team led by Akio Mimura demonstrated a low-temperature polycrystalline silicon (LTPS) process for fabricating n-channel TFTs on a silicon-on-insulator (SOI), at a relatively low temperature of 200°C.Hosiden research team led by T. Sunata in 1986 used a-Si TFTs to develop a 7-inch color AM LCD panel,Apple Computers.Sharp research team led by engineer T. Nagayasu used hydrogenated a-Si TFTs to demonstrate a 14-inch full-color LCD display,electronics industry that LCD would eventually replace cathode-ray tube (CRT) as the standard television display technology.notebook PCs.IBM Japan introduced a 12.1-inch color SVGA panel for the first commercial color laptop by IBM.

TFTs can also be made out of indium gallium zinc oxide (IGZO). TFT-LCDs with IGZO transistors first showed up in 2012, and were first manufactured by Sharp Corporation. IGZO allows for higher refresh rates and lower power consumption.polyimide substrate.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

Mimura, Akio; Oohayashi, M.; Ohue, M.; Ohwada, J.; Hosokawa, Y. (1986). "SOI TFT"s with directly contacted ITO". IEEE Electron Device Letters. 7 (2): 134–6. Bibcode:1986IEDL....7..134M. doi:10.1109/EDL.1986.26319. ISSN 0741-3106. S2CID 36089445.

Sunata, T.; Yukawa, T.; Miyake, K.; Matsushita, Y.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A large-area high-resolution active-matrix color LCD addressed by a-Si TFT"s". 33 (8): 1212–1217. Bibcode:1986ITED...33.1212S. doi:10.1109/T-ED.1986.22644. ISSN 0018-9383. S2CID 44190988.

Sunata, T.; Miyake, K.; Yasui, M.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A 640 × 400 pixel active-matrix LCD using a-Si TFT"s". IEEE Transactions on Electron Devices. 33 (8): 1218–21. Bibcode:1986ITED...33.1218S. doi:10.1109/T-ED.1986.22645. ISSN 0018-9383. S2CID 6356531.

Nagayasu, T.; Oketani, T.; Hirobe, T.; Kato, H.; Mizushima, S.; Take, H.; Yano, K.; Hijikigawa, M.; Washizuka, I. (October 1988). "A 14-in.-diagonal full-color a-Si TFT LCD". Conference Record of the 1988 International Display Research Conference: 56–58. doi:10.1109/DISPL.1988.11274. S2CID 20817375.

A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display that uses thin-film-transistor technologyactive matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven (i.e. with segments directly connected to electronics outside the LCD) LCDs with a few segments.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968. In 1971, Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated a 2-by-18 matrix display driven by a hybrid circuit using the dynamic scattering mode of LCDs.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).active-matrix liquid-crystal display (AM LCD) using CdSe TFTs in 1974, and then Brody coined the term "active matrix" in 1975.high-resolution and high-quality electronic visual display devices use TFT-based active matrix displays.

The liquid crystal displays used in calculators and other devices with similarly simple displays have direct-driven image elements, and therefore a voltage can be easily applied across just one segment of these types of displays without interfering with the other segments. This would be impractical for a large display, because it would have a large number of (color) picture elements (pixels), and thus it would require millions of connections, both top and bottom for each one of the three colors (red, green and blue) of every pixel. To avoid this issue, the pixels are addressed in rows and columns, reducing the connection count from millions down to thousands. The column and row wires attach to transistor switches, one for each pixel. The one-way current passing characteristic of the transistor prevents the charge that is being applied to each pixel from being drained between refreshes to a display"s image. Each pixel is a small capacitor with a layer of insulating liquid crystal sandwiched between transparent conductive ITO layers.

The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. However, rather than fabricating the transistors from silicon, that is formed into a crystalline silicon wafer, they are made from a thin film of amorphous silicon that is deposited on a glass panel. The silicon layer for TFT-LCDs is typically deposited using the PECVD process.

Polycrystalline silicon is sometimes used in displays requiring higher TFT performance. Examples include small high-resolution displays such as those found in projectors or viewfinders. Amorphous silicon-based TFTs are by far the most common, due to their lower production cost, whereas polycrystalline silicon TFTs are more costly and much more difficult to produce.

The twisted nematic display is one of the oldest and frequently cheapest kind of LCD display technologies available. TN displays benefit from fast pixel response times and less smearing than other LCD display technology, but suffer from poor color reproduction and limited viewing angles, especially in the vertical direction. Colors will shift, potentially to the point of completely inverting, when viewed at an angle that is not perpendicular to the display. Modern, high end consumer products have developed methods to overcome the technology"s shortcomings, such as RTC (Response Time Compensation / Overdrive) technologies. Modern TN displays can look significantly better than older TN displays from decades earlier, but overall TN has inferior viewing angles and poor color in comparison to other technology.

Most TN panels can represent colors using only six bits per RGB channel, or 18 bit in total, and are unable to display the 16.7 million color shades (24-bit truecolor) that are available using 24-bit color. Instead, these panels display interpolated 24-bit color using a dithering method that combines adjacent pixels to simulate the desired shade. They can also use a form of temporal dithering called Frame Rate Control (FRC), which cycles between different shades with each new frame to simulate an intermediate shade. Such 18 bit panels with dithering are sometimes advertised as having "16.2 million colors". These color simulation methods are noticeable to many people and highly bothersome to some.gamut (often referred to as a percentage of the NTSC 1953 color gamut) are also due to backlighting technology. It is not uncommon for older displays to range from 10% to 26% of the NTSC color gamut, whereas other kind of displays, utilizing more complicated CCFL or LED phosphor formulations or RGB LED backlights, may extend past 100% of the NTSC color gamut, a difference quite perceivable by the human eye.

In 2004, Hydis Technologies Co., Ltd licensed its AFFS patent to Japan"s Hitachi Displays. Hitachi is using AFFS to manufacture high end panels in their product line. In 2006, Hydis also licensed its AFFS to Sanyo Epson Imaging Devices Corporation.

A technology developed by Samsung is Super PLS, which bears similarities to IPS panels, has wider viewing angles, better image quality, increased brightness, and lower production costs. PLS technology debuted in the PC display market with the release of the Samsung S27A850 and S24A850 monitors in September 2011.

TFT dual-transistor pixel or cell technology is a reflective-display technology for use in very-low-power-consumption applications such as electronic shelf labels (ESL), digital watches, or metering. DTP involves adding a secondary transistor gate in the single TFT cell to maintain the display of a pixel during a period of 1s without loss of image or without degrading the TFT transistors over time. By slowing the refresh rate of the standard frequency from 60 Hz to 1 Hz, DTP claims to increase the power efficiency by multiple orders of magnitude.

Due to the very high cost of building TFT factories, there are few major OEM panel vendors for large display panels. The glass panel suppliers are as follows:

External consumer display devices like a TFT LCD feature one or more analog VGA, DVI, HDMI, or DisplayPort interface, with many featuring a selection of these interfaces. Inside external display devices there is a controller board that will convert the video signal using color mapping and image scaling usually employing the discrete cosine transform (DCT) in order to convert any video source like CVBS, VGA, DVI, HDMI, etc. into digital RGB at the native resolution of the display panel. In a laptop the graphics chip will directly produce a signal suitable for connection to the built-in TFT display. A control mechanism for the backlight is usually included on the same controller board.

The low level interface of STN, DSTN, or TFT display panels use either single ended TTL 5 V signal for older displays or TTL 3.3 V for slightly newer displays that transmits the pixel clock, horizontal sync, vertical sync, digital red, digital green, digital blue in parallel. Some models (for example the AT070TN92) also feature input/display enable, horizontal scan direction and vertical scan direction signals.

New and large (>15") TFT displays often use LVDS signaling that transmits the same contents as the parallel interface (Hsync, Vsync, RGB) but will put control and RGB bits into a number of serial transmission lines synchronized to a clock whose rate is equal to the pixel rate. LVDS transmits seven bits per clock per data line, with six bits being data and one bit used to signal if the other six bits need to be inverted in order to maintain DC balance. Low-cost TFT displays often have three data lines and therefore only directly support 18 bits per pixel. Upscale displays have four or five data lines to support 24 bits per pixel (truecolor) or 30 bits per pixel respectively. Panel manufacturers are slowly replacing LVDS with Internal DisplayPort and Embedded DisplayPort, which allow sixfold reduction of the number of differential pairs.

The bare display panel will only accept a digital video signal at the resolution determined by the panel pixel matrix designed at manufacture. Some screen panels will ignore the LSB bits of the color information to present a consistent interface (8 bit -> 6 bit/color x3).

With analogue signals like VGA, the display controller also needs to perform a high speed analog to digital conversion. With digital input signals like DVI or HDMI some simple reordering of the bits is needed before feeding it to the rescaler if the input resolution doesn"t match the display panel resolution.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

K. H. Lee; H. Y. Kim; K. H. Park; S. J. Jang; I. C. Park & J. Y. Lee (June 2006). "A Novel Outdoor Readability of Portable TFT-LCD with AFFS Technology". SID Symposium Digest of Technical Papers. AIP. 37 (1): 1079–82. doi:10.1889/1.2433159. S2CID 129569963.

Kim, Sae-Bom; Kim, Woong-Ki; Chounlamany, Vanseng; Seo, Jaehwan; Yoo, Jisu; Jo, Hun-Je; Jung, Jinho (15 August 2012). "Identification of multi-level toxicity of liquid crystal display wastewater toward Daphnia magna and Moina macrocopa". Journal of Hazardous Materials. Seoul, Korea; Laos, Lao. 227–228: 327–333. doi:10.1016/j.jhazmat.2012.05.059. PMID 22677053.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey