tft lcd frame buffer pricelist

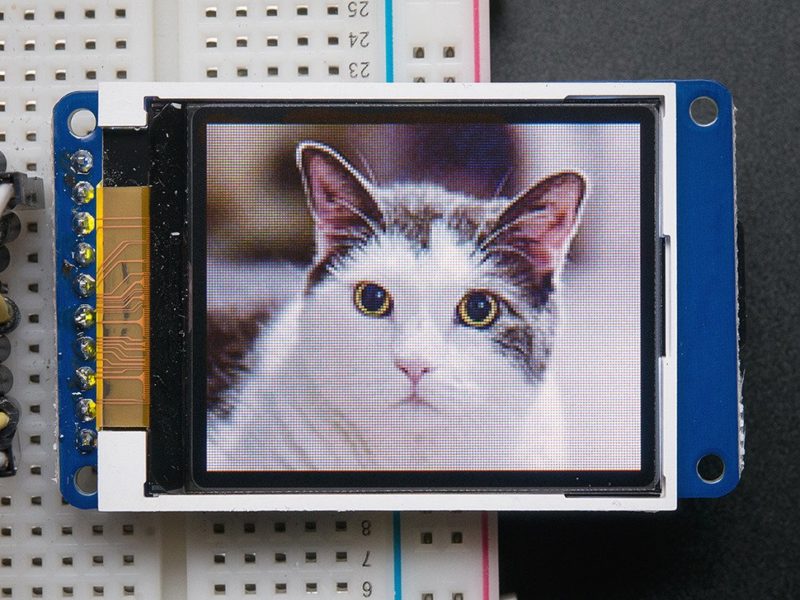

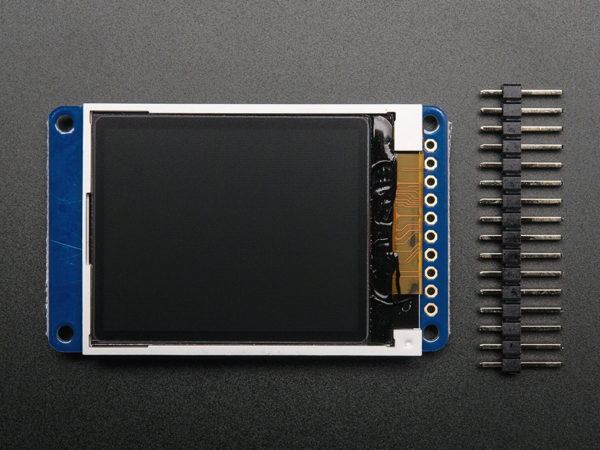

The 1.8″ display has 128×160 color pixels. Unlike the low cost “Nokia 6110” and similar LCD displays, which are CSTN type and thus have poor color and slow refresh, this display is a true TFT! The TFT driver (ST7735R) can display full 18-bit color (262,144 shades!). And the LCD will always come with the same driver chip so there’s no worries that your code will not work from one to the other.

The breakout has the TFT display soldered on (it uses a delicate flex-circuit connector) as well as a ultra-low-dropout 3.3V regulator and a 3/5V level shifter so you can use it with 3.3V or 5V power and logic, which allows you to use the display with virtually any microcontroller. There’s also a microSD card holder so you can easily load full color bitmaps from a FAT16/FAT32 formatted microSD card. The microSD card is not included.

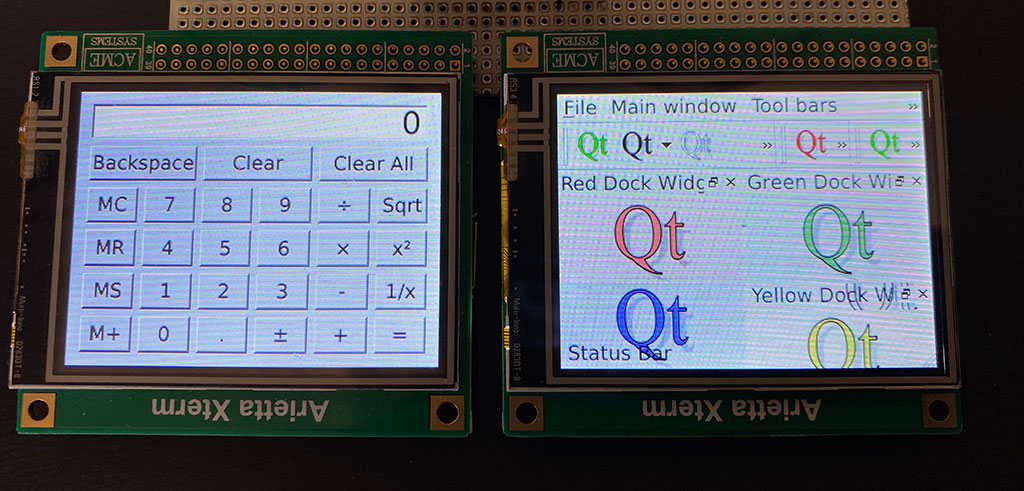

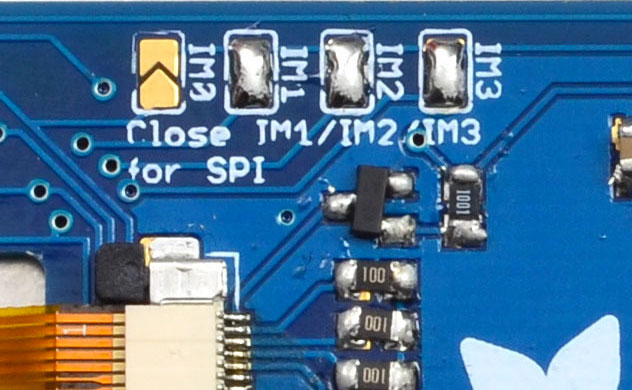

This lovely little display breakout is the best way to add a small, colorful and bright display to any project. Since the display uses 4-wire SPI to communicate and has its own pixel-addressable frame buffer, it can be used with every kind of microcontroller. Even a very small one with low memory and few pins available!

The 1.44" display has 128x128 color pixels. Unlike the low cost "Nokia 6110" and similar LCD displays, which are CSTN type and thus have poor color and slow refresh, this display is a true TFT! The TFT driver (ST7735R) can display full 16-bit color using our library code.

The breakout has the TFT display soldered on (it uses a delicate flex-circuit connector) as well as a ultra-low-dropout 3.3V regulator and a 3/5V level shifter so you can use it with 3.3V or 5V power and logic. We also had a little space so we placed a microSD card holder so you can easily load full color bitmaps from a FAT16/FAT32 formatted microSD card. The microSD card is not included, but you can pick one up here.

The TS-7390 is a compact full-featured Single Board Computer (SBC) based upon the Cirrus EP9302 200MHz Arm9™-based CPU, which provides a standard set of on-board peripherals. This product features an on-board FPGA with a dedicated 8MB RAM Framebuffer and a 800x480 video core integrated with a 7-inch Color TFT-LCD panel with TouchScreen Interface, as shown by the TS-TPC-7390 product pictures. The TS-7390 boots Linux2.6 out-of-the-box from on-board NAND flash or an SD Card and the included Debian Linux distribution provides driver and software library support for embedded video/touchscreen applications.

please call us for information about pricing or product customization. Also, for customers looking for a custom SBC solution for their LCD+TouchScreen

SOLOMON SYSTECH SEMICONDUCTOR TECHNICAL DATA Advance Information 1215KB Embedded Display SRAM LCD Display Controller This document contains information on a new product. Specifications and information herein are subject to change without notice. http://www.solomon-systech.com SSD1963 Rev 1.1 P 1/93 Copyright © 2010 Solomon Systech Limited

GENERAL DESCRIPTION SSD1963 is a display controller of 1215K byte frame buffer to support up to 864 x 480 x 24bit graphics content. It also equips parallel MCU interfaces in different bus width to receive graphics data and command from MCU. Its display interface supports common RAM-less LCD driver of color depth up to 24 bit-perpixel. Display feature − Built-in 1215K bytes frame buffer. Support up to 864 x 480 at 24bpp display − Support TFT 18/24-bit generic RGB interface panel − Support 8-bit serial RGB interface − Hardware rotation of 0, 90, 180, 270 degree − Hardware display mirroring −...

Signal Name VDDD VSS VSS VDDIO VSS VDDD D0 D1 D2 D3 D4 VDDIO VSS VDDD CLK VDDIO VSS VDDPLL VSSPLL VSS VDDD XTAL_IN VSS XTAL_OUT VDDD VSS VDDLCD LDATA23 LDATA22 LDATA21 LDATA20 VDDD Solomon Systech Signal Name VSS VDDLCD LDATA17 GPIO0 GPIO1 GPIO2 GPIO3 VDDD VSS VDDLCD LFRAME LLINE LSHIFT VDDD VSS VDDLCD LDEN TE PWM GAMAS0 GAMAS1 VDDLCD VSS VDDD VSS VDDLCD LDATA16 LDATA15 LDATA14 LDATA13 LDATA12 VDDD Signal Name VDDIO D17 D16 VDDIO VSS VDDD D15 D14 D13 D12 D11 VDDIO VSS VDDD D10 D9 D8 D7 D6 D5 VDDIO VSS VDDD R/W#(WR#) E(RD#) D/C# CS# VDDIO VSS VDDD RESET# CONF

Table 6-2: LCD Interface Pin Mapping Pin Name LFRAME LLINE LSHIFT LDEN Reference Type Voltage Level O VDDLCD O VDDLCD O VDDLCD O VDDLCD VDDLCD VDDLCD Description Vertical sync (Frame pulse) Horizontal sync (Line pulse) Pixel clock (Pixel shift signal) Data valid These pins can be configured for display 36, 37, 38, 39 miscellaneous signals or as general purpose I/O. Default as input 52, 53 Gamma selection for panel 51 PWM output for backlight driver Table 6-3: Control Signal Pin Mapping Pin Name RESET# CONF Reference Type Voltage Level I VDDIO I Description Master synchronize reset MCU...

Table 7-1: Pixel Data Format Tearing Effect Signal (TE) The Tearing Effect Signal (TE) is a feedback signal from the LCD Controller to MCU. This signal reveals the display status of LCD controller. In the non-display period, the TE signal will go high. Therefore, this signal enables the MCU to send data by observing the non-display period to avoid tearing. Figure 7-1 shows how the TE signal helps to avoid tearing. If the MCU writing speed is slower than the display speed, the display data should be updated after the LCD controller start to scan the frame buffer. Then the LCD controller will...

Figure 7-1: Relationship between Tearing Effect Signal and MCU Memory Writing In SSD1963, users can configure the TE signal to reflect the vertical non-display period only or reflect both vertical and horizontal non-display period. With the additional horizontal non-display period information, the MCU can control the refresh action in more accurately by counting the horizontal line scanned by the LCD controller. Usually, a fast MCU will not need horizontal non-display period. But a slow MCU will need it to ensure the frame buffer update process always lags behind the LCD controller. System...

Figure 7-2: Clock Control Diagram set_pll bit 1 set_pll bit 0 EXTERNAL CRYSTAL Frame Buffer There are 1215K bytes built-in SRAM inside SSD1963 to use as frame buffer. When the frame buffer is written or read, the “address counter” will automatically increase by one or decrease by one depends on the frame buffer settings. Table 7-2: Frame Buffer Settings regarding to set_address_mode command 0x36 System Clock and Reset Manager The “System Clock and Reset Manager” distributes the reset signal and clock signal to the entire system. It controls the Clock Generator and contains clock gating...

I am using STM32H753 for driving 800x480 TFT LCD. Currently I am using External SDRAM for my FRAME BUFFER. I am using DMA2D and TFT LCD module of MCU.

I"m talking about some nxp mcu like lpc1788 with the lcd controller integrated into the chip so you don"t need to use an external lcd controller. The models you are listing don"t have the lcd controller integrated,.

The main advantage of having it external is that the lcd controller has got its own memory for the frame buffer and it"s easing the load on the cpu because once you load the data it will keep refreshing the screen without calling the cpu and it doesn"t use the cpu ram memory.

In the other case if the lcd controller is integrated in the mcu you can do some nice "tricks" like using a colour look up table or palette so that your graphics takes less memory and because the framebuffer is in your internal memory it is even easier to manipulate.

Also consider that in case of lcd controller not integrated in the panel (so by using the one integrated in the mcu or another one on board as a separate chip) you can exchange panel quite easily so you are not tied to a single manufacturer as long on the lcd side you find the same interface like the 24 bit or the 18 bit.

Now, I"m considering the case of an lcd panel of 640x480 and 8 bit per colour which leads us to 640x480x8 = 2457600 bit / 8 = 307200 / 1024 = 300 KByte of ram needed for the framebuffer.

The integrated lcd controller has got a dma which will take care of transferring the data from external ram used for the frambuffer to the lcd controller which will then translate it and send to lcd but the problem is that the external bus and also the internal bus of the mcu(difficult to draw this here :-) ) is then shared by the lcd controller, which keeps accessing the memory to continuously refresh the screen, and the mcu which is fetching instructions or variables.

Because the internal bus gives priority to the mcu it means that probably you will see tearing effect on the lcd like reported by some people on the nxp question and answer (pasting the link here takes you to the general support page and not to the answer I found) because the mcu gain priority when accessing bus and memory and lcd refresh is delayed.

In the answer I found on Nxp support, they say you can actually change priority so that lcd screen has an higher priority then the cpu, problem is that in doing so the cpu and then your software will be slowed down by the lcd controller continuously refreshing and accessing memories.

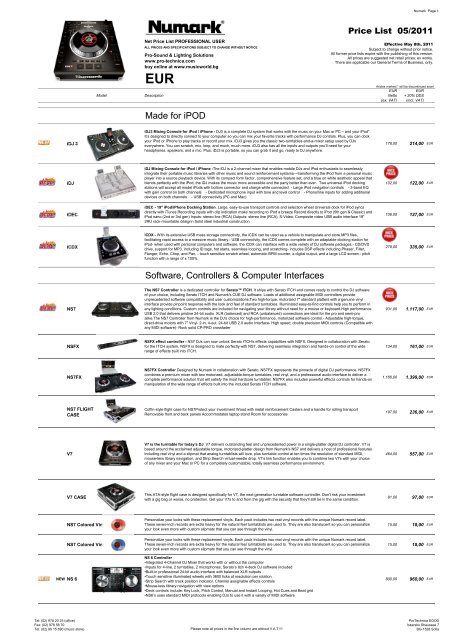

At present, TFT LCD touch panel prices rebounded, after six months of continuous decline, TFT LCD touch panel prices began to rebound at the end of July. Global TFT LCD panel prices have rebounded since August, according to Displaysearch, an international market-research firm. The price of a 17-inch LCD touch panel rose 6.6% to $112 in August, up from $105 in July, and fell from $140 in March to $105 in July. At the same time, 15 – inch, 19 – inch LCD touch panel prices also showed a different range of recovery. The price of a 17-inch LCD touch panel rose 5.8 percent, to $110, from $104 in late July, according to early August quotes from consulting firm with a view. Analysts believe the rebound will continue through the third quarter; LCDS will see seasonal growth in the third quarter, driven by back-to-school sales in us and the completion of inventory liquidation in the first half of the year. Dell and Hewlett-Packard (HPQ) started placing orders for monitors in the third quarter, and display makers Samsungelectronics (SXG) and TPV (TPV) are expected to increase production by 25% and 18% respectively.

It seems that due to the increasing demand in the market, the production capacity of the display panel production line has been released. Domestic TFT-LCD touch panel makers boe and Shanghai guardian said their production schedules have been set for September, and their production capacity may reach full capacity by the end of the year. Jd will produce 85,000 glass substrates per month (with a designed capacity of 90,000), according to boe and Shanghai guardian. Previously, panel makers have been hit by falling prices, with boe, SFT, and even international panel giant LG Philips all reporting losses. If the rebound continues into the fourth quarter, boe, Shanghai radio and television and other panel makers will use the rebound to reverse the decline, according to industry analysts.

It is understood that the first quarter of the boe financial results show that the company’s main business income of 2.44 billion yuan, a loss of 490 million yuan.Jd.com attributed the loss to a drop in the price of 17-inch TFT-LCD displays made by its Beijing TFT-LCD fifth-generation production line of Beijing boe photoelectric technology co., LTD., a subsidiary. Boe has issued the announcement of pre-loss in the first half of the year in April. Due to the influence of the off-season of TFT-LCD business operation in the first quarter of 2006, the company has suffered a large operating loss, and the low price in the TFT-LCD market has continued till now. Therefore, it is expected that the operating loss will still occur in the first half of 2006.LG Philips, the world’s largest TFT LCD maker, reported a won322bn ($340m) loss in July, compared with a won41.1bn profit a year earlier.LG Philips attributed the loss to fierce price competition and market demand did not meet expectations.

This application note describes the i.MX6 CPU graphical system and the steps to define a new custom TFT (Thin Film Transistor) display panel in Digi Embedded Yocto and discusses the most standard panels available. Some panels may need special consideration.

An LCD panel is a matrix of pixels that are divided into rows and columns. These pixels are individually painted according to different signals and timing parameters, and you can control each pixel"s color individually. The panel is continuously refreshed, typically at around 60 Hz, from the contents of the frame buffer memory. Each memory location on the frame buffer corresponds to a pixel on the LCD panel.

A 1024 x 600 resolution display requires 614400 memory locations, with each location having a number of possible colors. The number of bits needed to describe the available colors is called bits per pixel (bpp). For example, 16 bpp can describe 65536 colors and 24 bits can describe 16777216 colors (known as true color). A panel with 614400 24-bit locations requires a 1800 KB frame buffer.

VSYNC: Vertical synch (FPFRAME, FLM, SPS or TV) indicates the end of the current frame. The next line index should restart at zero in the upper-left corner.

Every manufacturer provides display timings in a slightly different way and some provide more detail than others. Most LCD panels work with a range of timing parameters.

The i.MX6 IPUs define a series of frame buffer devices (/dev/fbN, where N is an index number starting at zero) that correspond to the graphical capabilities of the SoC.

The i.MX6 Dual/Quad has two IPUs, each containing two DIs. Additionally, the driver allows for an overlay frame buffer per IPU (to be displayed over the frame buffer of DI0). These overlay frame buffers are also represented by nodes /dev/fbN.

Frame buffer devices provide an abstraction for the graphics hardware. You must create a frame buffer entry on your platform"s device tree file and bind it to a graphics driver through the compatible property.

The following example creates a frame buffer and binds it to the MXC frame buffer device driver (drivers/video/mxc/mxc_ipuv3_fb.c).Frame buffer node binding to MXC graphics drivermxcfb1: fb@0 {

The driver"s binding documentation at Documentation/devicetree/bindings/fb/fsl_ipuv3_fb.txt describes additional properties for the frame buffer. You must complete the node with required and optional properties that match your hardware, for example:

You can create as many frame buffer entries as you have available display interfaces in your platform. For example, the i.MX6 Dual/Quad has two IPUs, each containing two display interfaces, equaling a total of four displays:

LCD displays must be created as nodes in the device tree with a display-timings subnode. Display timings binding documentation at Documentation/devicetree/bindings/video/display-timing.txt explains the required timing properties to describe an LCD.lcdname {

hfront-porch is the horizontal front porch, the number of clock pulses (pixels) between the last valid pixel data in the line and the next HSYNC pulse. According to the LCD data format, this value is zero.

vfront-porch is the vertical front porch, the number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse. According to the LCD data format, this value is zero.

NoteThe recommended timings from the LCD datasheet often do not work perfectly, as each platform introduces noise and delays that affect the display"s signals and timings.

vfront-porch is the vertical front porch, the number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse. The datasheet does not provide this number but it provides the complete Vertical period (TV) and the Vertical period (High) (TVd) so you can calculate the vertical front porch as TV - TVd = 831 - 800 = 311.

To run the application, call fbtest from a console. The application shows the test color chart by default to frame buffer 0 (/dev/fb0). To show the test color chart on a different frame buffer, export the variable FRAMEBUFFER:export FRAMEBUFFER=/dev/fb2

This color chart displays a white one-pixel frame at the edges of the LCD (which allows you to verify correct position and width/height), and gradients of red, green, blue, and white (which allow you to verify correct color depth and format).

The FBTFT drivers are now in the Linux kernel staging tree: https://git.kernel.org/cgit/linux/kernel/git/gregkh/staging.git/tree/drivers/staging/fbtft?h=staging-testing

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey