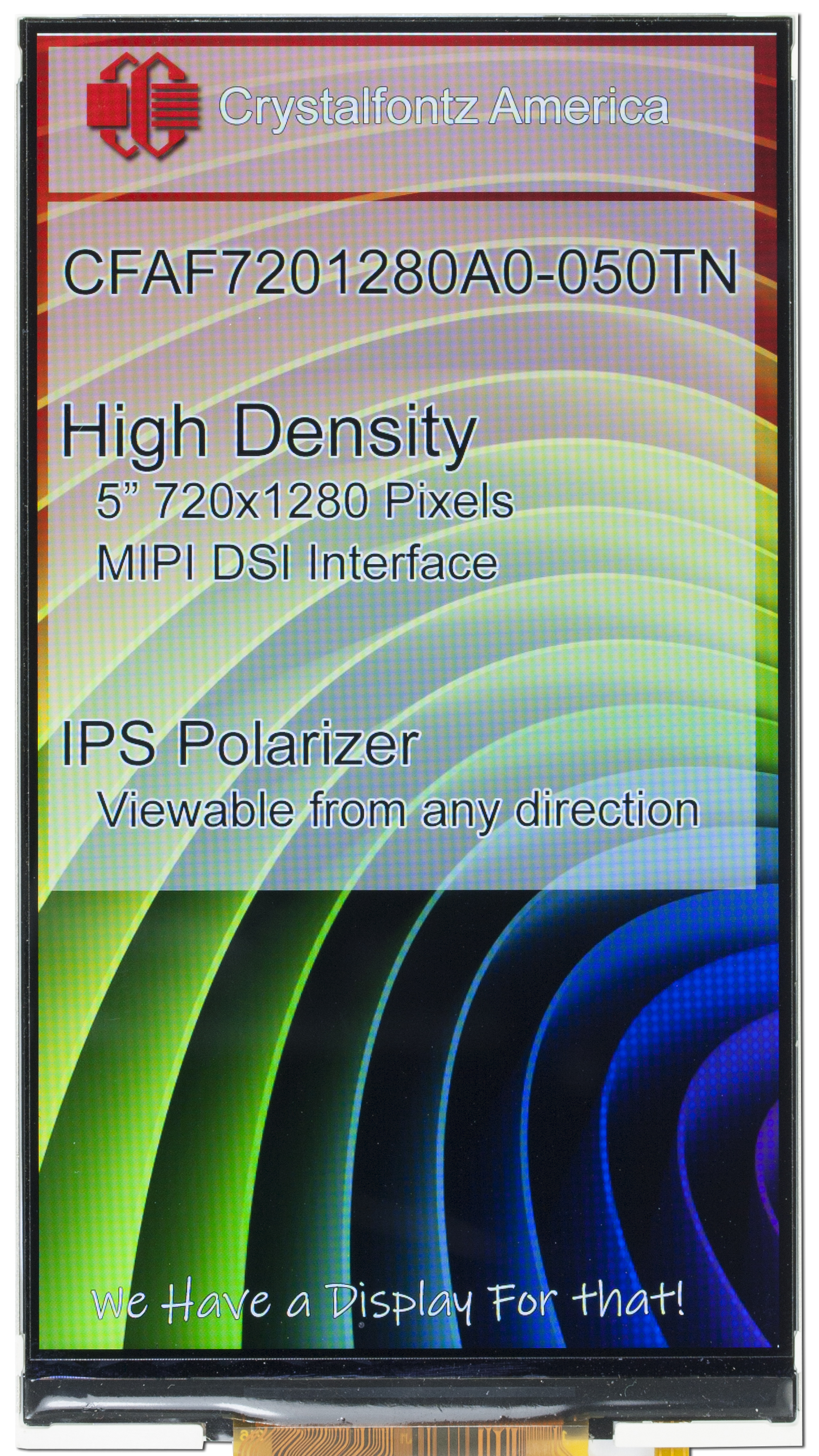

mipi dsi lcd display free sample

How many times did you start to plan a project and thought to yourself “if only I had a display that can fit within this design”? How many times did you alter the whole design because there were no displays available on the market that went with your idea?

If you’ve liked our standard display offer so far, you’ll be thrilled by what we can offer you now. It works like this: you send us your project information and display requirements, and we send you a free sample. Custom made and designed to fit perfectly within your project.

FIGURE 1. The MIPI Alliance has defined a plethora of interfaces for use in mobile devices. This article focuses on the Display Serial Interface (DSI) shown in the upper left corner.

The MIPI Alliance is a consortium of mobile device manufacturers and electronics components vendors that was established in 2003 to specify a common set of interfaces for various sub-systems within smartphones and similar multimedia devices. They have published a range of standards covering interfaces to audio, camera, display, touchscreen and other devices as shown in their infographic (Figure 1).

One of these, the Display Serial Interface, or DSI, standard is starting to appear on readily available microcontrollers (MCUs) and displays. I have recently embarked on my first project that uses this interface, so it’s worth sharing some of what I have learned in the process.

The DSI is a high-speed serial interface between a host processor and a display module. It is designed for low pin count, high bandwidth and low EMI. We will focus on the basic features of the DSI physical layer, called the D-PHY and touch briefly on the next layer up, the Display Command Set or DCS. Figure 2 shows two ways DSI can be used. It can operate in video mode where RGB pixel data and horizontal and vertical sync signals provided by the display controller are encoded into the serial stream by the DSI Host and decoded by the Device to drive the display glass. Alternatively, if the display controller and graphics RAM are integrated into the display, DSI can operate in command mode where data being written by the MCU into the RAM is encoded on the interface. In either mode commands from the DCS can be transmitted to configure the display.

FIGURE 2. The DSI interface can operate in two modes – video mode in which the pixel data and synchronization signals are streamed to the display in real-time, and command mode in which pixel data is written to the graphics RAM integrated with the display controller in the display module.

The two data lane zero line, D0P and D0N, can take one of four states, LP-00, LP-01, LP-10 and LP-11. Certain sequences of these states are used to switch between three possible modes – control mode, high-speed transmission, and escape mode. Control mode is the idle state from which the other states begin and end. On power-up the DSI is in control mode and the LP-11 idle state.

FIGURE 4. Commands can be sent over Data Lane 0 using LP data transmission by first sending an escape sequence and then a Low Power Transmission Entry Command. Data is then sent in long or short packets as described in the text. Such communication is usually used to initialize the display at power up.

There is a lot more to the MIPI DSI interface that we don’t have space for here. This overview has hopefully given you a flavour for this interesting interface. It is a lot more complex than the classic parallel RGB plus clock and sync signals, but it requires a lot fewer pins and is capable of much higher bandwidth and therefore driving larger, high resolution displays.

205 7 inch mipi dsi interface lcd display products are offered for sale by suppliers on Alibaba.com, of which lcd modules accounts for 68%, lcd touch screen accounts for 20%.

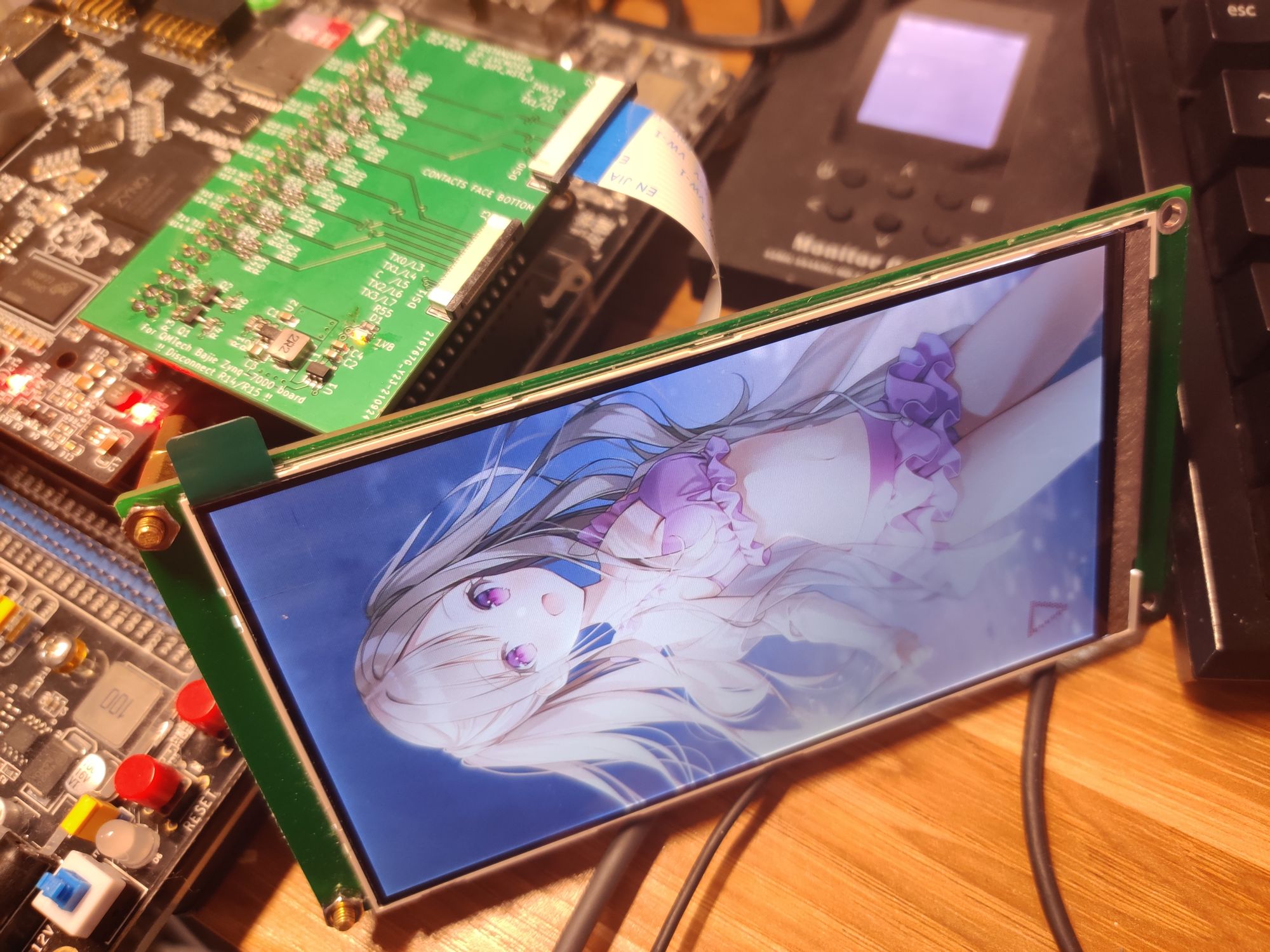

MIPI-DSI is the "latest" standard of mobile display, with highest bandwidth and low power consumption, it was quickly adopted by nearly every hardware vendors. Recently I discovered some really cheap DSI display modules, and decided to drive them the hard way by using a Zynq-7000 SoC.

The MIPI Alliance has kept their little secrets for years, exclusive to their organization members. The documentation provided by Xilinx and LCD manufacturers, however, gave me some basic clue of the specification of these mysterious standards.

MIPI D-PHY is the standard way which link layer protocols such as CSI-2 or DSI communicate with peripherals. A typical D-PHY transmitter or receiver has the following parts:PPI interface

The MIPI-DSI works on top of the D-PHY, provides the command and video interfaces to the host processor. There are two modes defined by the DSI specification, and panel manufacturers can select either or both modes to support.Command Mode

In HSDT mode, the data samples on each change of the clock lane(DDR clock), with LSBit shifting out first. The type of the packet is determined by the first byte of the packet, called Data Identification(DI). DI also has a Virtual Channel(VC) field, making lane sharing possible with maximum of 4 devices. However, display modules are only support VC 0. The last byte is a ECC byte calculated from the first 3 bytes. For example, the above packet has DI value 0x05, as a DCS short write command. The second packet is a special packet called End of Transmission Packet(EoTp), indicates the end of current transmission.

In DSI command mode, the host communicates with the peripheral by using different commands, including Display Command Set(DCS). If you have experience playing with some LCD or OLED display modules, you will find out that no matter which interface are used, some initialization sequence must be written to the module before it can function normally. These sequence contain the necessary drive voltage and clock settings, the type of the panel, the internal memory layout and many other parameters. For 4-line SPI or DBI(8080/6800 MCU interface) interfaces, commands are written by using a special signal called D/CX, which indicates the data currently being transmitted is a command or data. On MIPI-DSI, this is replaced with a command called DCS. Vendor specific command can be wrapped inside DCS packets, so the panel initialization process can be carried out by host.

Apart from traditional command based operations, DSI specification also has a Video Mode. In video mode, the host manage the display timing by sending out a stream of packets containing synchronization information and image data, then the display can retrive HSync/VSync/Blanking signal from these packets just like DPI(RGB panel interface) does. Video mode is capable of high bandwidth and smooth video, while some controllers without internal graphics RAM only supports this mode.

The board I planned to use is a Zynq-7020 board produced by QMTech, with the shunt resistors removed, external VCCO power can be provided by 2.54mm headers (Not every Zynq board has that) . I implemented the transmitter on a PCB, with power supplies for IOBANK and LCD, as well as the most common RaspberryPi compatible FPC socket. The impedance requirement for D-PHY is 100Ω differential and 50Ω single ended.

As this LCD controller (NovaTek NT35516) does not support command in HSDT mode, since Xilinx IP does not support Low Power Data Transmission (LPDT) either, I had to add an AXI GPIO and some glue logic to take over the bus for my bit-bang LPDT implementation.

The software part is quite routine, initialize a framebuffer in DDR, configure AXI framebuffer read IP to read from it and send the pixels through AXI Stream to MIPI DSI subsystem. Also, I implemented a bit-bang LPDT driver for the initialization process.

LCD can’t be driven with DC (Direct Current), it has to be driven with AC (Alternative Current) and the overall current has to be ZERO. Otherwise, the Liquid Crystal Material will be damaged sooner or later.

The Controller IC receives data written in ASCII or JIS code from the MPU and stores this data in RAM. This data is then converted into serial character patterns and transferred to the LCD driver IC.

RGB interface often been used in control large-scale high-resolution LCD display. It include 6/16/18bits data (like R0, R1, , , G0, G1, , ,B0, B1, , , ), VSYNC (Vertical synchronization), HSYNC (Horizontal synchronization).

Aimed at reducing the cost of display controllers in a mobile device. It is commonly targeted at LCD and similar display technologies. It defines a serial bus and a communication protocol between the host (source of the image data) and the device (destination of the image data)

DisplayPort (DP) is a digital display interface developed by a consortium of PC and chip manufacturers and standardized by the Video Electronics Standards Association (VESA). The interface is primarily used to connect a video source to a display device such as a computer monitor, and it can also carry audio, USB, and other forms of data.

DisplayPort was designed to replace VGA, DVI, and FPD-Link. The interface is backward compatible with other interfaces, such as HDMI and DVI, through the use of either active or passive adapters. It is mostly used for larger size and higher resolution displays.

HDMI (High-Definition Multimedia Interface) is a proprietary audio/video interface for transmitting uncompressed video data and compressed or uncompressed digital audio data from an HDMI-compliant source device, such as a display controller, to a compatible computer monitor, video projector, digital television, or digital audio device. HDMI is a digital replacement for analog video standards.

6) Power on the Raspberry Pi and wait for a few seconds until the LCD displays normally. And the touch function can also work after the system starts.

The Display Serial Interface (DSI) is a specification by the Mobile Industry Processor Interface (MIPI) Alliance aimed at reducing the cost of display controllers in a mobile device. It is commonly targeted at LCD and similar display technologies. It defines a serial bus and a communication protocol between the host, the source of the image data, and the device which is the destination. The interface is closed source, which means that the specification of the interface is not open to the public. The maintenance of the interface is the responsibility of the MIPI Alliance. Only legal entities (e.g. companies) can be members. These members or the persons commissioned and approved by them have access to the specification in order to use it in their possible applications.

At the physical layer, DSI specifies a high-speed (e.g. 4.5Gbit/s/lane for D-PHY 2.0differential signaling point-to-point serial bus. This bus includes one high speed clock lane and one or more data lanes. Each lane is carried on two wires (due to differential signaling). All lanes travel from the DSI host to the DSI device, except for the first data lane (lane 0), which is capable of a bus turnaround (BTA) operation that allows it to reverse transmission direction. When more than one lane is used, they are used in parallel to transmit data, with each sequential bit in the stream traveling on the next lane. That is, if 4 lanes are being used, 4 bits are transmitted simultaneously, one on each lane. The link operates in either low power (LP) mode or high speed (HS) mode. In low power mode, the high speed clock is disabled and signal clocking information is embedded in the data. In this mode, the data rate is insufficient to drive a display, but is usable for sending configuration information and commands. High speed mode enables the high speed clock (at frequencies from tens of megahertz to over one gigahertz) that acts as the bit clock for the data lanes. Clock speeds vary by the requirements of the display. High speed mode is still designed to reduce power usage due to its low voltage signaling and parallel transfer ability.

The communication protocol describes two sets of instructions. The Display Command Set (DCS) is a set of common commands for controlling the display device, and their format is specified by the DSI standard. It defines registers that can be addressed and what their operation is. It includes basic commands such as sleep, enable, and invert display. The Manufacturer Command Set (MCS) is a device-specific command space whose definition is up to the device manufacturer. It often includes commands required to program non-volatile memory, set specific device registers (such as gamma correction), or perform other actions not described in the DSI standard. The packet format of both sets is specified by the DSI standard. There are Short and Long Packets, Short Packet is 4 bytes long; Long Packet can be of any length up to 216 bytes. Packets are composed of a DataID, Word count, Error Correction Code (ECC), Payload and Checksum (CRC). Commands that require reading data back from the device trigger a BTA event, which allows the device to reply with the requested data. A device cannot initiate a transfer; it can only reply to host requests.

Image data on the bus is interleaved with signals for horizontal and vertical blanking intervals (porches). The data is drawn to the display in real time and not stored by the device. This allows the manufacture of simpler display devices without frame buffer memory. However, it also means that the device must be continuously refreshed (at a rate such as 30 or 60 frames per second) or it will lose the image. Image data is only sent in HS mode. When in HS mode, commands are transmitted during the vertical blanking interval.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey