tft display structure free sample

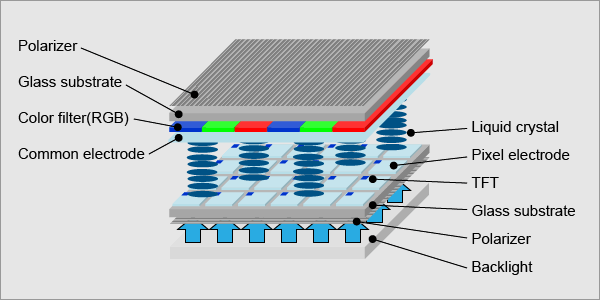

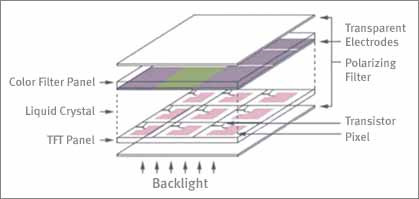

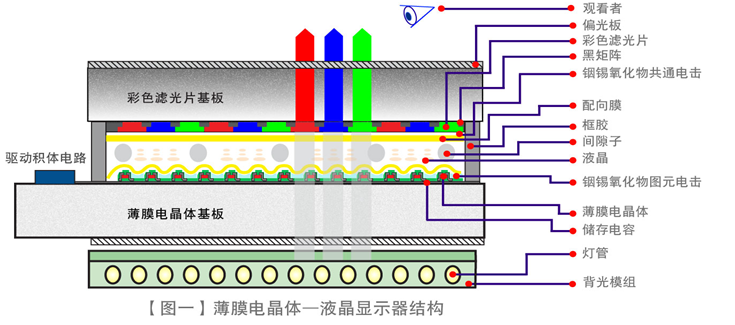

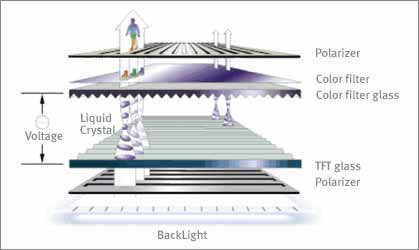

TFT LCD screen is mainly composed of three parts: rear panel module, LCD layer and front panel module. A layer of liquid crystal is sandwiched between two glass substrates. A color filter is attached to the front LCD panel, and a thin film transistor (TFT) is made on the back TFT panel. When a voltage is applied to the transistor, the liquid crystal turns, and light passing through the liquid crystal produces pixels on the front panel. As shown in the figure:

The rear plate module refers to the part behind the liquid crystal layer, which is mainly composed of the rear polarizer , the rear glass layer, the pixel unit (pixel electrode, TFT tube), the rear directional film, etc.

The rear glass substrate is divided into many tiny grids, called pixel units (or sub-pixels), by a number of transparent metal film wires arranged horizontally and vertically and insulated from each other. Each cell has a transparent metal film electrode, called the pixel electrode, which is insulated from the surrounding wire. One corner of the pixel electrode is connected with two vertical and horizontal wires through a TFT thin film field effect tube made on glass substrate by printing method to form a matrix structure:

The gate of the TFT field effect tube is connected with the horizontal line, the horizontal line is called the gate scan line or the X electrode, because it plays the role of TFT pass selection, also called the pass selection line; The source pole of the TFT tube is connected with the vertical line, which is called the source line or Y electrode. The drain of the TFT is integrated with the transparent pixel electrode. The function of the TFT tube is a switch tube, using the gate voltage applied to the TFT switch tube, can control the conduction and cut-off of the TFT switch tube.

The LCD screen has a pixel electrode and a thin film transistor (TFT) on the rear glass plate, and a color filter on the front glass plate. The liquid crystal layer is sandwiched between the front and back glass layers.

For TFT LCD screen, each pixel unit can be regarded as a layer of TN liquid crystal sandwiched between the pixel electrode and the common electrode. The liquid crystal layer can be equivalent to a liquid crystal capacitor (CLc), whose size is about 0.1pF. In practice, this capacitor cannot hold the voltage until the next time the picture data is updated, that is, when the TFT tube is fully charged to this capacitor, it cannot hold the voltage until the next time the TFT tube is charged to this point (at the usual 60Hz picture update frequency, it needs to hold the voltage for about 16ms). As a result, if the voltage changes, the gray scale will be incorrect. Therefore, when designing the panel, a storage capacitor Cs (usually formed by the wiring of the pixel electrode and the common electrode) will be added, with a value of about 0.5pF, so that the charged voltage can be maintained until the next image updated.

Red, blue, and green are the so-called three primary colors. That is to say, with these three colors, different colors can be mixed together. The three RGB colors are divided into three independent units, each of which has different gray-scale changes. Then the three adjacent RGB display units are taken as a basic display unit — pixel, and the pixel can have different color changes.

In the figure, the black part between each RGB point, called the black-matrix, is mainly used to cover the part that is not intended to transmit light, such as the pixel electrode wire, TFT tube, etc.

In this Arduino touch screen tutorial we will learn how to use TFT LCD Touch Screen with Arduino. You can watch the following video or read the written tutorial below.

As an example I am using a 3.2” TFT Touch Screen in a combination with a TFT LCD Arduino Mega Shield. We need a shield because the TFT Touch screen works at 3.3V and the Arduino Mega outputs are 5 V. For the first example I have the HC-SR04 ultrasonic sensor, then for the second example an RGB LED with three resistors and a push button for the game example. Also I had to make a custom made pin header like this, by soldering pin headers and bend on of them so I could insert them in between the Arduino Board and the TFT Shield.

Here’s the circuit schematic. We will use the GND pin, the digital pins from 8 to 13, as well as the pin number 14. As the 5V pins are already used by the TFT Screen I will use the pin number 13 as VCC, by setting it right away high in the setup section of code.

I will use the UTFT and URTouch libraries made by Henning Karlsen. Here I would like to say thanks to him for the incredible work he has done. The libraries enable really easy use of the TFT Screens, and they work with many different TFT screens sizes, shields and controllers. You can download these libraries from his website, RinkyDinkElectronics.com and also find a lot of demo examples and detailed documentation of how to use them.

After we include the libraries we need to create UTFT and URTouch objects. The parameters of these objects depends on the model of the TFT Screen and Shield and these details can be also found in the documentation of the libraries.

So now I will explain how we can make the home screen of the program. With the setBackColor() function we need to set the background color of the text, black one in our case. Then we need to set the color to white, set the big font and using the print() function, we will print the string “Arduino TFT Tutorial” at the center of the screen and 10 pixels down the Y – Axis of the screen. Next we will set the color to red and draw the red line below the text. After that we need to set the color back to white, and print the two other strings, “by HowToMechatronics.com” using the small font and “Select Example” using the big font.

Established in 2010, Topfoison has devoted itself to the manufacturing and development of high-quality products for the Wearable device, Smart Watch, VR, Medical device, Industrial LCD display including Color LCD modules/OLED/LCD display/Round lcd screen/Round AMOLED/ Square transflective lcd screen/ IPS full wide display/ 1080p fhd AMOLED and 2K 1440p lcd. Topfoison focus on1.22-7.0 inch small size displays, all the products produced in our company enjoys the most advanced production craft and technology as well as the strictly ISO quality management system.

A TFT LCD, or a thin film transistor liquid crystal display, is one of the fastest growing forms of display technology today. The thin film transistor (TFT) is a type of semiconductor device used in display technology to enhance efficiency, compactness, and cost of the product. In conjunction with its semiconductor properties, the TFT LCD is an active matrix display, controlling pixels individually and actively rather than passively, furthering the benefits of this semiconductor device.

The TFT LCD is built with three key layers. Two sandwiching layers consist of glass substrates, though one includes TFTs while the other has an RGB, or red green blue, color filter. The layer between the glass layers is a liquid crystal layer.

The Architecture of a TFT Pixelbelow) from the other substrate layer of the device and control the amount of voltage applied to their respective sub-pixels. This layer also has pixel electrodes between the substrate and the liquid crystal layer. Electrodes are conductors that channel electricity into or out of something, in this case, pixels.

Between the two substrate layers lie liquid crystals. Together, the liquid crystal molecules may behave as a liquid in terms of movement, but it holds its structure as a crystal. There are a variety of chemical formulas available for use in this layer. Typically, liquid crystals are aligned to position the molecules in a certain way to induce specific behaviors of passing light through the polarization of the light waves. To do this, either a magnetic or electric field must be used; however, with displays, for a magnetic field to be usable, it will be too strong for the display itself, and thus electric fields, using very low power and requiring no current, are used.

Before applying an electric field to the crystals between the electrodes, the alignment of the crystals is in a 90 degree twisted pattern, allowing a properly crystal-polarized light to pass through the surface polarizer in a display’s “normal white” mode. This state is caused by electrodes that are purposely coated in a material that orients the structure with this specific twist.

However, when the electric field is applied, the twist is broken as the crystals straighten out, otherwise known as re-aligning. The passing light can still pass through the back polarizer, but because the crystal layer does not polarize the lights to pass through the surface polarizer, light is not transmitted to the surface, thus an opaque display. If the voltage is lessened, only some crystals re-align, allowing for a partial amount of light to pass and creating different shades of grey (levels of light). This effect is called the twisted nematic effect.

Fig. 3:The top row characterizes the nature of alignment in using IPS as well as the quality of viewing angles. The bottom row displays how the twisted nematic is used to align the crystals and how viewing angles are affected by it.

The light that passes through the device is sourced from the backlight which can shine light from the back or the side of the display. Because the LCD does not produce its own light, it needs to use the backlight in the OLED) have come into use as well. Typically white, this light, if polarized correctly, will pass through the RGB color filter of the surface substrate layer, displaying the color signaled for by the TFT device.

A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display that uses thin-film-transistor technologyactive matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven (i.e. with segments directly connected to electronics outside the LCD) LCDs with a few segments.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968. In 1971, Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated a 2-by-18 matrix display driven by a hybrid circuit using the dynamic scattering mode of LCDs.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).active-matrix liquid-crystal display (AM LCD) using CdSe TFTs in 1974, and then Brody coined the term "active matrix" in 1975.high-resolution and high-quality electronic visual display devices use TFT-based active matrix displays.

The liquid crystal displays used in calculators and other devices with similarly simple displays have direct-driven image elements, and therefore a voltage can be easily applied across just one segment of these types of displays without interfering with the other segments. This would be impractical for a large display, because it would have a large number of (color) picture elements (pixels), and thus it would require millions of connections, both top and bottom for each one of the three colors (red, green and blue) of every pixel. To avoid this issue, the pixels are addressed in rows and columns, reducing the connection count from millions down to thousands. The column and row wires attach to transistor switches, one for each pixel. The one-way current passing characteristic of the transistor prevents the charge that is being applied to each pixel from being drained between refreshes to a display"s image. Each pixel is a small capacitor with a layer of insulating liquid crystal sandwiched between transparent conductive ITO layers.

The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. However, rather than fabricating the transistors from silicon, that is formed into a crystalline silicon wafer, they are made from a thin film of amorphous silicon that is deposited on a glass panel. The silicon layer for TFT-LCDs is typically deposited using the PECVD process.

Polycrystalline silicon is sometimes used in displays requiring higher TFT performance. Examples include small high-resolution displays such as those found in projectors or viewfinders. Amorphous silicon-based TFTs are by far the most common, due to their lower production cost, whereas polycrystalline silicon TFTs are more costly and much more difficult to produce.

The twisted nematic display is one of the oldest and frequently cheapest kind of LCD display technologies available. TN displays benefit from fast pixel response times and less smearing than other LCD display technology, but suffer from poor color reproduction and limited viewing angles, especially in the vertical direction. Colors will shift, potentially to the point of completely inverting, when viewed at an angle that is not perpendicular to the display. Modern, high end consumer products have developed methods to overcome the technology"s shortcomings, such as RTC (Response Time Compensation / Overdrive) technologies. Modern TN displays can look significantly better than older TN displays from decades earlier, but overall TN has inferior viewing angles and poor color in comparison to other technology.

Most TN panels can represent colors using only six bits per RGB channel, or 18 bit in total, and are unable to display the 16.7 million color shades (24-bit truecolor) that are available using 24-bit color. Instead, these panels display interpolated 24-bit color using a dithering method that combines adjacent pixels to simulate the desired shade. They can also use a form of temporal dithering called Frame Rate Control (FRC), which cycles between different shades with each new frame to simulate an intermediate shade. Such 18 bit panels with dithering are sometimes advertised as having "16.2 million colors". These color simulation methods are noticeable to many people and highly bothersome to some.gamut (often referred to as a percentage of the NTSC 1953 color gamut) are also due to backlighting technology. It is not uncommon for older displays to range from 10% to 26% of the NTSC color gamut, whereas other kind of displays, utilizing more complicated CCFL or LED phosphor formulations or RGB LED backlights, may extend past 100% of the NTSC color gamut, a difference quite perceivable by the human eye.

In 2004, Hydis Technologies Co., Ltd licensed its AFFS patent to Japan"s Hitachi Displays. Hitachi is using AFFS to manufacture high end panels in their product line. In 2006, Hydis also licensed its AFFS to Sanyo Epson Imaging Devices Corporation.

A technology developed by Samsung is Super PLS, which bears similarities to IPS panels, has wider viewing angles, better image quality, increased brightness, and lower production costs. PLS technology debuted in the PC display market with the release of the Samsung S27A850 and S24A850 monitors in September 2011.

TFT dual-transistor pixel or cell technology is a reflective-display technology for use in very-low-power-consumption applications such as electronic shelf labels (ESL), digital watches, or metering. DTP involves adding a secondary transistor gate in the single TFT cell to maintain the display of a pixel during a period of 1s without loss of image or without degrading the TFT transistors over time. By slowing the refresh rate of the standard frequency from 60 Hz to 1 Hz, DTP claims to increase the power efficiency by multiple orders of magnitude.

Due to the very high cost of building TFT factories, there are few major OEM panel vendors for large display panels. The glass panel suppliers are as follows:

External consumer display devices like a TFT LCD feature one or more analog VGA, DVI, HDMI, or DisplayPort interface, with many featuring a selection of these interfaces. Inside external display devices there is a controller board that will convert the video signal using color mapping and image scaling usually employing the discrete cosine transform (DCT) in order to convert any video source like CVBS, VGA, DVI, HDMI, etc. into digital RGB at the native resolution of the display panel. In a laptop the graphics chip will directly produce a signal suitable for connection to the built-in TFT display. A control mechanism for the backlight is usually included on the same controller board.

The low level interface of STN, DSTN, or TFT display panels use either single ended TTL 5 V signal for older displays or TTL 3.3 V for slightly newer displays that transmits the pixel clock, horizontal sync, vertical sync, digital red, digital green, digital blue in parallel. Some models (for example the AT070TN92) also feature input/display enable, horizontal scan direction and vertical scan direction signals.

New and large (>15") TFT displays often use LVDS signaling that transmits the same contents as the parallel interface (Hsync, Vsync, RGB) but will put control and RGB bits into a number of serial transmission lines synchronized to a clock whose rate is equal to the pixel rate. LVDS transmits seven bits per clock per data line, with six bits being data and one bit used to signal if the other six bits need to be inverted in order to maintain DC balance. Low-cost TFT displays often have three data lines and therefore only directly support 18 bits per pixel. Upscale displays have four or five data lines to support 24 bits per pixel (truecolor) or 30 bits per pixel respectively. Panel manufacturers are slowly replacing LVDS with Internal DisplayPort and Embedded DisplayPort, which allow sixfold reduction of the number of differential pairs.

The bare display panel will only accept a digital video signal at the resolution determined by the panel pixel matrix designed at manufacture. Some screen panels will ignore the LSB bits of the color information to present a consistent interface (8 bit -> 6 bit/color x3).

With analogue signals like VGA, the display controller also needs to perform a high speed analog to digital conversion. With digital input signals like DVI or HDMI some simple reordering of the bits is needed before feeding it to the rescaler if the input resolution doesn"t match the display panel resolution.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

K. H. Lee; H. Y. Kim; K. H. Park; S. J. Jang; I. C. Park & J. Y. Lee (June 2006). "A Novel Outdoor Readability of Portable TFT-LCD with AFFS Technology". SID Symposium Digest of Technical Papers. AIP. 37 (1): 1079–82. doi:10.1889/1.2433159. S2CID 129569963.

Kim, Sae-Bom; Kim, Woong-Ki; Chounlamany, Vanseng; Seo, Jaehwan; Yoo, Jisu; Jo, Hun-Je; Jung, Jinho (15 August 2012). "Identification of multi-level toxicity of liquid crystal display wastewater toward Daphnia magna and Moina macrocopa". Journal of Hazardous Materials. Seoul, Korea; Laos, Lao. 227–228: 327–333. doi:10.1016/j.jhazmat.2012.05.059. PMID 22677053.

TFT LCD image retention we also call it "Burn-in". In CRT displays, this caused the phosphorus to be worn and the patterns to be burnt in to the display. But the term "burn in" is a bit misleading in LCD screen. There is no actual burning or heat involved. When you meet TFT LCD burn in problem, how do you solve it?

Burn in is a noticeable discoloration of ghosting of a previous image on a display. It is caused by the continuons drive of certain pixels more than other pixels. Do you know how does burn in happen?

When driving the TFT LCD display pixels Continously, the slightly unbalanced AC will attract free ions to the pixels internal surface. Those ions act like an addition DC with the AC driving voltage.

Those burn-in fixers, screen fixer software may help. Once the Image Retention happened on a TFT, it may easy to appear again. So we need to take preventive actions to avoid burn in reappearing.

For normal white TFT LCD, white area presenting minimal drive, black area presenting maximum drive. Free ions inside the TFT may are attracted towards the black area (maximum drive area)

When the display content changed to full screen of 128(50%) gray color, all the area are driving at the same level. Those ions are free again after a short time;

The TFT F display series are extra flat TFT displays with high graphic resolution, which can be installed horizontally and vertically. In addition to floor designations and direction arrows, special displays can also be shown as full and partial image, elevator data, logos, slide show and running text.

The information is displayed in the TFT F via widgets that can be freely positioned. More about the configuration via the SCHAEFER Configurator can be found in the manual chapter 4.

The internal menu of the device can be operated via three keys on the back of the display. For more information on the internal menu, please refer to the manual chapter 4.6.5.

Dr Pan: Hello, Greg. TFT LCD module is one of the best LCD technology. We can simply consider it as TFT+LCD+LED backlight, and monochrome LCD module consists of LCD+LED backlight. An image on an LCD we can see is composed of pixels. TFT is the abbreviation for thin film transistor and it controls the R, G, B colors of each pixel respectively on the surface of LCD.

TFT LCD is a high standard product and it is not well customized as monochrome LCD. But still, it has a variety of options to meet the customers’ requirements.The sizes range from 1.44 inch to 130.0 inch;

Figures 3a–d show optical and SEM (scanning electron microscopy) images of the fabricated CL and CLSE pixel structures. Each structure has the same pixel size (80 μm × 240 μm) and minimum pattern size (5 μm). As shown in Fig. 3d, the white line patterns are the ITO interdigitated pixel and common electrodes. They are well connected to the source electrode and gate line via through holes, and the common electrodes at both ends cover the underlying data lines to prevent electrical noise from being applied to the LC layer. As will be shown later, this noise shield electrode (SE) is what makes the black matrix above the data line unnecessary

Optical and SEM (scanning electron microscopy) images of fabricated (a, b) CL and (c, d) CLSE pixel structures. The five white line patterns in (d) are the ITO interdigitated pixel and common electrodes. (e) Images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel. (f) The three-black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM) and (g) optical images of pixels without BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines).

Figure 3e shows images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel fabricated in our laboratory, (f) the three black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM), and (g) optical images of panel areas without the BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines). As can be seen in the image from the normal direction, the brightness and contrast of the display area with the top BM and middle BM patterns are almost the same, but the contrast of the display area without the BM is relatively lower because of the lower darkness level of the LC off pixels indicating “HITACHI”. As shown in Fig. 3g, this is due to light leaking through the aperture between the data line and adjacent common lines. Therefore, in the CL structure, the BM on the drain line is necessary to obtain a high contrast ratio by shielding light leakage. This is the same as in the conventional structure. On the contrary, there is no light leakage along the gate line through the gaps between the gate line and edges of the pixel/common electrodes, as is clearly shown in Fig. 3g. This is a unique advantage of the CL structure because the conventional structure must shield these gaps with the BM to prevent light leakage. The suppression of light leakage along the gate line in the CL structure is due to the driving scheme (see Fig. 2b,a for a comparison with the conventional structure). During the holding period (tOFF) in the conventional structure, regardless of the pixel voltage, Vp (including Vp = 0), nonzero Vgp and Vgc are always applied to keep the TFT off, and these voltages are applied to the LC layer, inducing light leakage as reported in

Figure 4a shows the gate voltage (Vg) dependence of the panel brightness, while the inset shows that of the TFT current (transfer characteristics). The gray curves are for the conventional IPS TFT-LCD with the TFT before enhancement, the common line, and the matrix BM (MBM) shown at the top of Fig. 3f. The blue curves are for the proposed CL structure with the enhanced TFT and the stripe BM (SBM) shown in the middle of Fig. 3f. In this case, enhanced TFT characteristics were obtained by using an MNOS TFT without back-channel oxidation that was enhanced by the BTS process. In both structures, the threshold voltages for panel brightness, defined by extrapolating the straight part of the brightness curves, reflect those of the TFT transfer curves defined as Vg at a drain current of 10−12 A, and they are well matched to be 4 V and 9 V, respectively. The maximum brightness for the CL structure is 137% higher than that for the conventional structure, which is due to the increase in the aperture ratio from 38 to 52% that results from the elimination of the common line and the BM covering the gate line.

(a) Dependence of panel brightness and TFT current on gate voltage for the conventional pixel structure of 38% aperture ratio (AR) with matrix black matrix (MBM) over both drain and gate lines and proposed CL pixel structure of 52% AR with strip black matrix (SBM) over only the drain lines. Transfer characteristics before and after bias temperature stress (BTS) treatment are shown in the inset. (b) Charging and (c) holding characteristics of enhanced TFT of the CL structure with gate as a common line. Vg and Vd in the TFT ON state are 30 V and +/−7 V, respectively.

To estimate the charging and holding characteristics of the MNOS-enhanced TFT in the panel, the gate TFT ON and OFF time dependences of the panel brightness were measured (Fig. 4b,c). The charging characteristics in Fig. 4b are plotted as a function of tON at tOFF = 16.6 ms, Vg = 30 V, and Vd = ± 7 V. The holding characteristics in Fig. 4c are plotted as a function of tOFF at tON = 34 μs. 95.1% charging at tON = 34 μs and 95.3% holding at tOFF = 16.6 ms indicate that the enhanced TFT has sufficient charging and holding performance to drive a standard VGA (640 × 480 pixels) panel (the number of scanning lines is estimated as tOFF/tON = 16.6/0.034 = 488).

To confirm the driving conditions for the CL structure without the BM along the gate line (with the SBM), the tOFF dependence of the contrast ratio (CR) in the CL panel was further investigated as shown in Fig. 5a, where CR is plotted as a function of tOFF for the CL panels with the matrix BM (MBM) and the strip BM (SBM). The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. The SBM and MBM panels keep CR higher than 240 with tOFF > 16.6 ms, the frame period of a display panel without flicker being noticeable to the human eye. both panels decrease CR when tOFF is less than 16.6 ms; the CR of the SBM panel decreases faster than the CR of the MBM panel. As shown in the inset, the decrease in CR was due to the increase in dark-state brightness with decreasing tOFF as light leakage increases along the gate line. This light leakage is induced by the voltage Vgp = Vgc = VgON = 30 V applied only for 34 μs during the TFT ON (charging) state, which is 1/488th the duration, tOFF = 16.6 ms, of the TFT OFF (holding) state with Vgp = Vgc = VgOFF = 0 V, but the ratio increases with decreasing tOFF and becomes effective enough to switch on LC layer and induce light leakage. However, it should be stressed again that the CL panel with the normal holding (TFT OFF) time of 16.6 ms does not suffer from the light leakage along the gate line, so the aperture ratio can be increased by removing the BM along the gate line.

(a) Contrast ratio (CR) for CL panels with matrix BM (MBM) and stripe BM (SBM) plotted as a function of tOFF. The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. Vd (= VLC) dependence of (b) brightness and (c) contrast ratio of the CLSE panel. Insets of (b): optical images indicating the elimination of the BM from the CLSE structure (upper left) and the MBM in the conventional structure (lower right). Insets of (c): CLSE panel composed of different areas with three different pixel structures and aperture ratios (ARs), i.e., CLSE structure without BM (60%), CL structure with SBM (52%), and conventional structure with MBM (38%).

Figure 5b,c shows the Vd (= VLC) dependence of the brightness and contrast ratio of the CLSE panel without a BM along the drain line and along the gate line. As shown in the optical images in the insets of Fig. 5c, the CLSE panel has different areas with three different pixel structures and aperture ratios (ARs), i.e., the CLSE structure without the BM (60%), the CL structure with the SBM (52%), and the conventional structure with the MBM (38%). The optical images in the inset of Fig. 5b clearly indicate the elimination of the BM from the CLSE structure and the MBM in the conventional structure. The ratios of the bright area in the CLSE and conventional pixels shown in the red dotted square appear higher than the aperture ratios because the pixel and common electrodes are invisible due to the brightness. The brightness and contrast ratio in each area increase with increasing Vd; the ratios for the CLSE structure without the BM are approximately 160% those of the conventional structure with the MBM, reflecting the difference in aperture ratio.

Figure 6 indicates the effect of bias temperature stress (BTS) on the TFT characteristics. As the stressing time, tS, of the positive gate stress voltage, Vst = + 77 V, increases from 0 to 3600 s, the transfer (Id-Vg) curve shifts in the positive direction (Fig. 6a). Vth is defined as Vg at which Id = 10−12 A and ΔVth is defined as the Vth shift from the initial value via BTS. As shown in Fig. 6b, ΔVth increases logarithmically with increasing tS: ΔVth = 2.17 + 4.93 × log (tS). The mechanism behind the gate-stress-induced Vth shift is electron tunnel injection from the a-Si:H semiconductor into the SiOx gate insulator. For confirmation, ΔVth of MNOS TFTs with different SiOx thicknesses is plotted as a function of the electric field applied to the SiOx layer in Fig. 6c. Here, the thickness of the SiOx was varied (5, 10, 20, 50 nm), while the SiN thickness was fixed at 200 nm. The electric field applied to SiOx, Eox, was calculated using the following equation,

Effect of bias temperature stress (BTS) on TFT characteristics. (a) The transfer (Id–Vg) curve shifts in the positive direction with positive gate bias stress of Vst = + 77 V over the duration of 0–3600 s. (b) ΔVth, defined as the Vth shift from the initial value via BTS, increases logarithmically with increasing tS, following ΔVth = 2.17 + 4.93 × log (tS). (c) ΔVth of MNOS TFTs with different SiOx thicknesses from 5 to 50 nm as a function of the electric field applied to the SiOx layer.

Figure 7a shows the effect of back-channel oxidation (BCO) and passivation (PAS) on the Id-Vg characteristics of the MNOS TFT. The Id-Vg curve with Vth = 5.1 V is further enhanced to Vth = 10.9 V after BCO, although there is a slight degradation of the slope of the current increase in the sub-threshold region. The slope recovers after PAS without any change to the enhanced characteristics

(a) Effect of back-channel oxidation (BCO) and passivation (PAS) on Id–Vg characteristics of MNOS TFT. (b) Vth and Vth standard deviation, σVth, after BTS and after BCO without BTS treatments and (c) SiOX thickness as a function of position along gate-line, x.

The advantage of BCO over BTS is the uniformity of the enhanced characteristics; Fig. 7b shows the distribution of the enhanced Vth as a function of position along gate-line, x, for the MNOS TFTs connected with a 90-mm-long gate line in the TFT substrate after BTS and BCO treatments. The average value of Vth and the standard deviation, σVth, for pristine TFTs before BTS or BCO, are 5.1 V and 0.35 V, respectively. After BCO, Vth is uniformly enhanced, with an average Vth = 11 V and σVth = 0.4 V without increasing σVth. On the other hand, after BTS, Vth is nonuniformly enhanced with an average Vth = 9.3 V and σVth of 1.4 V. In particular, Vth increases linearly as a function of position along gate-line, x. As the gate SiOx thickness linearly decreases, from (54 nm) to (47 nm) with increasing x as shown in Fig. 7c, the increase in ΔVth after BTS with x is due to increase in the electric field applied to SiOx as shown in Fig. 6c and Eq. 1.

It has been shown that the Vth of the MNOS TFT is independent of the gate SiOx thickness when the thickness is more than 5 nm8a, Vth of the MNOS TFT with the BCO treatment becomes almost independent of the BCO SiOx thickness. As shown in the inset, the thickness of BCO SiOx composed of oxidized a-Si:H linearly increases with BCO processing time, and the Vth increase almost saturates at a BCO SiOx thickness greater than 5 nm. Therefore, the enhanced MNOS TFT after BCO has a uniformly high Vth that is robust to thickness fluctuations of the gate and BCO SiOx layers. BCO also has an advantage over BTS in terms of the stability of Vth as shown in Fig. 8b, which plots the annealing time dependence of Vth for BCO and BTS. In this experiment, the stoichiometry (x) of the gate SiOx was 1.78 for BTS and 1.78 and 1.9 for BCO. The annealing temperature in the N2 atmosphere was 200 °C. In the case of BTS, Vth decreased to the pristine value after approximately 5 h of annealing, while Vth decreased more slowly in the case of BCO. In particular, the annealing time required for Vth to fall to 7 V was 7.5 times longer than that of BTS. Increasing the stoichiometry (x) of the gate SiOx dramatically improved the BCO-enhanced Vth to as much as 11 V, which was stably maintained after 24 h of annealing at 200 °C.

(a) Dependence of Vth on thickness of back-channel oxidized (BCO) SiOX. The inset shows the SiOx thickness dependence on the BCO process time for RF powers of 200 W and 500 W. (b) Stability of Vth as a function of annealing time for three different TFTs with gate SiOx stoichiometry, x = 1.78 and bias temperature stress (BTS), x = 1.78 and BCO, and x = 1.9 and BCO. The temperature of annealing in the N2 atmosphere was 200 °C. (c) Band diagram of back-channel oxidized MNOS TFT. The red arrows show the electric dipoles at the SiOX/a-Si:H and a-Si:H/BCO SiOX interfaces.

A schematic band model for the MNOS TFT with the BCO treatment and the sectional structure of the interface between the a-Si:H and gate and BCO SiOx are shown in Fig. 8c. The uniformly high Vth that is independent of SiOx thickness is due to the dipoles generated at the channel and back-channel interfaces between a-Si:H and SiOx8 of reference

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey