lcd panel side cof data made in china

This website is using a security service to protect itself from online attacks. The action you just performed triggered the security solution. There are several actions that could trigger this block including submitting a certain word or phrase, a SQL command or malformed data.

This website is using a security service to protect itself from online attacks. The action you just performed triggered the security solution. There are several actions that could trigger this block including submitting a certain word or phrase, a SQL command or malformed data.

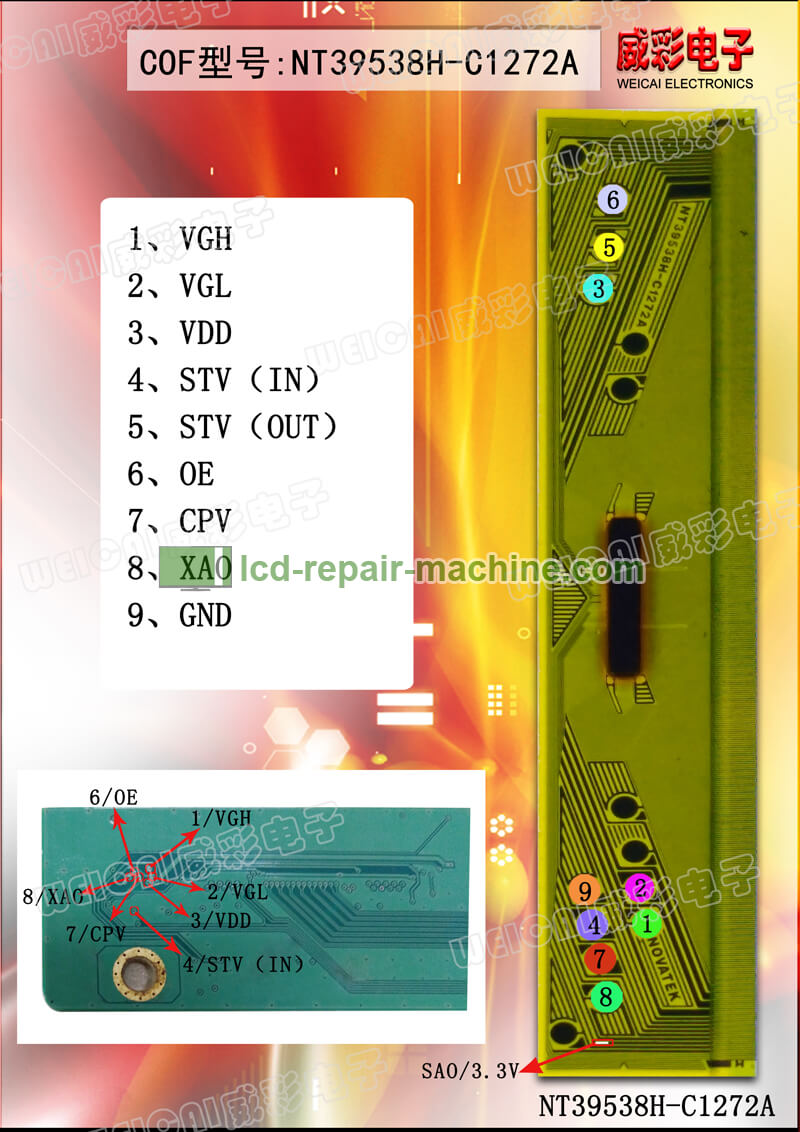

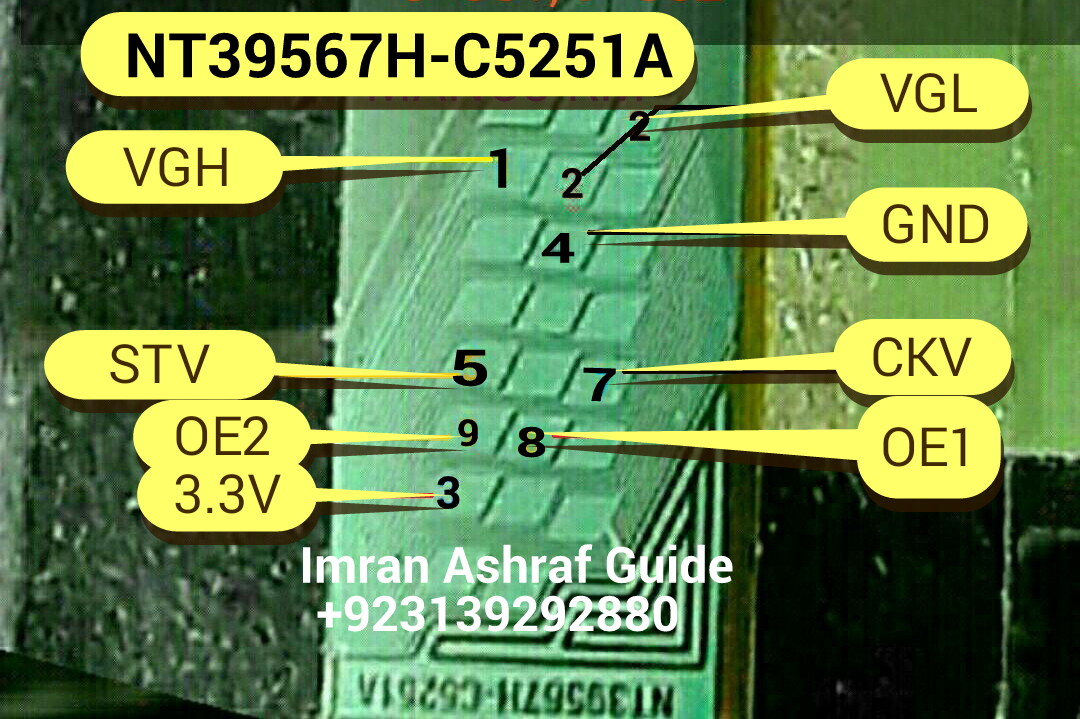

飞线图点位图 边板ST315A05-C-XC-2支持边板到Y全飞线 Panel ST5461D04-1-XR2 T-con Board Voltages and Testing Guide Full Video COF T370XW02 T400HW04 V2 S6CG331-58 COF DATA 57618 CF12 COF DATA Job Done after successful Bypass RM76A30FA-906 Cof Data You Tube videos Cof Data From Different Resources for all technical job person we appreciate all efforts. T7C24A1 and PBTC7C1 Cof Data EK73538 S050A. NT61302H-C5290A ILI5271M ILI5381M2AB NT39538H-1272A NT39538H-1272B RM7615F-034 NT39573H-C6007A COF Data www.fixledtv.blogspot.com Cof Data ILI5271M ILI5381M2A NT39538H-1272A NT39538H-1272B RM76150FA-034 RM76320FB-61A NT39573H-C6007A Cof Data and Voltages Firmware Available IMRAN ASHRAF +923139292880 https://electronics-tricks.blogspot.com Youtube Channel: https://www.youtube.com/user/imran03452164785/videos?view_as=subscriber Facebook Page: https://www.facebook.com/profile.php?id=100044482969994 T-Con M190ES DC DC IC 5562A Voltages Earn Coins Together ILI5271M2AA 5253-ACBPQ 861

COF (Chip-On-Film) Technology is widely used as a package for LCD Driver ICs Using a Reel-to-Reel system. COF tape can be mounted using solder. In case of panel failure of LCD/LED TV the following symptoms may usually occur:

The cause of the above symptoms is the failure of one of the contacts between the Glass side of the panel glass or between the PCB/Tcon Board Connections. If we diagnose the missing data on gate cof the repair solution is possible by bypassing the missing data/voltage from T-Con Board to Cof IC Points but this process requires good skills.

scratch gently the paint on the center of each pad and contact them with the tester of the multi-meter. When you are able to scratch the points then you can connect thin wire but for this, you need to identify the points first. So, here are some Cof Data Points for the technician’s support for free download.

All Cof data PDF files and image files are saved/collected from authentic and Expert Masters/Technicians. You can get the idea from these files. Kazmi Elecom Team is not responsible for any type of damage/loss. If you are new and do not have enough knowledge of loading or installing software/firmware or dump files then read here first.

The equipment is a professional high precision equipment,used to bond various FPC/COF/TAB cables with LCD and PCB. It’s suitable for flat and curved LCD screens in different sizes and can repair cable abscission and damage.

The present disclosure relates to the technical field of displays, and in particular, to an active-matrix organic light-emitting diode (AMOLED) display panel and a corresponding display device. BACKGROUND OF INVENTION

With development of display industry technologies, requirements of customers for display panels are increasingly high. For example, for some high-end display panels, customers require that a narrow bezel is designed. The current active-matrix organic light-emitting diode (AMOLED) display panel includes a display area C1 configured to set a pixel structure, a binding area C2 configured to place a chip on film (COF) or a chip binding area configured to place a chip on plastic (COP), a fan-out area C3 connected to “Data” signals in a pixel circuit of the display area C1 and a bending area C4 for bending. The binding area is bent to a location below the panel by bending the bending area C4, and a lower bezel of original rigid display panel may be diminished, as shown FIG. 1.

In the current design, a value of a distance D from the display area C1 to the bending area C4 is still relatively large. A main reason is that a wiring space of the fan-out area C3 requires to be considered, and a height required for the current fan-out area C3 is mainly affected by factors, such as a quantity of fan-out wires. That is, when the quantity of wires is relatively small, the height required for the fan-out area C3 may be reduced.

In the current AMOLED display panel, “Pentile” pixel arrangement is used. As shown in FIG. 2, a structure of the pixel arrangement includes a pixel 1 obtained by combining two sub-pixels, namely, a red sub-pixel and a green sub-pixel, and a pixel 2 obtained by combining two sub-pixels, namely, a blue sub-pixel and a green sub-pixel. The two pixels share neighboring sub-pixels and form repeating units arranged in an array manner. The repeating units are arranged along a row direction. Moreover, a direction of a short side of each sub-pixel is consistent with the row direction, and a direction of a long side of each sub-pixel is consistent with a column direction, such that each pixel requires two “Data” signal lines (data line) and one “Scan” signal line (gate line), so as to increase the quantity of fan-out wires and increase the height required for the fan-out area. SUMMARY OF INVENTION

Embodiments of the present disclosure provide an active-matrix organic light-emitting diode (AMOLED) display panel and a corresponding display device, in which a quantity of data lines is reduced. That is to reduce a quantity of fan-out wires and reduce a height of a fan-out area, to resolve a technical problem that a “Pentile” pixel arrangement design is used in the current AMOLED display panel and each pixel requires two data lines, causing an increase in the quantity of fan-out wires and an increase in the height required for the fan-out area.

An embodiment of the present disclosure provides an AMOLED display panel, which includes a plurality of first pixel units and a plurality of second pixel units, wherein the first pixel units and the second pixel units are alternately disposed along a horizontal direction and along a vertical direction to form a pixel structure arranged in a matrix manner;

wherein the first pixel unit includes a first sub-pixel and a second sub-pixel disposed side by side with the first sub-pixel; wherein the second pixel unit includes another first sub-pixel and a third sub-pixel disposed side by side with the another first sub-pixel; wherein the first pixel unit and the third sub-pixel adjacent to the second pixel unit constitute a pixel point, and the second pixel unit and a second sub-pixel adjacent to the first pixel unit constitute a pixel point;

wherein in the first pixel unit, the first sub-pixel and the second sub-pixel are arranged along a direction in which the data lines extend, and the first sub-pixel and the second sub-pixel share one of the data lines; wherein in the second pixel unit, the first sub-pixel and the third sub-pixel are arranged along the direction in which the data lines extend, and the first sub-pixel and the third sub-pixel share one of the data lines;

wherein the first sub-pixel, the second sub-pixel, and the third sub-pixel are rectangular and have areas in equal, and a direction extending along a long side of each of the first sub-pixel, the second sub-pixel, and the third sub-pixel is perpendicular to the direction in which the data lines extend; and

In the AMOLED display panel of the present disclosure, the pixel circuit is a 7T1C pixel circuit, and the 7T1C pixel circuit includes a driving transistor configured to determine driving current of a driving circuit,

In the AMOLED display panel of the present disclosure, the 7T1C pixel circuit includes a capacitor for voltage compensation, the capacitor includes a straight-strip-shaped lower electrode plate and a straight-strip-shaped upper electrode plate located over the straight-strip-shaped lower electrode plate, and the first gate is a portion of the straight-strip-shaped lower electrode plate.

In the AMOLED display panel of the present disclosure, the pixel circuit is a 7T1C pixel circuit, and the 7T1C pixel circuit includes a transistor configured to control a reference signal VI transmitted to a control end of the driving transistor;

An embodiment of the present disclosure provides another AMOLED display panel, which includes a plurality of first pixel units and a plurality of second pixel units, wherein the first pixel units and the second pixel units are alternately disposed along a horizontal direction and along a vertical direction to form a pixel structure arranged in a matrix manner;

wherein the first pixel unit includes a first sub-pixel and a second sub-pixel disposed side by side with the first sub-pixel; wherein the second pixel unit includes another first sub-pixel and a third sub-pixel disposed side by side with the another first sub-pixel; wherein the first pixel unit and the third sub-pixel adjacent to the second pixel unit constitute a pixel point, and the second pixel unit and a second sub-pixel adjacent to the first pixel unit constitute a pixel point;

wherein the pixel structure further includes a plurality of data lines connected to the sub-pixels; wherein in the first pixel unit, the first sub-pixel and the second sub-pixel are arranged along a direction in which the data lines extend, and the first sub-pixel and the second sub-pixel share one of the data lines; and wherein in the second pixel unit, the first sub-pixel and the third sub-pixel are arranged along the direction in which the data lines extend, and the first sub-pixel and the third sub-pixel share one of the data lines.

In the another AMOLED display panel of the present disclosure, the first sub-pixel, the second sub-pixel, and the third sub-pixel are rectangular and have areas in equal, and a direction extending along a long side of each of the first sub-pixel, the second sub-pixel, and the third sub-pixel is perpendicular to the direction in which the data lines extend.

In the another AMOLED display panel of the present disclosure, the pixel structure includes a pixel circuit configured to drive any one of the first sub-pixel, the second sub-pixel, and the third sub-pixel to emit light, and the pixel circuit is one of 7T1C, 6T1C, 6T2C, 5T1C, and 4T1C.

In the another AMOLED display panel of the present disclosure, the pixel circuit is a 7T1C pixel circuit, and the 7T1C pixel circuit includes a driving transistor configured to determine driving current of a driving circuit;

In the another AMOLED display panel of the present disclosure, the 7T1C pixel circuit includes a capacitor for voltage compensation, the capacitor includes a straight-strip-shaped lower electrode plate and a straight-strip-shaped upper electrode plate located over the straight-strip-shaped lower electrode plate, and the first gate is a portion of the straight-strip-shaped lower electrode plate.

In the another AMOLED display panel of the present disclosure, the pixel circuit is a 7T1C pixel circuit, and the 7T1C pixel circuit includes a transistor configured to control a reference signal VI transmitted to a control end of the driving transistor;

In the another AMOLED display panel of the present disclosure, the first sub-pixel is a green sub-pixel, the second sub-pixel is a blue sub-pixel, and the third sub-pixel is a red sub-pixel.

The present disclosure further relates to a display device including an AMOLED display panel, which includes a plurality of first pixel units and a plurality of second pixel units, wherein the first pixel units and the second pixel units are alternately disposed along a horizontal direction and along a vertical direction to form a pixel structure arranged in a matrix manner;

wherein the first pixel unit includes a first sub-pixel and a second sub-pixel disposed side by side with the first sub-pixel; wherein the second pixel unit includes another first sub-pixel and a third sub-pixel disposed side by side with the another first sub-pixel; wherein the first pixel unit and the third sub-pixel adjacent to the second pixel unit constitute a pixel point, and the second pixel unit and a second sub-pixel adjacent to the first pixel unit constitute a pixel point; and

wherein the pixel structure further includes a plurality of data lines connected to the sub-pixels. In the first pixel unit, the first sub-pixel and the second sub-pixel are arranged along a direction in which the data lines extend, and the first sub-pixel and the second sub-pixel share one of the data lines, and in the second pixel unit, the first sub-pixel and the third sub-pixel are arranged along the direction in which the data lines extend, and the first sub-pixel and the third sub-pixel share one of the data lines.

In the display device of the present disclosure, the first sub-pixel, the second sub-pixel, and the third sub-pixel are rectangular and have areas in equal. An extending direction of a long side of each of the first sub-pixel, the second sub-pixel and the third sub-pixel is perpendicular to the extending direction of the data lines.

Compared with AMOLED display panels in the prior art, the AMOLED display panel and the corresponding display device of the present disclosure are implemented by the first sub-pixel and the second sub-pixel in the first pixel unit share one of the data lines, and the first sub-pixel and the third sub-pixel in the second pixel unit share one of the data lines, such that a quantity of data lines is reduced, thereby reducing a quantity of fan-out wires, and reducing a space required by wiring in a fan-out area, so as to reduce a size of a lower bezel.

Additionally, when the 7T1C pixel circuit is configured to drive the sub-pixel, the channel area of the driving transistor is linear, thereby reducing a process difficulty. The first channel area and the second channel area of the transistor configured to control the reference signal VI transmitted to a control end of the driving transistor are oblique-line-shaped, thereby increasing an effective length of the channel area and reducing a leakage current. It resolves a technical problem that a “Pentile” pixel arrangement design used in the current AMOLED display panel, in which each pixel requires two data lines, that causes an increase in the quantity of fan-out wires and increases an height required for the fan-out area. BRIEF DESCRIPTION OF DRAWINGS

FIG. 5 is a schematic diagram of a structure of a 7T1C circuit of a first pixel unit of an embodiment of an AMOLED display panel according to the present disclosure (circuit structures of the first pixel unit and the second pixel unit are the same);

With reference to figures in the accompanying drawings, a same component symbol represents a same component. The following description is based on exemplified specific embodiments of the present disclosure, and the embodiments should not be considered to limit other specific embodiments of the present disclosure that are not detailed herein.

Referring to FIG. 3, which is a schematic diagram of arrangement of a pixel structure of an embodiment of an active-matrix organic light-emitting diode (AMOLED) display panel according to the present disclosure.

The AMOLED display panel of the present embodiment includes a plurality of first pixel units 10 and a plurality of second pixel units 20. The first pixel units 10 and the second pixel units 20 are alternately disposed along a horizontal direction and along a vertical direction to form a pixel structure arranged in a matrix manner.

The first pixel unit a includes a first sub-pixel 11 and a second sub-pixel 12 disposed side by side with the first sub-pixel 11. The second pixel unit b includes another first sub-pixel 11 and a third sub-pixel 13 disposed side by side with the another first sub-pixel 11. The first pixel unit a and a third sub-pixel 13 adjacent to the second pixel unit b constitute a pixel point. The second pixel unit b and a second sub-pixel 12 adjacent to the first pixel unit a constitute a pixel point.

The pixel structure further includes a plurality of data lines Data connected to sub-pixels. In the first pixel unit a, the first sub-pixel 11 and the second sub-pixel 12 are arranged along a direction in which the data lines Data extend. The first sub-pixel 11 and the second sub-pixel 12 share one of the data lines Data. In the second pixel unit b, the first sub-pixel 11 and the third sub-pixel 13 are arranged along the direction in which the data lines Data extend. The first sub-pixel 11 and the third sub-pixel 13 share one of data lines Data.

A sub-pixel includes a light-emitting device unit and a corresponding pixel driving circuit unit. In the present embodiment, a disposition of side by side between sub-pixels is essentially a disposition of side by side between pixel driving circuit units.

Compared with the prior art in which two sub-pixels, namely, a red sub-pixel and a green sub-pixel in a pixel 1 (as shown in FIGS. 2 and 6) are arranged along a direction that a gate line (Scan) extends, such that each of the red and green sub-pixels requires one of data lines Data, and shares the gate line (Scan), additionally, the sub-pixels are longitudinally arranged as a whole. The AMOLED display panel of the present embodiment is achieved by the first sub-pixel 11 and the second sub-pixel 12 in the first pixel unit a share one of the data lines Data, and by the first sub-pixel 11 and the third sub-pixel 13 in the second pixel unit b share one of the data lines Data, such that a quantity of the data lines Data is reduced, thereby reducing a quantity of fan-out wires, and reducing a space required for wiring in a fan-out area, so as to reduce a size of a lower bezel.

Compared with the AMOLED display panel in the prior art, although such disposition of the present embodiment increases a quantity of gate lines, the quantity of data lines Data is reduced by one half, thereby reducing a space required for wiring in a fan-out area, so as to reduce a size of a lower bezel. On the other band, the quantity of gate lines Scan is increased, but if the present disclosure and the prior art use the same driving manner, widths of left and right bezels are increased. Therefore, interlace driving or multi-stage driving may be for gate driver on array (GOA) circuits of two side areas to reduce the widths of the left and right bezels.

The first sub-pixel 11, the second sub-pixel 12 and the third sub-pixel 13 are rectangular and have areas in equal. A direction extending along a long side of each of the first sub-pixel 11, the second sub-pixel 12, and the third sub-pixel 13 is perpendicular to the direction in which the data lines Data extend. In such disposition, the entire structure of the sub-pixel horizontally extend, thereby facilitating the fabrication of a driving transistor in a driving circuit.

The driving transistor T1 is configured to determine driving current of the pixel driving circuit. The light-emitting device OLED is configured to illuminate to display in response to the driving current. The second transistor T2 is configured to control transmission of a data signal Data. The third transistor T3 is configured to control on and off of a control end and a second end of the driving transistor T1. The fourth transistor T4 is configured to control a reference signal VI transmitted to the control end of the driving transistor T1. The fifth transistor T5 is configured to control a first power signal VDD transmitted to a first end of the driving transistor T1. The sixth transistor T6 is configured to transmit the driving current from the driving transistor T1 to the light-emitting device OLED.

A control end of the fourth transistor T4 is connected to the gate driving signal Scan(n), a first end of the fourth transistor T4 is connected to the reference signal VI, a second end of the fourth transistor T4 is connected to a first end of the third transistor T3, a second end of the capacitor C1, and the control end of the driving transistor T1. The control end of the driving transistor T1 is connected to the second end of the capacitor C1, the second end of the fourth transistor T4 and the first end of the third transistor T3. The first end of the driving transistor T1 is connected to a second end of the second transistor T2 and a first end of the fifth transistor T5. The second end of the driving transistor T1 is connected to a second end of the third transistor T3 and a first end of the sixth transistor T6. A control end of the second transistor T2 is connected to a driving signal Scan(n), and a first end of the second transistor T2 is connected to a data signal Data. A control end of the fifth transistor T5 is connected to a driving signal EM(n). A second end of the fifth transistor is connected to a first end of the capacitor C1 and the first power signal VDD. An anode of the light-emitting device OLED is connected to a second end of the sixth transistor T6. A cathode of the light-emitting device OLED is connected to a second power signal VSS.

Compared with a width of a U-shaped channel area of a driving transistor T1′ (as shown in FIG. 6) in a 7T1C circuit structure of a pixel unit of the AMOLED display panel in the prior art, the linear channel area enables a channel width to be more easily controlled, and surface uniformity is better. Because the U-shaped channel has corners, which is more difficult to control a channel width at the corners in a manufacturing process.

The present disclosure further relates to a display device including an AMOLED display panel, which includes a plurality of first pixel units and a plurality of second pixel units. The first pixel units and the second pixel units are alternately disposed along a horizontal direction and along a vertical direction to form a pixel structure arranged in a matrix manner.

The first pixel unit includes a first sub-pixel and a second sub-pixel disposed side by side with the first sub-pixel. The second pixel unit includes another first sub-pixel and a third sub-pixel disposed side by side with the another first sub-pixel. The first pixel unit and a third sub-pixel adjacent to the second pixel unit constitute a pixel point. The second pixel unit and a second sub-pixel adjacent to the first pixel unit constitute a pixel point.

The pixel structure further includes a plurality of data lines connected to sub-pixels. In the first pixel unit, the first sub-pixel and the second sub-pixel are arranged along a direction in which the data lines extend, and the first sub-pixel and the second sub-pixel share one of the data lines, and in the second pixel unit, the first sub-pixel and the third sub-pixel are arranged along the direction in which the data lines extend, and the first sub-pixel and the third sub-pixel share one of the data lines.

In the display device of the present disclosure, the first sub-pixel, the second sub-pixel, and the third sub-pixel are rectangular and have areas in equal. An extending direction of a long side of each of the first sub-pixel, the second sub-pixel and the third sub-pixel is perpendicular to the extending direction of the data lines.

Compared with AMOLED display panels in the prior art, the AMOLED display panel and the corresponding display device of the present disclosure are implemented by the first sub-pixel and the second sub-pixel in the first pixel unit share one of the data lines, and the first sub-pixel and the third sub-pixel in the second pixel unit share one of the data lines, such that a quantity of data lines is reduced, thereby reducing a quantity of fan-out wires, and reducing a space required by wiring in a fan-out area, so as to reduce a size of a lower bezel.

Additionally, when the 7T1C pixel circuit is configured to drive the sub-pixel, the channel area of the driving transistor is linear, thereby reducing a process difficulty. The first channel area and the second channel area of the transistor configured to control the reference signal VI transmitted to a control end of the driving transistor are oblique-line-shaped, thereby increasing an effective length of the channel area and reducing a leakage current. It resolves a technical problem that a “Pentile” pixel arrangement design used in the current AMOLED display panel, in which each pixel requires two data lines, that causes an increase in the quantity of fan-out wires and increases a height required for the fan-out area.

The present application relates to a display panel, the display panel has a display area, a plurality of odd stage scan lines and even stage scan lines arranged sequentially in the display area, and non-display area located at two sides of the display area, and includes a plurality of odd stage gate COFs, disposed on a first side of the non-display area, each odd stage gate COF having a plurality of odd stage scan output channels corresponding to each of the odd stage scan lines respectively; and a plurality of even stage gate COFs, disposed on a second side opposite to the first side on the non-display area, each even stage gate COF having a plurality of even stage scan output channels corresponding to each of the even stage scan lines respectively.

The present application relates to a display panel and a gate driver structure, and particularly to a display panel and a gate driver structure for a thin film transistor liquid crystal display (TFT-LCD). BACKGROUND OF THE INVENTION

Thin film transistor liquid crystal displays (TFT-LCD) are the main variety of current flat-panel displays. The main driving principle of a TFT-LCD is shown in

FIG. 1. The system board 1 connects an R/G/B three-color compressed signal, a control signal, and a power through a line material and a connector on a printed circuit board (PCB) 10, and PCB plate 10 is connected to a gate chip on film (G-COF) 12 and a display area 13 through a source chip on film (S-COF) 11, so that the LCD obtains the desired power and signal.

The signals transmitted between the S-COF 11 and the G-COF 12, and the signals between different G-COF are all completed by a wiring of a layout of a fan-out area 14. With the development of the requirement for a narrow border of the display panel, the space for the wiring of the fan-out area on the gate side gradually decreases, the wiring of the layout gets more difficult, and the width thereof continues to decrease, thus it is needed to provide a gate driver structure to reduce the wiring density of the fan-out area. SUMMARY OF THE INVENTION

The present application arranges the G-COF in the single side drive structure on two sides of the display panel, to increase the space of the wiring of the fan-out area of the fan-out area on the gate side, and uses outputs of a plurality of odd stage G-COFs as start signals of the even stage G-COFs, to achieve reducing the density of the wiring of the fan-out area.

A display panel is provided according to an embodiment of the present invention, having a display area, a plurality of odd stage scan lines and even stage scan lines arranged sequentially in the display area, and non-display area located at two sides of the display area. The panel includes a plurality of odd stage gate COFs, disposed on a first side of the non-display area, each odd stage gate COF having a plurality of odd stage scan output channels corresponding to each of the odd stage scan lines respectively; and a plurality of even stage gate COFs, disposed on a second side opposite to the first side on the non-display area, each even stage gate COF having a plurality of even stage scan output channels corresponding to each of the even stage scan lines respectively; wherein a first odd stage gate COF of the plurality of odd stage gate COFs sequentially drives each of the odd stage scan output channels according to a first start signal, and in the first odd stage gate COF, the first odd stage scan output channel outputs a scan drive signal to a first even stage gate COF of the plurality of even stage gate COFs through a first odd stage scan line, and uses the scan drive signal as a second start signal of the first even stage gate COF, to sequentially drive each of the even stage scan output channels.

Preferably, the odd stage gate COFs of the plurality of odd stage gate COFs other than the first odd stage gate COF drive each odd stage scan output channel correspondingly according to another scan drive signal.

Preferably, a drive manner of each odd stage scan output channel of the plurality of odd stage gate COFs and each even stage scan output channel of the plurality of even stage gate COFs is driving each other alternatively.

Preferably, the first start signal comprises an initial pulse vertical signal, the initial pulse vertical signal being used as a start-up signal of each refreshed screen of the odd stage gate COF.

The present application arranges the G-COF in the single side drive structure on two sides of the display panel, to increase the space of the wiring of the fan-out area of the fan-out area on the gate side. Please refer to FIG. 2 and FIG. 3. FIG. 2 illustrates a diagram of a structure of a gate driver panel according to an embodiment of the present invention, and FIG. 3 illustrates a diagram of the detailed structure in FIG. 2. As shown in FIG. 2, a display panel 2 has a display area 20, a plurality of odd stage scan lines and even stage scan lines (like an odd stage scan line GL1 and an even stage scan line GL2), arranged sequentially in the display area 20, and non-display area 21 located at two sides of the display area 20. The panel 2 includes a plurality of odd stage gate COFs 210, disposed on a first side 201 of the non-display area 21, wherein each odd stage gate COF has a plurality of odd stage scan output channels Ch_O corresponding to each of the odd stage scan lines respectively; and a plurality of even stage gate COFs 210′, disposed on a second side 202 opposite the first side 201 on the non-display area 21, wherein each even stage gate COF 210′ has a plurality of even stage scan output channels Ch_E corresponding to each of the even stage scan lines respectively.

As shown in FIG. 3, a first odd stage gate COF COF 210_1 of the plurality of odd stage gate COFs 210 sequentially drives each of the odd stage scan output channels Ch_O according to a first start signal STV, and in the first odd stage gate COF 210_1, the first odd stage scan output channel Ch_O_1 outputs a scan drive signal S_Gate1 to a first even stage gate COF 210_1′ of the plurality of even stage gate COFs 210′ through a first odd stage scan line GL1, and uses the scan drive signal S_Gate1 as a second start signal S_ini of the first even stage gate COF 210_1′, to sequentially drive each of the even stage scan output channels Ch_E.

Preferably, the odd stage gate COFs 210 of the plurality of odd stage gate COFs other than the first odd stage gate COF 210_1 drive each odd stage scan output channel Ch_O correspondingly according to another scan drive signal STV′.

Preferably, the even stage gate COFs 210′ of the plurality of even stage gate COFs other than the first even stage gate COF 210_1′ drive each even stage scan output channel Ch_E correspondingly according to another scan drive signal S_ini′.

Preferably, a drive manner of each odd stage scan output channel Ch_O of the plurality of odd stage gate COFs 210 and each even stage scan output channel Ch_E of the plurality of even stage gate COFs 210′ is driving each other alternatively.

Preferably, the first start signal comprises an initial pulse vertical signal (start pulse vertical signal, STV), the initial pulse vertical signal being used as a start-up signal of each refreshed screen of the odd stage gate COF 210, for the G-COF, and once for each screen. When the first start signal STV is transmitted to the first odd G-COF 210_1, after the first odd G-COF 210_1 receives the first start signal STV, the scan drive signal S_Gate1 outputted is connected to the first even stage gate COF 210_1′ as the second start signal S_ini on the second side 202, and from the second output of the first odd G-COF 210_1, the output signal is only used as the turn-on signal of the gate, and not connected to the even stage G-COF on the second side 202. After a refreshed screen is completed, PCB generates a next first start signal, transmitted to the first odd G-COF 210_1, that is, in each screen, the first side 201 and the second side 202 only have a first start signal STV and a second start signal S_ini.

That is, using the scan output signal S_Gate1 of the first odd stage gate COF 210_1, as the second start signal S_ini of the first even stage gate COF 210_1′, it can be seen from FIG. 3, the first start signal STV is the start signal of the first odd stage gate COF 210_1, and the scan drive signal S_Gate1 outputted by the first odd stage gate COF 210_1; and the scan drive signal S_Gate1 is used as the second start signal S_ini of the G-COF 210_1′, and the scan drive signal outputted from the first even stage gate COF 210_1′ is signal S_Gate2.

FIG. 4 illustrates a diagram of a waveform of a scan output channel of the G-COF in FIG. 3 working in the display panel, wherein, the first odd stage scan output channel Ch_O_1 of the first odd stage gate COF 210_1 corresponds to the first odd stage scan line GL1, then the first even stage scan output channel Ch_E_1 of the first even stage gate COF 210_1′ corresponds to the even stage scan line GL2 next to the first odd stage scan line GL1, and sequentially, the second odd stage scan output channel Ch_O_2 of the G-COF 210_1 corresponds to the odd stage scan line GL3, and the second even stage scan output channel Ch_E_2 of the first even stage gate COF 210_1′ corresponds to the even stage scan line GL4 next to the odd stage scan line GL3.

The present application cooperating with a particular output timing of the G-COF, realizes the function of the G-COF, and changes the wiring space from single side to two sides to increase the wiring space for reducing the difficulty of the wiring, thereby increasing the product quality and the product competitiveness.

1. A display panel, having a display area, a plurality of odd stage scan lines and even stage scan lines arranged sequentially in the display area, and a non-display area located at two sides of the display area, the display panel comprising:

a plurality of odd stage gate chips on film (COFs), disposed on a first side of the non-display area, each odd stage gate COF having a plurality of odd stage scan output channels corresponding to each of the odd stage scan lines respectively; and

a plurality of even stage gate COFs, disposed on a second side opposite the first side on the non-display area, each even stage gate COF having a plurality of even stage scan output channels corresponding to each of the even stage scan lines respectively;

wherein a first odd stage gate COF of the plurality of odd stage gate COFs sequentially drives each of the odd stage scan output channels according to a first start signal, and in the first odd stage gate COF, the first odd stage scan output channel outputs a scan drive signal to a first even stage gate COF of the plurality of even stage gate COFs through a first odd stage scan line, and uses the scan drive signal as a second start signal of the first even stage gate COF, to sequentially drive each of the even stage scan output channels, and wherein the first start signal comprises an initial pulse vertical signal.

2. A display panel, having a display area, a plurality of odd stage scan lines and even stage scan lines arranged sequentially in the display area, and a non-display area located at two sides of the display area, the display panel comprising:

a plurality of odd stage gate COFs, disposed on a first side of the non-display area, each odd stage gate COF having a plurality of odd stage scan output channels corresponding to each of the odd stage scan lines respectively; and

a plurality of even stage gate COFs, disposed on a second side opposite the first side on the non-display area, each even stage gate COF having a plurality of even stage scan output channels corresponding to each of the even stage scan lines respectively;

wherein a first odd stage gate COF of the plurality of odd stage gate COFs sequentially drives each of the odd stage scan output channels according to a first start signal, and in the first odd stage gate COF, the first odd stage scan output channel outputs a scan drive signal to a first even stage gate COF of the plurality of even stage gate COFs through a first odd stage scan line, and uses the scan drive signal as a second start signal of the first even stage gate COF, to sequentially drive each of the even stage scan output channels.

3. The display panel of claim 2, wherein the odd stage gate COFs of the plurality of odd stage gate COFs other than the first odd stage gate COF drive each odd stage scan output channel correspondingly according to another scan drive signal.

4. The display panel of claim 2, wherein the even stage gate COFs of the plurality of even stage gate COFs other than the first even stage gate COF drive each even stage scan output channel correspondingly according to another scan drive signal.

5. The display panel of claim 2, wherein a drive manner of each odd stage scan output channel of the plurality of odd stage gate COFs and each even stage scan output channel of the plurality of even stage gate COFs is driving each other alternatively.

6. The display panel of claim 2, wherein the first start signal comprises an initial pulse vertical signal, the initial pulse vertical signal being used as a start-up signal of each refreshed screen of the odd stage gate COF.

7. A gate driver structure, located in a display panel, the display panel having a plurality of odd stage scan lines and even stage scan lines arranged sequentially, the gate driver structure comprising:

a plurality of odd stage gate COFs, disposed on a first side of the non-display area, each odd stage gate COF having a plurality of odd stage scan output channels corresponding to each of the odd stage scan lines respectively; and

a plurality of even stage gate COFs, disposed on a second side opposite to the first side on the non-display area, each even stage gate COF having a plurality of even stage scan output channels corresponding to each of the even stage scan lines respectively;

wherein a first odd stage gate COF of the plurality of odd stage gate COFs sequentially drives each of the odd stage scan output channels according to a first start signal, and in the first odd stage gate COF, the first odd stage scan output channel outputs a scan drive signal to a first even stage gate COF of the plurality of even stage gate COFs through a first odd stage scan line, uses the scan drive signal as a second start signal of the first even stage gate COF, to sequentially drive each of the even stage scan output channels.

8. The gate driver structure of claim 7, wherein the odd stage gate COFs of the plurality of odd stage gate COFs other than the first odd stage gate COF drive each odd stage scan output channel correspondingly according to another scan drive signal.

9. The gate driver structure of claim 7, wherein the even stage gate COFs of the plurality of even stage gate COFs other than the first even stage gate COF drive each even stage scan output channel correspondingly according to another scan drive signal.

10. The gate driver structure of claim 7, wherein a drive manner of each odd stage scan output channel of the plurality of odd stage gate COFs and each even stage scan output channel of the plurality of even stage gate COFs is driving each other alternatively.

11. The gate driver structure of claim 7, wherein the first start signal comprises an initial pulse vertical signal, the initial pulse vertical signal being used as a start-up signal of each refreshed screen of the odd stage gate COF.

TAB bonding machine, also name COF bonding machine, ACF bonding machine, OLB Bonding machine, Chip on Film bonding machine. COF(Chip on Film, Chip on Flex).COF bonding machine is widely used in the TV/laptop/pad panel, it is very popular in the TV/laptop repairing for the LCD/LED/OLED panel bonding. For TV or laptop panel repairing COF bonding machine, has COF on glass bonding and COF on PCB board bonding. The COF Bonding machine also can do COF on flex cable, COF on film bonding, and maybe IC on film bonding. Normal theCOF bonding machine is Pulse heating bonding machine with Titanium alloy press bonding head.

We also offer all the accessories: ACF tapes, ACF Remover, Blue glue, Acetone, Alcohol ,Customized bonding head, Quartz glass, Silicone tape, Teflon tape, Microscope, Air Compressor, COF cutter, Cleaning nanosponge, Cleaning clothes wiper, Ear buds, Pump bottles, T-bit, T-rubber, T-Iron, Magnifier lens, Allen key, Precision tweezers, Soldering Stations, Removing Wind Station Hot Air Gun, LEDS,LVDS cables, LCD Test Board, LCD/LED Tester.RT809H programmer, Open cell, Polarizer, Backlight ,T-Con Board, Main-board, IC, TAB COF IC and others.

TAB bonding machine is a widely used machine all over the world. This bonding machine is based on the recent innovations as well as planned to repair the arrangements of LCD, LED, and television. This bonding machine may consist of has two Digital Microscope, and also has a Digital Pressure Gauge. The ACF bonding machine consists of vacuum generator which may help to hold the panel during the bonding process. It may also provide the quick as well as easy solutions for various mobile problems. COF (TAB Bonding Machine) is fast as well as it is very easy to access this bonding machine. This bonding machine is able to provide high accuracy repair apparatus for repair different size of the LED or LCD screen as well as LCD Panel. COF bonding machine also consists a process of repairing the technical equipment in an easy way.

We provide the various sizes and types of this machine, as well as all the services, are available if any defect may occur in the machine. Anisotropic conductive film (ACF) bonding machine commonly use in connectivity with electrical and mechanical connections from electronics driver to glass substrate of the LCD/LED/TV. During the ACF bonding process, heat and pressure are applied via a thermode (or hot bar) on to the ACF film or other component that is sandwiching the ACF film.

TAB bonding machinehelps to repair LED,LCD,TV, of lining issues on panel . Ultimate solutions of bonding of COF (COF Bonding Machine)with fast and easy to operate bonding machine. it is a kind of high precision repair equipment for repair various size LED/LCD screen/LCD Panel.

TAB bonding machine OL-TVCBM1285-DH/SH-SS , is our company in the R&D process , according to maintenance staff tailored high-end products , machine not only in the accuracy of the temperature and the mechanical accuracy do the precision design , the procedures also increases the glass and circuit board parameters direct selected function , working pressure automatically switch , greatly facilitate the technical staff selected the parameters , increased the tool bit preheating function , to ensure that the machine at any temperature difference can ensure heating rate and temperature accuracy , double head design , glass and circuit board independent bonding reached factory-class level , high bonding excellent rate、low repair rate , this COF bonding machine is the maintenance and after-sales staff preferred the classic model.

TAB bonding machine OL-1285-DH/SH-SS platform Up to 100inch, the COF/TAB/ACF Bonding machine for TV repair,Television repair,Panel repair,screen repair. Welcome you visit us,our website:www.szoulian.com, It is your best choose for your TV COF repairing.

液晶电视维修辅助设备耗材 ,ACF胶带 AC-7206,AC-2056,G450去除液,日立蓝胶,酒精,丙酮,酒精瓶,棉布,纳米海绵,棉签,COF裁切刀,空压机,显微镜,热风枪,石英条,硅胶皮,铁氟龙,精密镊子,六角扳手,烙铁头,放大镜,校正仪,LVDS链接线, 驱动测试板等,免费随机附送整套,免费来厂学习,免费打出口木箱,欢迎来厂试机购买。

TAB/COF/ACF Bonding machine,12-65/85/100inch Single/Double Stations bonding head TV Repair machine,ACF/TAB/COF bonding machine for TV/laptop repair,Television repair,Panel repair,screen repair.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey