lcd panel edid eeprom error made in china

I have recently fitted a new LCD panel to a Dell 1545 Inspiron Laptop as well as a new inverter. When i boot it it gives a quick flash on the screen and thats it. I have tested the panel on the inverter on my packard bell and it lights up ok. I have an output to an external monitor too.

Could it be the wrong panel? it seems to me that the power to the inverter is being switched off as it only gives you a quick flash on the screen and thats that.

In the case of my 4K monitors, as they are connected by DisplayPort, powering them off via the front panel controls results in them “disconnecting” from the graphics card. Sometimes this doesn’t happen quite immediately, but the result is always the same – Windows thinks there is no monitor connected, thus the desktop is not rendered and remote control of the computer (via VNC in my case) is not possible or suffers strange graphical glitches.

Instead, I reasoned that a dummy plug could be made simply with an EEPROM containing the EDID data hooked up to the correct pins of the HDMI port. But instead of building one myself this time, I found some on eBay that were priced at about AU$3.30 and bought a few for some experiments. After all, getting a hold of an HDMI connector (e.g. via cutting open a cable) is perhaps even more expensive when factoring in the cost of an EEPROM and not quite as neat …

I cut apart the moulded rubber with a knife to reveal a small black PCB inside. On the top side, there aren’t any components, merely tracks leading to vias which push the signal to the other side. Some of the pins are soldered (i.e. the important ones – power, ground and EDID clock/data) whereas the others are not soldered at all. I would have preferred the other pins to be soldered for mechanical rigidity, but functionally, it would not make a difference.

The underside shows a similar pattern to the soldering on the HDMI port. The unit has an unbranded 24C02 EEPROM (as I expected), with a surface mount capacitor and three 4.7kOhm resistors probably to protect the EEPROM in case of a rogue device and signal hot plug detection.

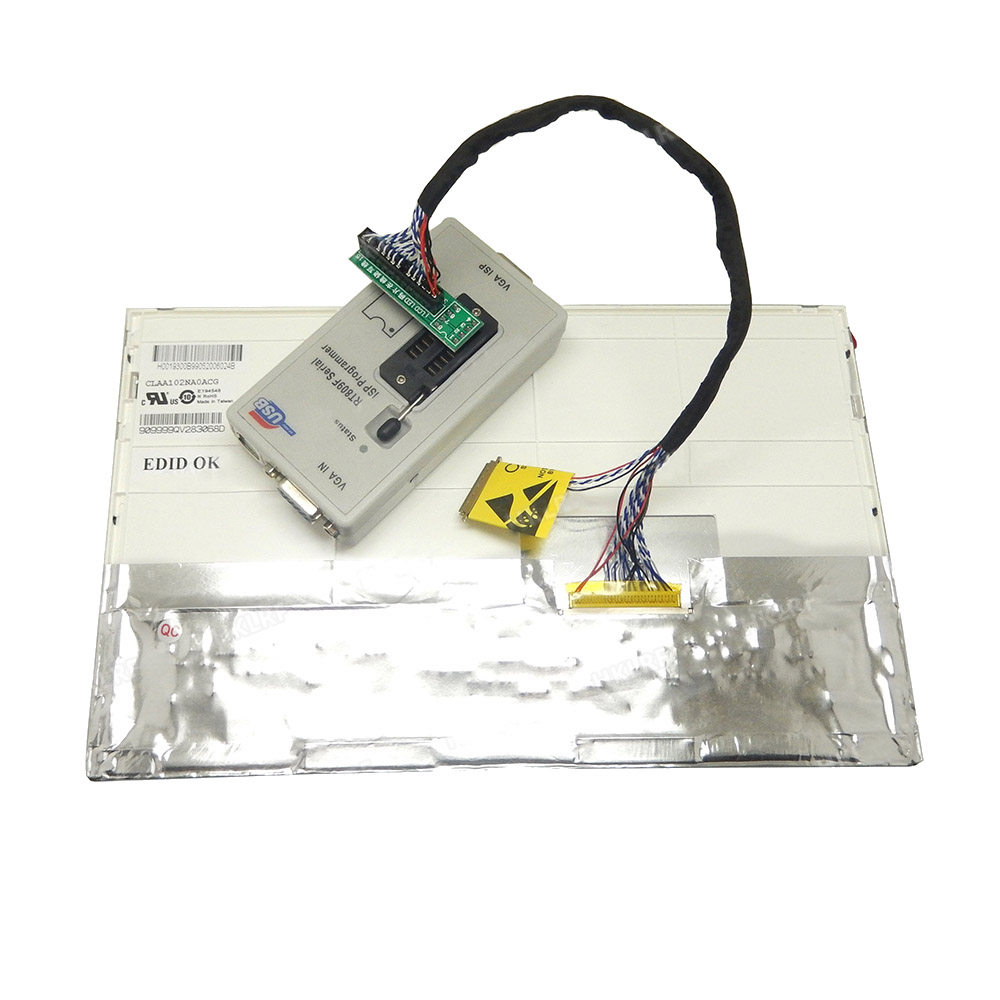

Once torn apart, dumping the EDID data was as easy as clipping on my CH341 programmer and reading out the EEPROM. The resulting dump can be downloaded here. To analyse the EDID in comfort, I used Analog Way’s EDID Editor which is a very useful piece of software for parsing and customising EDIDs. The following are screen dumps from the software showing what this dummy plug is pretending to be.

The standard data page shows that the Manufacturer ID is AOC with a product ID of 0CCD, serial number of 0, manufactured Week 3 of 2017. This suggests that the EDID is stolen from an AOC monitor with a horizontal size of 62cm and vertical size of 34cm. Standard timings go up to 1920×1080 at 75Hz or 1920×1200 at 60Hz.

It’s quite a confusing array of features – I never knew the 256-byte extended EDID could denote so many different pieces of display information, thus computers being “confused” about display capabilities could be a possibility especially if they don’t interpret some of these extensions.

The plug itself is not much in terms of circuitry, but that is the expectation. The EDID data seems to have been “stolen” from an AOC monitor and modified slightly, seemingly to prefer full HD but having the option to go up to 4K to ensure that devices which aren’t stable for 4K output don’t run into trouble. I suppose if you don’t like it, you could either shove wires into the device or break it apart and reprogram the EEPROM to whichever EDID you would like (e.g. change the monitor name, etc).

EDID data exchange is a standardized means for a display to communicate its capabilities to a source device. The premise of this communications is for the display to relay its operational characteristics, such as its native resolution, to the attached source, and then allow the source to generate the necessary video characteristics to match the needs of the display. This maximizes the functional compatibility between devices without requiring a user to configure them manually, thus reducing the potential for incorrect settings and adjustments that could compromise the quality of the displayed images and overall reliability of the system.

Generally, the source device will be a computer graphics card on a desktop or laptop PC, but provisions are in place for many other devices, including HDTV receivers and DVRs, DVD and Blu-ray Disc players, and even gaming consoles, to read EDID and output video accordingly. Originally developed for use between analog computer-video devices with VGA ports, EDID is also now implemented for DVI, HDMI, and DisplayPort.

EDID was developed by VESA - the Video Electronics Standards Association, with version 1.0 introduced in 1994 within version 1.0 of the DDC standard. See Table 1.

Prior to the development of EDID, pins 4, 11, 12, and 15 on the VGA connector were sometimes used to define monitor capabilities. These ID bit pins carried either high or low values to define different screen resolutions. VESA extended this scheme by redefining VGA connector pins 9, 12, and 15 as a serial bus in the form of the DDC - Display Data Channel. This allowed for much more information to be exchanged, so that EDID and other forms of communication were possible between the source and the display.

As display types and capabilities increased, 128 bytes became insufficient, and both EDID and DDC were extended so that multiple 128-byte data blocks could be exchanged. This is known as E-EDID and has been implemented in many consumer devices. In fact, the CEA - Consumer Electronics Association has defined its own EDID extensions to cover additional video formats and to support advanced multi-channel audio capabilities.

In December 2007, VESA released DisplayID, a second generation of EDID. It is intended to replace all previous versions. DisplayID is a variable length data structure, of up to 256 bytes, that conveys display-related information to attached source devices. It is meant to encompass PC display devices, consumer televisions, and embedded displays such as LCD screens within laptops, without the need for multiple extension blocks. DisplayID is not directly backward compatible with previous EDID/E-EDID versions, but is not yet widely incorporated in AV products.

The base EDID information of a display is conveyed within a 128-byte data structure that contains pertinent manufacturer and operation-related data. See Table 2. The current EDID version defines the structure as follows:

The general structure of CEA-861 extension data is shown in Table 3. CEA-861 allows for a variable number of 18-byte detailed timing descriptions to be included. For example, video timing details for 1080i, which is popular for consumer displays but not for PCs, can be communicated. CEA-861 also specifies a variable length "CEA Data Block Collection" for describing parameters such as display colorimetry, and advanced audio capabilities including surround sound format, audio sampling rate, and even speaker configuration and placement. The significance of the CEA-861 extension is that it aims to address previous operational disparities experienced with integrating consumer-based display devices into computer-based commercial AV systems, allowing for proper conveyance of EDID information between devices.

EDID information is typically exchanged when the video source starts up. The DDC specifications define a +5V supply connection for the source to provide power to a display"s EDID circuitry so that communication can be enabled, even if the display is powered off. At startup, the video source will send a request for EDID over the DDC. The EDID/DDC specifications support hot plug detection, so that EDID information can also be exchanged whenever a display is reconnected to a video source. Hot plug detection is not supported for VGA, but is supported in digital interfaces including DVI, HDMI, and DisplayPort. For these interfaces, the display device will supply a voltage on an HPD - Hot Plug Detect pin, to signal to the video source device that it is connected. The absence of a voltage on the HPD pin indicates disconnection. The video source device monitors the voltage on the HPD pin and initiates EDID requests as it senses incoming voltage.

Display devices can have various levels of EDID implementation and, in some cases, they may lack EDID information altogether. Such inconsistencies can cause operational issues ranging from overscan and resolution problems, to the display device not displaying the source content at all.

Possible CauseThe source device, such as a PC graphics card, or laptop, cannot read the EDID information from the display. As a result, in some cases the PC will not output any video signal.

While hot plug detection is supported for DVI, HDMI, and DisplayPort, EDID communication problems can arise from inconsistencies in the implementation of HPD signaling between devices from different manufacturers. This frequently becomes an issue for professional integration, since the ability to switch digital video signals is a necessity.

Possible CauseA PC cannot read the EDID information, so it defaults to a standard resolution, such as 640x480. If the user subsequently attempts to manually set the resolution to match the display, some graphics card drivers may enforce the lower default resolution and create a scrolling/panning desktop without actually changing the video resolution.

The PC is able to read the EDID information, but the graphics card limits the output resolution to XGA 1024x768, a resolution most displays can accommodate, ensuring a usable image and reducing the likelihood of no image being displayed. If this does not match the native resolution of the display, fonts will likely appear to be abnormally large, small, or fuzzy.

The PC is connected to multiple displays with different native resolutions. Since it can only read EDID from one display, the output will be mismatched in resolution with all other displays, resulting in less than optimal image quality, or no image displayed at all. This issue is a common occurrence in professional systems when video signals need to be distributed or routed to multiple displays.

Software such as Extron EDID Manager can be used to help troubleshoot possible compatibility issues between the display device and the source. EDID Manager is available as a free download from Extron"s Web site, www.extron.com. It is a useful software tool that allows you to read the display"s EDID and determine whether a graphic card and the display device may be experiencing EDID handshake problems.

AV systems typically comprise several remotely located displays and often include multiple source devices. It is important to realize this can potentially contribute to EDID-related issues. The necessity to switch, distribute, and route signals from sources to displays presents a considerable challenge in terms of ensuring proper EDID communications and therefore reliable system operation.

For example, systems that employ RGBHV-based distribution have no means of passing EDID information from the display to the source. This could become problematic in system designs where laptops and computers with expectation of seeing EDID are connected into the system. Since EDID information is not being provided to these devices, some of the aforementioned EDID communication issues may occur.

Extron products include features to help prevent or solve many of them by properly managing EDID communications between sources and displays in AV systems. These features provide automatic and continuous EDID management with attached source devices, ensuring proper power-up and reliable output of content.

EDID Emulation is a feature of many Extron DVI and HDMI products, including switchers, distribution amplifiers, and matrix switchers. It maintains constant EDID communication with source devices by providing pre-stored EDID information for various signal resolutions. A user can select the desired signal resolution, and then the corresponding EDID block is conveyed to all attached source devices. This EDID information is constantly available to the sources, even in a switching application where inputs are regularly selected and de-selected. The output of the sources should match the native resolution of the intended display device.

EDID Minder® is an advanced, Extron exclusive technology for EDID management. It encompasses EDID Emulation, but also incorporates an additional level of "intelligence." Extron products with EDID Minder® can communicate with the display device, and automatically capture and store EDID information from the display. See Figure 3. This captured information can then be used as the reference EDID for the sources. EDID Minder® is a standard feature in most Extron DVI and HDMI extenders, switchers, distribution amplifiers, and matrix switchers, as well as products that incorporate DVI or HDMI switching.

The functional role of a given product as a distribution amplifier, switcher, or matrix switcher determines the complexity of EDID Minder® implementation. Matrix switching environments represent the most difficult EDID management situation, with simultaneous EDID communications required for multiple inputs and outputs. The displays connected to the outputs are very likely to be of different models and native resolutions. The EDID information between them is different and needs to be conveyed to the source devices. Proper EDID management within the system is crucial to consistent and reliable operation.

Extron HDMI and DVI matrix switchers with EDID Minder® achieve this by managing EDID communications for each input/output tie. EDID Minder® first analyzes the EDID for all displays connected to the system, applies a complex algorithm to determine a common resolution, refresh rate and color space, and then uses the EDID protocol to set up the input sources. This powerful convenience feature simplifies system setup for the integrator, helps ensure consistent and reliable image display, and makes system operation virtually transparent to the end user.

The RM3251/RM5451/RM5251 LCD controllers offered hobbyists one of the first ever opportunities to create their own LCD display centric contraptions. Prior to this, the LVDS interface featured by almost all LCD panels was a mystery, with scores of tinkerers wondering how to interface this to something more familiar, i.e. VGA or DVI.

I’ve seen a few of these over the years, normally you get one posted to you when you engage with a LCD controller firmware company, right after signing a non-disclosure agreement, and handing over a lump of cash.

But on eBay? This is interesting. I had to hit ‘buy’. The seller has got their hands on the programmer software for this family of boards, and a whole bunch of firmware images for different panels, and they’re selling it on eBay for hobbyist money.

The present invention relates to a display apparatus and a method of controlling the same, and more particularly, to a display apparatus and a method of controlling the same, which can prevent error data from being stored in an extended display identification data (EDID) storage.

To provide the Plug and Play functionality to the display apparatus, the display apparatus must previously store extended display identification data (EDID), such as a manufacturer identification (ID), a model name ID, a display power management signaling function supportability, etc., and a protocol for data communication between the display apparatus and the computer must be previously set.

In the DDC1, the display data is transmitted from the display apparatus to the computer one bit by one bit in correspondence to a vertical synchronous signal transmitted from the computer. As long as the vertical synchronous signal is inputted to the display apparatus, the display apparatus continuously and circularly transmits the EDID having a data size of 128-bytes to the computer.

In the DDC2B, when the computer asks for the EDID of the display apparatus through a serial data line (SDA) and a serial clock line (SCL), the display apparatus transmits the EDID to the computer through the SDA.

As shown in FIG. 1, in a conventional display apparatus, an EDID storage 110 is operated by at least one of a display power and a computer power. Further, the EDID storage 110 includes a write-protect (WP) port being grounded.

Here, when the WP port is in a high state, it is allowed to only read data from the EDID storage 110. In contrast, when the WP port is in a low state, it is allowed to read data from and write data to the EDID storage 110.

However, the conventional display apparatus is allowed to write data to the EDID storage 110 so long as the computer power is supplied to the EDID storage 110 regardless of the display power. Therefore, error data may be unexpectedly written to the EDID storage 110 because of an electrostatic discharge (ESD) or application malfunction while the computer is being used.

Further, in a case when the computer is turned off while accessing the EDID storage 110 to read the EDID, the data communication is interrupted and therefore the EDID storage 110 cannot receive a clock signal from the computer through the SCL, so that the EDID storage 110 becomes abnormal.

Further, in a case when the computer is turned on while the EDID storage 110 is operated by the display power, the EDID storage 110 may be supplied with an unstable power due to the computer power. In this case, if the computer accesses the EDID storage 110, the data communication is inaccurately performed.

In order to solve the above-mentioned and/or other problems, it is an aspect of the general inventive concept to provide a display apparatus and a method of controlling the same, which can prevent error data from being stored in an EDID storage.

The foregoing and/or other aspects of the general inventive concept are achieved by providing a display apparatus including a connector, a readable/writable EDID storage to store EDID, and a controller to control the EDID storage to be write-protected from error data transmitted from a computer through the connector.

According to an aspect of the general inventive concept, the connector can be selectively connected with a video card of the computer or an EDID storage jig to store the EDID, and can output a determining signal according to a determination of what is connected to the connector, and the controller can control the EDID storage to be write-protected from the error data when the controller determines that the video card is connected, and can control the EDID storage to store the EDID transmitted from the EDID storage jig when the controller determines that the EDID storage jig is connected, on the basis of the determining signal.

According to another aspect of the general inventive concept, the EDID storage may include a write-protect (WP) port, and the controller may include a microcomputer to transmit an enable signal or a disable signal to the WP port according to the determining signal of the connector.

According to another aspect of the general inventive concept, the controller can control the EDID storage to initialize a communication condition of the EDID storage when the controller determines that the video card is connected, on the basis of the determining signal.

According to yet another aspect of the general inventive concept, the EDID storage may include an I2C line port, and the controller can determine whether an I2C line is accessible when the video card is connected, and can transmit a driving signal to the I2C line port to initialize the communication condition of the EDID storage when the I2C line is accessible.

According to still another aspect of the general inventive concept, the EDID storage may include a power input port to receive a display power or a computer power, and the controller can control the EDID storage to be write-protected from the error data when the controller determines that the computer power is supplied through the power input port.

According to still another aspect of the general inventive concept, the EDID storage may include a WP port, and the controller may include a current passage to connect a computer power line with the WP port.

According to still another aspect of the general inventive concept, the EDID storage may include a WP port, and the controller may include a microcomputer to transmit an enable signal or a disable signal to the WP port according to a determination of whether the computer power is supplied.

According to still another aspect of the general inventive concept, the controller can control the EDID storage to initialize a communication condition of the EDID storage when the controller determines that the computer power is supplied.

According to still another aspect of the general inventive concept, the EDID storage may include an I2C line port, and the controller can determine whether an I2C line is accessible when the computer power is supplied, and transmits a driving signal to the I2C line port to initialize the communication condition of the EDID storage when the I2C line is accessible.

According to still another aspect of the general inventive concept, the EDID storage may include a power input port to receive display power or computer power, and a WP port being enabled when the computer power is supplied through the power input port, and the controller can control the EDID storage to be write-protected from the error data when the controller determines that the display power is supplied while the computer power is supplied.

The above and/or other aspects of the general inventive concept may also be achieved by providing a method of controlling a display apparatus having a connector and a readable/writable EDID storage to store EDID, the method including controlling the EDID storage to be write-protected from error data transmitted from a computer through the connector.

According to an aspect of the general inventive concept, the controlling of the EDID storage may include allowing the connector to output a determining signal according to a determination of whether the connector is selectively connected with a video card of the computer or an EDID storage jig, to store the EDID, and controlling the EDID storage to be write-protected from the error data when it is determined that the video card is connected, and controlling the EDID storage to store the EDID transmitted from the EDID storage jig when it is determined that the EDID storage jig is connected, on the basis of the determining signal of the connector.

According to an aspect of the general inventive concept, the method may further include controlling the EDID storage to initialize a communication condition of the EDID storage when it is determined that the video card is connected, on the basis of the determining signal of the connector.

According to another aspect of the general inventive concept, the controlling of the EDID storage may include controlling the EDID storage to be write-protected from the error data when it is determined that computer power is supplied.

According to yet another aspect of the general inventive concept, the method may further includes controlling the EDID storage to initialize a communication condition of the EDID storage when it is determined that the computer power is supplied.

According to still another aspect of the general inventive concept, the controlling of the EDID storage may include enabling a WP port when the EDID storage is supplied with computer power, and controlling the EDID storage to be write-protected from the error data transmitted from the computer when it is determined that display power is supplied.

FIGS. 7A and 7B illustrate waveforms of signal levels of a port of a microcomputer and a WP port of the EDID storage in the display apparatus of FIG. 6;

FIG. 9 illustrates waveforms of signal levels of a computer power, a port of the microcomputer, and a WP port of the EDID storage in the display apparatus of FIG. 8;

FIGS. 2 and 3 are block diagrams of a display apparatus according to an embodiment of the general inventive concept. As shown in FIGS. 2 and 3, the display apparatus may include a connector 11 to which a video card 18 of a computer or an EDID storage jig 28 can be selectively connected, an EDID storage 10 to store the EDID, and a microcomputer 12 to control the EDID storage 10 according to a determination of what is connected to the connector 11.

It is noted that other external devices can be connected to the display device alternatively. The connector 11 may be a D-sub connector, a digital video interface (DVI) connector, etc., to which the video card 18, the EDID storage jig 28, etc., is selectively connected through one or more lines coupled between the display apparatus and the external device.

As shown in FIG. 2, when the video card 18 is connected to the connector 11, the connector 11 can output a ground voltage as a ground terminal of the video card 18 and a part of the connector 11 are connected. Further, as shown in FIG. 3, when the EDID storage jig 28 is connected to the connector 11, the connector 11 can output a predetermined voltage due to a resistor 26 provided in the EDID storage jig 28. That is, the connector 11 generates one of the grounded voltage and the predetermined voltage as a determining signal according to the determination of what is connected to the connector 11, thereby transmitting the determining signal to the microcomputer 12.

The EDID storage 10 may include an electrically erasable programmable read only memory (EEPROM) to store the EDID therein. In an aspect of this embodiment of the general inventive concept, the data size of the EDID is 128-byte as shown in the following

The EDID storage 10 may include a Vcc port to receive a display power or a computer power, a write-protect (WP) port, and a serial clock line (SCL) port and a serial data line (SDA) port used as an I2C line port to communicate with the microcomputer 12 and the video card 18.

The display power transmitted through a diode 14 or the computer power transmitted from the video card 18 and through a diode 16 can be supplied to the EDID storage 10 through the Vcc port. Here, the EDID storage 10 can be operated by at least one of the display power and the computer power.

Further, when the WP port is in a high state, it is allowed to only read data from the EDID storage 10. In contrast, when the WP port is in a low state, it is allowed to read and write data to the EDID storage 10.

The SCL and SDA ports of the EDID storage 10 can be connected to the video card 18 through the connector 11, thereby forming an I2C communication interface between the EDID storage 10 and the video card 18. Further, the SCL and SDA ports can be connected to the microcomputer 12, thereby allowing the EDID storage 10 to communicate with the microcomputer 12.

The microcomputer 12 can determine whether the video card 18 or the EDID storage jig 28 is connected to the connector 11, on the basis of the determining signal generated by the connector 11.

As shown in FIG. 2, in the case where it is determined that the video card 18 is connected to connector 11, the microcomputer 12 can transmit a high signal as an enable signal to the WP port of the EDID storage 10.

On the other hand, as shown in FIG. 3, in the case where it is determined that the EDID storage jig 28 is connected to the connector 11, the microcomputer 12 can transmit a low signal as a disable signal to the WP port of the EDID storage 10.

Thus, in the case where the video card 18 is connected to the connector 11, write-protection of the EDID storage 10 can be enabled, thereby preventing accidental error data transmitted from the computer from being stored in the EDID storage 10. Further, in the case where the EDID storage jig 28 is connected to the connector 11, the write-protection of the EDID storage 10 can be disabled, thereby allowing the normal EDID to be stored in the EDID storage 10. The normal EDID is transmitted from the EDID storage jig 28 to the SCL and SDA ports of the EDID storage 10 through SCL and SDA of the connector 11.

Further, in the case where it is determined that the video card 18 is connected to the connector 11, the microcomputer 12 determines whether an I2C line is accessible. As a result of the determination, when the I2C line is accessible, the microcomputer 12 transmits a stop condition signal to both SCL and SDA ports so as to initialize a communication condition of the EDID storage 10.

That is, the microcomputer 12 can transmit several times the SCL and SDA signals corresponding to the stop condition to the SCL and SDA ports of the EDID storage 10, thereby initializing the communication condition of the EDID storage 10.

FIG. 11 is a control flowchart of operations performed in the display apparatus of FIG. 2 when the video card 18 is connected to the connector 11, and FIG. 12 is a control flowchart of operations performed in the display apparatus of FIG. 3 when the EDID storage jig 28 is connected to the connector 11.

As shown in FIG. 11, the microcomputer 12 can determine whether the video card 18 is connected to the connector 11, on the basis of the determining signal generated by the connector 11 in operation S10. When it is determined that the video card 18 is connected to the connector 11, the microcomputer 12 can transmit the enable signal to the WP port of the EDID storage 10 in operation S12, thereby preventing the error data from being written on the EDID storage 10. The microcomputer 12 can initialize the communication condition of the EDID storage 10 in operation S14.

Further, as shown in FIG. 12, the microcomputer 12 can determine whether the EDID storage jig 28 is connected to the connector 11, on the basis of the determining signal generated by the connector 11 in operation S20. When it is determined that the EDID storage jig 28 is connected to the connector 11, the microcomputer 12 can transmit the disable signal to the WP port of the EDID storage 10 in operation S22, thereby allowing the EDID transmitted from the EDID storage jig 28 to be written on the EDID storage 10.

FIG. 4 is a block diagram of a display apparatus according to another embodiment of the general inventive concept. As shown in FIG. 4, the display apparatus may include an EDID storage 30 having a Vcc port to receive a display power or a computer power through diodes 34 and 36, respectively, a WP port connected to a computer power line 38, a SCL port and a SDA port to form an I2C communication interface; and a current passage 32 to control the EDID storage 30 according to a determination of whether the computer power is supplied or not.

The current passage 32 can connect the computer power line 38 with the WP port and can lower a level of the computer power into a predetermined level through a resistor 32 bwhen the computer power is supplied to the EDID storage 30 through the Vcc port, thereby transmitting a signal having a predetermined level to the WP port.

Thus, when the computer power is supplied to the EDID storage 30 as a computer is turned on, accidental error data transmitted from the computer is prevented from being stored in the EDID storage 30.

FIG. 5 is a block diagram of a display apparatus according to another embodiment of the general inventive concept. As shown in FIG. 5, the display apparatus may include an EDID storage 40 having a Vcc port to receive a display power or a computer power through diodes 44 and 46, respectively, a WP port, and a SCL port and a SDA port to form an I2C communication interface, and a microcomputer 42 to control the EDID storage 40 according to whether the computer power is supplied or not.

The microcomputer 42 can determine whether the computer power is supplied from a video card 48 connected with a connector (not shown) through the Vcc port of the EDID storage 40, by an interrupt method or a polling method.

As a result of the determination, when it is determined that the computer power is supplied from the video card 48 to the EDID storage 40, the microcomputer 42 can transmit a high signal to the WP port, thereby preventing accidental error data transmitted from the computer from being stored in the EDID storage 40.

Further, in the case where it is determined that the computer power is supplied to the EDID storage 40, the microcomputer 42 determines whether an I2C line is accessible. As a result of this determination, when the I2C line is accessible, the microcomputer 42 can transmit a stop condition signal to both SCL and SDA ports so as to initialize a communication condition of the EDID storage 40.

First, the current passage 32 of FIG. 4 and the microcomputer 42 of FIG. 5 sense whether the computer power is supplied to the Vcc port in operation S30. When it is determined that the computer power is supplied to the Vcc port, the enable signal is transmitted to the WP port of the EDID storage 30 and 40 in operation S32, thereby preventing the error data from being written on the EDID storage 30 and 40. A communication condition of the EDID storage 30 and 40 can be initialized in operation S34, wherein the initialization is implemented by the microcomputer 42 of FIG. 5. Further, in the embodiment of FIG. 4, a controller may be provided to sense whether the computer power is supplied or not and to initialize a communication condition of the EDID storage 30.

FIG. 6 is a block diagram of a display apparatus according to another embodiment of the general inventive concept. As shown in FIG. 6, the display apparatus may include an EDID storage 50 having a Vcc port to receive a display power or a computer power through diodes 54 and 56, respectively, a WP port, a SCL port and a SDA port to form an I2C communication interface, a switch 64 switching the WP port between enable and disable modes, a selector 58 selecting the WP port to be disabled, and a microcomputer 52 to control the switch 64 according to supplying of the display power and selection of the selector 58.

In this embodiment, the WP port connected to the Vcc port becomes a high level when the computer power is supplied, so that accidental error data transmitted from the computer is prevented from being stored in the EDID storage 50.

Here, the selector 58 is achieved by a hidden key combination of the display apparatus or a command of an EDID storage jig (not shown), etc. Therefore, the selector 58 may not be easily selected by a user, and can be selected in a manufacturing process or after-sales service.

Further, supposing that the EDID storage 50 of FIG. 6 is not supplied with the display power but the computer power, the WP port of the EDID storage 50 can be the high level, thereby preventing the error data from being written on the EDID storage 50.

However, when the EDID storage 50 is initially supplied with the display power while being supplied with the computer power, the microcomputer 52 can be reset, and an output port of the microcomputer 52 connected to the switch 64 can become a high level.

When the output port of the microcomputer 52 becomes a high level, the switch 64 illustrated as an NPN transistor in FIG. 6 is turned on. Hence, the WP port of the EDID storage 50 is grounded, so that there occurs a problem that a time interval in which writing is allowed is generated.

FIGS. 7A and 7B illustrate waveforms of signal levels of the port of the microcomputer 52 and the WP port of the EDID storage 50 of FIG. 6, and FIGS. 7A and 7B refer to a push-pull port and an open-drain port of the microcomputer 52, respectively.

As shown in a waveform of a signal level (a) of FIGS. 7A and 7B, when the EDID storage 50 is initially supplied with the display power while being supplied with the computer power, the port of the microcomputer 52 instantly becomes the high level during a time interval t1. Correspondingly, as shown in a waveform of a signal level (b) of FIGS. 7A and 7B, the WP port instantly becomes the low level during the time interval t1, thereby making the EDID storage 50 be writable. Therefore, error data may be written on the EDID storage 50.

Accordingly, in this embodiment of the present general inventive concept, when the display power is supplied to the EDID storage 50, the microcomputer 52 can be reset and can transmit the low signal to the switch 64, thereby turning off the switch 64. Therefore, the WP port can be connected to the Vcc port and can become a high level, and thus error data transmitted from the computer can be prevented from being written on the EDID storage 50 when the EDID storage 50 is initially supplied with the display power while being supplied with the computer power.

When an EDID storage 70 is supplied with the display power while being supplied with the computer power through a Vcc port, a port of the microcomputer 72 connected to the first switch 88 can instantly become a high level, and thus the first switch 88 is turned on and transmits a ground signal to the second switch 84. When the second switch 84 receives the ground signal and is turned off, the WP port can be connected to the Vcc port and can become a high level. Therefore, a writable time interval in which the EDID storage 70 is writable, like the time interval t1 shown in a waveform of a signal level (b) of FIGS. 7A and 7B, can be prevented from being generated.

Meanwhile, when the microcomputer 72 determines that the WP port is selected to be disabled by the selector 78, the microcomputer 72 can transmit a low signal to the first switch 88, thereby turning off the first switch 88. Then, a high signal can be transmitted to the second switch 84, thereby turning on the second switch 84. Thus, the WP port can be grounded and can be disabled as necessary (for example, in the case when the EDID is stored in the EDID storage in the manufacturing process).

FIG. 9 illustrates waveforms of signal levels of the computer power, the port of the microcomputer 72, and the WP port of the EDID storage 70 according to another embodiment of the present general inventive concept. While the computer power is supplied as shown in a waveform of a signal level (a) of FIG. 9, the WP port may have a high level as shown in a waveform of a signal level (c), thereby protecting the EDID storage 70 from writing.

With this configuration, operations of the display apparatus of FIGS. 6 and 8 will be described hereinbelow with reference to FIG. 14. Assuming that the computer power is being supplied to the EDID storage 50 and 70.

First, the display power can be supplied to the EDID storage 50 and 70 in operation S40, and thus, the microcomputer 52 and 72 can be initialized in operation S42. Then, the microcomputer 52 and 72 can control the enable signal to be transmitted to the WP port of the EDID storage 50 and 70 in operation S44, thereby solving the problem that the WP port is disabled when the microcomputer 52 and 72 is reset.

In the above-described embodiments, the high signal is employed as the enable signal, and the low signal is employed as the disable signal. However, in the case where the WP port of the EDID storage is a low active port, a low signal may be employed as the enable signal, and a high signal may be employed as the disable signal.

Thus, the EDID storage is controlled to prevent error data transmitted from the computer through the connector from being stored in the EDID storage, thereby protecting the EDID storage from storing abnormal data.

As described above, the present general inventive concept provides a display apparatus and a method of controlling the same, which can prevent error data from being stored in an EDID storage.

Three I2C addresses are responding. 0x37 and 0x50 are the "well known addresses" for DDC/CI and the EDID EEPROM, according to an old BenQ Z Series flash guide. This blog post is one of the rare sources about flashing Mstar chips. Furthermore, via this guide the info was found that communication with the Mstar chip requires address 0x49 on I2C. It does not seem to be available via USB-C.

One thing I do hope to be able to do, however, is eventually selling "making your display work" kits on Tindie which would cover usecases that Chinese sellers don"t cover. For instance, eDP displays from laptops can easily be adapted to full-size DisplayPort with a small PCB that"d connect to commonly available eDP-FPC cables with standardized pinout, providing both a DisplayPort input and a small circuit generating EN+ADJ signals for the panel"s builtin LED driver. Nobody is currently making these boards, but there"s a market for them, and I will be making them. And I"ll be linking to product pages for these boards from this project page, for sure - but that"s not the end goal, it"s merely "I can do this and it nets some extra income to fund my research" thing, especially given these boards will certainly be OSHW.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey