igzo tft display factory

The thin-film transistor (TFT) became commercially available slightly more than 30 years ago in the form of a switch for the Liquid Crystal Display. It all started with an amorphous silicon (a-Si) TFT. Compared to the traditional crystalline silicon CMOS transistor, the a-Si TFT can be produced on large substrates and at low processing temperatures, below 300 °C, enabling integration on glass substrates and even flexible substrates.

A-Si TFTs are mainly implemented as simple pixel switches due to their low charge carrier mobility (0.5-1 cm²/Vs). An alternative semiconductor on glass substrates is low-temperature polycrystalline silicon (LTPS), outperforming a-Si TFTs by a 100x larger mobility (50-100 cm²/Vs) and often used for high-end displays and imagers. Despite the advantages, fabrication of an LTPS TFT takes more process steps, is limited in substrate size, and requires a larger process temperature. Oxide-based semiconductors as indium-gallium-zinc-oxide (IGZO) fill this gap between a-Si and LTPS nicely, exhibiting low processing temperatures and a decent charge carrier mobility of 10 up to 40 cm²/Vs [1].

Figure 1: Example cross-section of an IGZO TFT with a dual-gate fabricated on a glass substrate. The top and bottom gates can be connected by vias through the first metal layer (M1). Silicon dioxide (SiO2) is used to insulate the gates from the active IGZO layer, to achieve the field-effect transistor. After fabrication, the glass can be detached from the polyimide layer resulting in a flexible circuit.

With such characteristics, the IGZO TFTs can be used to fabricate relatively complex circuits on flexible substrates. Consequently, IGZO TFTs are evolving beyond displays and entering the fields of wearable devices and the Internet of Things (IoT). Some highlights include an ultra-flexible circuit for recording electrocardiograms [2], radiofrequency identification (RFID) tags and near-field communication (NFC) tags [1]. Even the memory field has noticed IGZO and its extremely low OFF current and recently demonstrated a capacitor-less IGZO-based DRAM cell with a retention time longer than 400 seconds [3]. We can expect the first IGZO products beyond display applications to emerge in the near future.

As with a large majority of products, electrostatic discharge (ESD) protection is an important concern. If we are to see IGZO products enter the fields of IoT or biomedical engineering, they will have to include ESD protection.

Perhaps ESD protection is not a great concern for wireless products, for example, NFC and RFID tags which have no wired input and output ports. Here the sensitive electronic parts will not be exposed to the user as they are electrically insulated. In this case, like for displays [4,5], a good ESD control program might be enough to protect the IGZO components during assembly. The full display will, in any case, include ESD protection circuits at the system level, even perhaps at the peripherals where the electrical connections leave the display, but not necessarily at the IGZO component level. On the other hand, some wearables like the electrocardiogram patch, might not be able to affordsystem-level ESD protection circuits fabricated in a different technology other than IGZO. Since the electrodes have direct contact with the end-user, they may require ESD protection circuits at the device level. The same will be true for displays and imagers if their peripheral circuits are implemented using IGZO – to enable a fully flexible display, for example.

Yes, like any digital or analog circuit, also IGZO TFT circuits are susceptible to ESD. Even though the IGZO TFT technology nominal voltage can be as high as 10 V, degradation and breakdown can be observed already at 20 to 30 V [6]. To avoid damage to performance, the IGZO circuit should never be exposed to voltages higher than 20 V. This means the eventual ESD protection circuits should have a clamping voltage lower than 20V, which is only twice the nominal voltage. These limits depend on the IGZO technology and could change as the technology improves.

There are several challenges when designing IGZO TFT circuits in general, but perhaps the most prominent one is the fact it is a unipolar technology. Unlike the complementary metal-oxide-semiconductor (CMOS) technology integrating two types of transistors, n-type and p-type, the IGZO TFT only provides n-type transistors. Research on p-type oxide-based TFTs to complement the IGZO n-type transistor exists. Unfortunately, the p-type transistors generally have a much lower charge carrier mobility and would make the complementary design less efficient than the unipolar one [1]. Since ESD protection circuits can rarely dictate the technology evolution, ESD protection designs will most likely have to be made with unipolar circuits too.

The second challenge of the IGZO TFT technology for ESD circuit design is that there are usually no diodes available. Even though it is possible to make diodes in the IGZO TFT technology, it also increases the process cost and is not a commodity in this industry. Therefore, the best next choice would be a diode-connected transistor. The technology options to improve the ESD performance of the diode-connected transistor would be to smartly use the back-gate or to optimize the channel material resulting in larger mobility.

Luckily, the negative threshold issue that was observed in the early IGZO TFT technology improved significantly. Therefore, the significant leakage at the zero-volt bias that would be present in IGZO TFT ESD protection circuits can be solved from the technology side.

Figure 3: Drain-to-source current as function of the gate-to-source voltage measured on a dual-gate IGZO transistor shows a positive threshold voltage (top) and leakage currents below the measurement setup noise level (bottom). These data have been measured on a 5 µm by 100 µm TFT with a drain-to-source bias voltage of 50 mV.

Nevertheless, given the limited IGZO TFT conductivity, to achieve a product-worthy ESD protection level, the ESD circuits will have to be in the millimeter or even centimeter size range [5][2]. Given the IGZO TFT technology is optimized for large areas, spending these kinds of areas for ESD protection should not be a showstopper.

Unlike the silicon integrated circuit technology, there is a very limited choice of devices in IGZO, which also limits the possible solutions of ESD protection circuits. Passive devices could help with that. Inductors, capacitors, and resistors could be used as ESD protection or to complement the active devices. A spark gap could be a compact ESD protection option too.

IGZO TFT technology is a good candidate for future wearable and flexible electronic devices. If it is used in a wireless or non-contact way, consumer-side ESD protection should not be a great concern. However, if it will be used as a wearable with electrically exposed pads, it will certainly require ESD protection designs and ESD testing. In this case, the ESD testers might need to be adapted. Take the Human Body Model (HBM) ESD tester, for example. Most HBM ESD testers today target small, packaged devices in millimeter or centimeter sizes. HBM ESD testing of an IGZO TFT product might imply pins to be more than 10 cm apart. That might be challenging indeed, but perhaps some ingenious test fixtures or packaging could overcome this. Bending the flexible wearable device for ESD testing purposes could be an example.

The Transmission Line Pulse (TLP) ESD tester could be an alternative to HBM testing. Since the TLP tester is of a more academic nature than the HBM tester, it could perhaps offer more flexibility in connecting to the large IGZO circuit. Even though the TLP is a 50-Ohm tester while HBM has a typical series resistance of 1500 Ohm, we have observed comparable ESD testing results with both testers [6]. Since there is no universal conversion rule, care needs to be taken when interpreting TLP measurement results as HBM protection values.

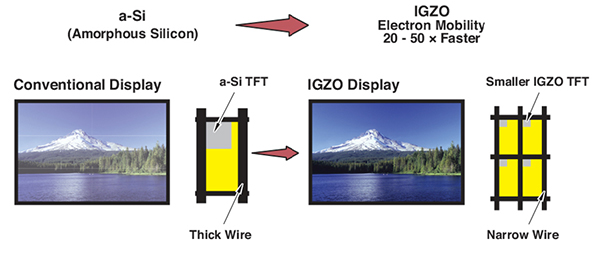

Liquid crystal displays (LCD) began to replace cathode-ray tube-based televisions in the early 2000s. The pixels in these LCDs were, until 2012, driven exclusively by thin-film transistors (TFTs) that use amorphous hydrogenated silicon (a-Si:H) as the semiconducting channel. But as demand grew for ever larger displays, with better viewing and energy performance, a need for improved TFTs emerged. TFTs block light coming from the display, so they need to be small, which lowers their current-driving ability. Additionally, there was a push to move away from LCD technology and into organic light emitting diodes (OLEDs) in order to capitalize on their better performance, which includes direct emission and richer colours, but OLEDs need to be driven by large amounts of current, at levels a-Si:H TFTs cannot accommodate. What was needed was a new technology that could be used to create TFTs with a high charge carrier mobility, which could drive large currents.

Charge carrier mobility tells us how quickly charge carriers (electrons and holes) can move through a semiconductor, and determines the amount of current we can drive through a TFT of a given size. This is limited by the nature of the path that charge carriers take though a material. This path can be thought of in terms of the atomic orbitals and how they interconnect to make up the conduction and valence bands — the energetic levels at which the electrons and holes are free to move around. The sp3 hybridized orbitals in silicon are highly directional, and in the crystalline state the silicon–silicon bonds properly overlap, providing an efficient path to travel through. However, in amorphous silicon, structural disorder leads to disconnects and conduction cannot occur through the orbitals in the same way. Instead, the charge carriers have to hop across the orbitals, which leads to mobilities of at most 1 cm2 V–1 s–1 — about 2–3 orders of magnitude lower than in crystalline silicon.

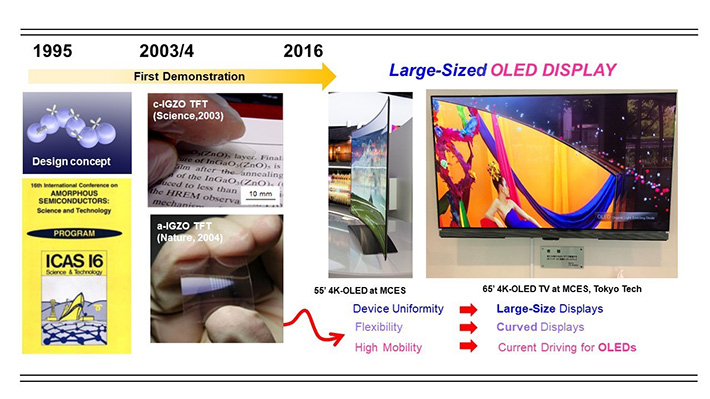

After a few years verifying the validity of the hypothesis, we started research on transparent oxide TFTs. To develop high-mobility TFTs using transparent conductive oxides, the major issue was their high carrier concentrations (the TFTs can’t be turned off). Indium oxide is a typical transparent conductive oxide with a large mobility, but reducing its excessive carrier concentration is difficult due the ease with which oxygen vacancies form. We tested InGaO3(ZnO)m epitaxial films, where m = 4 and 5, as I believed the unique local structure around Ga3+ would help lower the carrier concentration. As expected, the carrier concentration in epitaxial InGaO3(ZnO)4 reduced to a suitable level, and when applied in TFTs showed excellent performance, with a mobility of approximately 80 cm2 V–1 s–1. We then fabricated thin films using amorphous InGaZnO4 (a-IGZO). The electron concentrations in the resulting a-IGZO thin films, which were deposited on glass substrates at room temperature, were below 1016 cm–3 and the TFTs exhibited mobilities of approximately 10 cm2 V–1 s–1 — an order of magnitude larger than that of a-Si:H TFTs. We also found that TFTs fabricated on plastic substrates offered almost identical performance (Fig. 1). At this point we applied for patents and then submitted our paper to Nature, which was published in 2004.

Demonstrations of IGZO TFT-based displays began to emerge in 2007, when Samsung Electronics first reported a-IGZO TFT-based high-definition LCDs. Demonstrations of IGZO TFT-based backplane LCDs in smart phones and tablet computers then appeared around 2012. Arguably the most striking application emerged in 2015, when LG Display demonstrated large-sized OLED televisions. Here the a-IGZO TFT was indispensable because of the need for high mobility and simple formation over large areas.

I believe the success of IGZO transistors is due to a number of factors. First is their high mobility, which is an order of magnitude higher than a-Si:H, and the excellent controllability of their carrier concentration. Second, the production process is almost the same as a-Si:H, except for the deposition of the channel layer (chemical vapour deposition is used for a-Si:H whereas sputtering is used for IGZO), making integration into current manufacturing workflows relatively painless. Third, synthesizing large-sized high-quality sputtering targets is relatively easy, which also makes thin-film deposition on large-sized substrates a relatively simple task. With these attributes, IGZO transistors provide a promising backplane technology to drive the future of flat panel displays.

An IGZO display is any display panel that uses indium gallium zinc oxide or IGZO as the primary semiconducting material in its thin-film transistor or TFT. Hence, it is not a display technology but rather, a specific backplane technology for driving and addressing transmissive or emissive components of a particular panel.

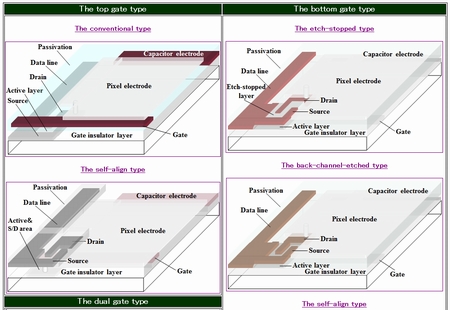

Some of the notable examples of a display technology include LCD technologies such as in-plane switching or IPS LCD and twisted nematic or TN LCD, as well as organic light-emitting diode or OLED technology, and microLED technology. On the other hand, there are three major backplane technologies: IGZO TFT, amorphous silicon or a-Si TFT, and low-temperature polysilicon or LTPS TFT.

• Note that a-Si-TFT is not transparent but can be stretched thin enough to allow an adequate amount of light to pass through. An IGZO-TFT is naturally transparent, thus translating to specific advantages such as brighter display panels and energy efficiency, reduced need for backlighting in the case of LCDs, and reduced brightness output in OLED and LED displays.

• Another advantage of IGZO display is that it has 30 to 50 times more electron mobility than a-Si display. Better electron flow means higher resolutions and faster pixel response time to allow the manufacturing of smaller panels with high pixel density. Earlier prototypes using indium gallium zinc oxide featured a 6-inch panel at 2560×1600 pixels or 498 pixels per inch.

• Note that transparency and better electron mobility also mean that these displays are more power-efficient than those based on amorphous silicon. Furthermore, it has a lower leakage current than both amorphous and low-temperature polysilicon TFT, thus allowing it to retain an active pixel state longer, especially when displaying still images such as photographs and documents.

• Manufacturing IGZO displays also require the use of rare-earth materials. More specifically, indium and gallium are rare. They are costly to extract from their point of origin and procure from the suppliers. This drawback introduces cost and supply risks for manufacturers of display panels and consumer electronic devices.

• Another disadvantage is that producing displays based on this semiconductor is more complicated than manufacturing a-Si TFT display panels. The current challenge to mass-producing indium gallium zinc oxide is the relevant synthesis method using Pulsed Laser Deposition or PLD. However, PLD requires expensive equipment and lengthier time. These requirements can hamper large-scale production.

• It is also worth mentioning that LTPS displays have key advantages over IGZO displays and a-Si displays. More specifically, it has better and faster electron flow, allows the production of small-sized screens with high pixel density, and more efficient power consumption.

Miyata, Y., Furuta, M., Yoshioka, T., and Kawamura, T. 1992. “Low-Temperature Polycrystalline Silicon Thin-Film Transistors for Large-Area Liquid Crystal Display.” Japanese Journal of Applied Physics. 31(P. 1, No. 12B): 4559-4562. DOI: 1143/jjap.31.4559

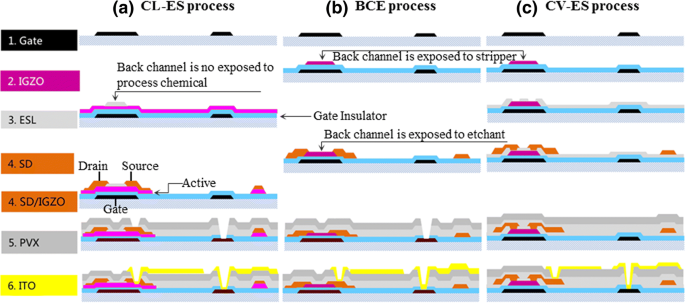

a-IGZO-based TFT fabricated via CL-ES process shows the same mask number to that of BCE process (Fig. 1). Compared with a-IGZO-based TFT with BCE structure, a-IGZO-based TFT with CL-ES structure shows two advantages: (1) a-IGZO-based backplane produced using CL-ES process deposits gate insulator, a-IGZO nano-layer, and ES nano-layer sequentially, then forms a ESL nano-mask through dry-etch method. This newly formed ESL nano-mask with 100 nm can prevent the exposure of a-IGZO nano-film to etchant, stripper, or photoresist. Therefore, the contamination at inter-layer interfaces is effectively prevented [25]. (2) At the same time, a-IGZO nano-film is not protected by ES layer but bombarded by CF4 plasma during the ESL nano-mask formation, thus becomes a conductor. This naturally forms the Ohmic contact between S/D electrode of following process and a-IGZO semiconductor. For another part, a simultaneous etching of S/D and a-IGZO nano-layer can be one overlay allowance of ESL-(a-IGZO+S/D metallization) layer, which could decrease the two overlay process error of the a-IGZO-ESL and ES-S/D metallization layer in the conventional ESL process (Fig. 2). The overlay number of the a-IGZO, ES, and S/D layer is reduced, which resulted in the decrease in the size of TFT device that lowered the parasitic capacitance. The outcome planar structure is similar to the BCE structure (Fig. 3a, b).

(Color online) Schematics of simultaneous formation method for TFT channel and S/D electrode in CL-ES process. a The first step that forms gate electrode. b The second step that forms etch-stopper layer. c The third step that forms S/D photo pattern. d The fourth step that forms S/D electrode and active pattern

Figure 3 shows the SEM images of a-IGZO-based TFTs with CL-ES structure (Fig. 3a, c) and BCE structure (Fig. 3b, d). From the top view, it is difficult to identify the differences between CL-ES structure and BCE structure (Fig. 3a, b). From the side view, an ES nano-layer can be found between the a-IGZO nano-layer and the S/D electrode layer in CL-ES structure (Fig. 3c). Meanwhile, a passivation layer can be found on the top of a-IGZO nano-layer in BCE structure (Fig. 3d). In the presented CL-ES process, an a-IGZO nano-layer with a thickness of 30 nm is deposited. Moreover, the damage during wet etching is negligible. For BCE process, a 70-nm a-IGZO nano-layer is deposited, as a-IGZO layer needs compensation for etching loss. The difference between the thicknesses of a-IGZO nano-layers in CL-ES and BCE structures can be observed in the SEM images (Fig. 3c, d).

The I-V characteristics of a-IGZO-based TFT with CL-ES structure and BCE structure are compared (Fig. 4). The saturation electron mobility, threshold voltage, subthreshold voltage swing (SS) value, and more characteristic values are summarized in Table 1. Note that the values summarized in Table 1 are the average number derived from the center and edge of an 8.5 generation glass substrate. The a-IGZO-based TFT with CL-ES structure realizes Vth of − 0.8 V, SS value of 0.18 V/dec, and saturation electron mobility of 8.05 cm2/V s. In the a-IGZO-based TFT with BCE structure, the corresponding results are Vth of + 0.5 V, SS value of 0.77 V/dec, and saturation electron mobility of 6.03 cm2/V s. Compared to the BCE structure, CL-ES structure shows an improved device performances. However, the on-current characteristic of the a-IGZO-based TFT device with CL-ES structure is lower than that with BCE-structured device. This is due to the fact that TFT channel structures are different in CL-ES and BCE structures. Generally, BCE-structured TFT channel length are the distance between S/D metal electrodes, and the measured channel length in this study is 5 um [21]. In CL-ES structure, electrodes are in contact with the a-IGZO nano-film that is stretched at the side of ESL nano-mask. Therefore, the channel length is decided by the distance between the a-IGZOs defined at the etch-stopper’s sides, but not determined by the distance between the electrodes. The channel length of the present CL-ES-structure device is measured to be 10 um.

(Color online) Comparison of I-V characteristic of a-IGZO TFTs with CL-ES and BCE structure on the center (a) and edge (b) of 8.5 generation glass substrate

As shown in Table 1, the measured values of Ion/Ioff ratio (~ 106, see Table 1) are approximately 10 times smaller than the typical value (> 107) of a-IGZO-based TFTs. This is because the measuring equipment used here is for the 8.5 generation mass production. Long cables are necessary for these measurements, as the size of the industrial equipment is large. The long cables resulted in an increased measurement noise. In the following reliability testing, smaller-scale measuring equipment is utilized, and the individual TFT devices is used as specimen for measurement. In this way, the measured Ion/Ioff ratios are all upper 107 (see below).

CL-ES process is carefully designed to prevent a-IGZO channel layer being exposed to etchant, photoresist, or stripper. During the process that produces CL-ES process, gate insulator, a-IGZO nano-layer, and ES nano-layer, each inter-layer interface is in contact with only DI water for cleaning purpose. Hence, the chemical contamination is negligible in insulator layer and a-IGZO nano-layer [25, 26]. However, the BCE process not only exposes channel layer to the chemicals but also involves Cu ion diffusion contamination, as the a-IGZO channel is directly exposed to Cu metal. This is also avoided in device with CL-ES structure. The channel region of the a-IGZO nano-film is well protected by ESL nano-mask. The low chemical contamination in CL-ES process may lead to a low carrier trap density at the interface between a-IGZO nano-layer and insulator layer, resulting in an excellent SS value. This low chemical contamination of a-IGZO-based TFT device via CL-ES process also helps improve the uniformity and reproducibility of a-IGZO TFT, which are highly important in industrial production [27, 28].

Figure 5 shows the measured I-V characteristic of TFTs with CL-ES structure and BCE structure derived from 42 measuring points on an 8.5 generation substrate. a-IGZO-based TFT with CL-ES structure has a Vth range of 0.72 V, while that of BCE-structured device is 2.14 V (Table 1). In other words, the uniformity of device performance is significantly improved by CL-ES structure.

(Color online) a CL-ES structure. b BCE structure’s TFTs I-V transfer characteristic. c 42 measuring points. d the photo of TFT. All measured on an 8.5 generation substrate

Figure 6a, b show the I-V characteristic shift of CL-ES-structured device and BCE-structured device obtained in NBTIS testing, respectively. The NBTIS testing results are summarized in Table 2. Under the stress condition described in the Table 2, the Vth shift of CL-ES-structured device and BCE-structured device are − 0.51 and − 3.88 V, respectively. Additionally, the on-current shift, off-current shift, and SS value variance of the CL-ES-structured device are all lower than those of the BCE-structured device (Table 2); this is because a-IGZO-based device with CL-ES-structure can effectively prevent the contamination of a-IGZO and lower carrier trap density of a-IGZO TFT channel. Especially, when looking at the result from first 1000 s of stress, no SS value change is observed in CL-ES-structured device. This phenomenon is comparable to the 0.16 V/dec increase in SS value of BCE-structured device, as it shows that defect sites, which can form carrier traps on the surface of a-IGZO nano-film constituting CL-ES TFT back channel, are not additionally created by electrical and illumination stress. These results fully prove that CL-ES-structured device is much more stable than BCE-structured device. Figure 6c, d show the I-V curve shift of CL-ES- and BCE-structured TFTs obtained from PBTS testing. The detailed PBTS testing results are summarized in Table 3. Both CL-ES-structured TFT and BCE-structured TFT have decreased in ion current during PBTS evaluation. This is caused by the shift in Vth to the positive direction. During PBTS evaluation, residual ion current ratio [(last ion/initial ion) × 100] of the CL-ES-structured TFT with relatively smaller Vth positive shift (+ 1.94 V) is in the level of 88.2%. When compared to the BCE-structured TFT"s residual ion current ratio of 41.3%, CL-ES-structured TFT is significantly superior. This shows the important capacity difference during designing of gate drive on array (GOA) circuit. Different from NBTIS, SS value of CL-ES-structured TFT does not have significant variation ((∆SS 0.06 V/dec), or rather decreases (∆SS − 0.86) like as BCE-structured TFT. This is perhaps due to the carriers, accumulate in the inner space and interface between gate insulator and a-IGZO nano-film by positive gate bias, filling the carrier trap site at the early stage, causing decrease in carrier trap phenomenon. Moreover, the threshold voltage shift phenomenon occurs by carrier charge trapped near the interface between gate insulator and a-IGZO nano-film. Small threshold voltage shift of CL-ES-structured TFT represents that the interface and the inner space of a-IGZO are remarkably clean. In conclusion, PBTS testing also suggests that CL-ES structure and process lead to a better device reliability.

The trade-off between carrier mobility and stability in amorphous oxide semiconductor-based thin film transistors (TFTs) has been finally overcome by researchers from Tokyo Institute of Technology (Tokyo Tech) in a fabricated indium tin zinc oxide TFT. This could pave the way for the design of display technologies that are cheaper than current silicon-based technologies.

Amorphous oxide semiconductors (AOS) are a promising option for the next generation of display technologies due to their low cost and high electron (charge carrier) mobility. The high mobility, in particular, is essential for high-speed images. But AOSs also have a distinct drawback that is hampering their commercialization: the mobility/stability tradeoff.

One of the core tests of stability in TFTs is the "negative-bias temperature stress" (NBTS) stability test. Two AOS TFTs of interest are indium gallium zinc oxide (IGZO) and indium tin zinc oxide (ITZO). IGZO TFTs have high NBTS stability but poor mobility while ITZO TFTs have the opposite characteristics. The existence of this tradeoff is well-known, but thus far there has been no understanding of why it occurs.

In a recent study published in Nature Electronics, a team of scientists from Japan have now reported a solution to this tradeoff. "In our study, we focused on NBTS stability which is conventionally explained using "charge trapping." This describes the loss of accumulated charge into the underlying substrate. However, we doubted if this could explain the differences we see beteen IGZO and ITZO TFTs, so instead we focused on the possibility of a change in carrier density, or Fermi level shift, in the AOS itself," said Assistant Professor Junghwan Kim of Tokyo Tech.

To investigate the NBTS stability, the team used a "bottom-gate TFT with a bilayer active-channel structure" comprising an NBTS-stable AOS (IGZO) layer and an NBTS-unstable AOS (ITZO) layer. They then characterized the TFT and compared the results with device simulations performed using the charge-trapping and the Fermi-level shift models.

The fabrication of AOS TFTs introduces impurities, including carbon monoxide (CO), into the TFT, especially in the ITZO case. The team found that charge transfer was occurring between the AOSs and the unintended impurities. In this case the CO impurities were donating electrons into the active layer of the TFT, which caused the Fermi-level shift and NBTS instability. "The mechanism of this CO-based electron donation is dependent on the location of the conduction band minimum, which is why you see it in high-mobility TFTs such as ITZO but not in IGZO," said Kim.

Armed with this knowledge, the researchers developed an ITZO TFT without CO impurities by treating the TFT at 400 °C and found that it was NBTS stable. "Super-high vision technologies need TFTs with an electron mobility above 40 cm2 (Vs)-1. By eliminating the CO impurities, we were able to fabricate an ITZO TFT with a mobility as high as 70 cm2 (Vs)-1," said Kim.

However, CO impurities alone do not cause instability. According to Kim, "Any impurity that induces a charge transfer with AOSs can cause gate-bias instability. To achieve high-mobility oxide TFTs, we need contributions from the industrial side to clarify all possible origins for impurities."

These results could pave the way for fabrication of other similar AOS TFTs for use in display technologies, as well as chip input/output devices, image sensors and power systems.

Indium gallium zinc oxide (IGZO) is a semiconducting material, consisting of indium (In), gallium (Ga), zinc (Zn) and oxygen (O). IGZO thin-film transistors (TFT) are used in the TFT backplane of flat-panel displays (FPDs). IGZO-TFT was developed by Hideo Hosono"s group at Tokyo Institute of Technology and Japan Science and Technology Agency (JST) in 2003 (crystalline IGZO-TFT)electron mobility of amorphous silicon, which has often been used in liquid-crystal displays (LCDs) and e-papers. As a result, IGZO-TFT can improve the speed, resolution and size of flat-panel displays. It is currently used as the thin-film transistors for use in organic light-emitting diode (OLED) TV displays.

In 2012, Sharp was first to start production of LCD panels incorporating IGZO-TFT.smartphones, tablets, and 32" LCDs. In these, the aperture ratio of the LCD is improved by up to 20%. Power consumption is improved by LCD idling stop technology, which is possible due to the high mobility and low off current of IGZO-TFT.pixel-density panels for notebook applications.LCD of an ultrabook PC supplied by Fujitsu,Razer Blade 14" (Touchscreen Variant) Gaming Laptop and a 55" OLED TV supplied by LG Electronics.

IGZO"s advantage over zinc oxide is that it can be deposited as a uniform amorphous phase while retaining the high carrier mobility common to oxide semiconductors.transistors are slightly photo-sensitive, but the effect becomes significant only in the deep violet to ultra-violet (photon energy above 3 eV) range, offering the possibility of a fully transparent transistor.

The current impediment to large-scale IGZO manufacturing is the synthesis method. The most widely used technique for Transparent Conducting Oxide (TCO) synthesis is Pulsed Laser Deposition(PLD).laser is used to focus on nano-sized spots on solid elemental targets. Laser pulse frequencies are varied between the targets in ratios to control the composition of the film. IGZO can be deposited onto substrates such as quartz, single-crystal silicon, or even plastic due to its ability for low-temperature deposition. The substrates are placed in a PLD vacuum chamber, which controls oxygen pressure in order to ensure favorable electrical properties. After synthesis, the film is annealed, or gradually exposed to air to adjust to the atmosphere.

TFT active-matrix is a key technology for display manufacturing such as AMLCD and AMOLED display. Past, current and future TFT technologies are reviewed and discussed with the use of amorphous silicon (a-Si), low-temperature poly-Si (LTPS), organic and oxide semiconductors. TFT technologies based on a-Si:H and LTPS are mature enough, but the TFTs with oxide and organic semiconductors are still many issues to be solved for large scale manufacturing. Currently, display manufacturing based on a-IGZO TFT backplane is hot issue because a-Si:H production line can be easily modified to that for IGZO TFTs.

About Us: Lumiode is a fast growing, fabless semiconductor company commercializing a novel micro-LED platform delivering ultra-high brightness, low power, small form factor displays. As a leading developer of monolithic micro-LED displays, our integration of thin film transistors (TFTs) and micro-LEDs is well suited for AR/MR, head-up display (HUD) and other consumer, industrial and automotive display applications.

Position Description: We are looking for an experienced TFT process engineer. The ideal candidate will be skilled in LTPS and/or IGZO TFT process development and fabrication, ideally with experience in ramping technology from R&D to volume production. Candidates should also be able to translate process parameters into realistic simulation inputs and contribute to applicable process simulation and modeling. We are looking for a self-motivated team player who can work with all levels of our technical team. This is a great opportunity to make a big impact at a fast-growing startup. Responsibilities include:

Utilize in-depth knowledge of the relationship between materials, process, and device physics to design and execute process experiments (DOEs) to optimize TFT performance.

Test TFTs using hardware including but not limited to manual and semi-automatic probe stations, parameter analyzers, oscilloscopes, and impedance analyzers.

LCD or AMOLED, 1080p vs 2K? There are plenty of contentious topics when it comes to smartphone displays, which all have an impact on the day to day usage of our smartphones. However, one important topic which is often overlooked during analysis and discussion is the type of backplane technology used in the display.

Display makers often throw around terms like A-Si, IGZO, or LTPS. But what do these acronyms actually mean and what’s the impact of backplane technology on user experience? What about future developments?

For clarification, backplane technology describes the materials and assembly designs used for the thin film transistors which drive the main display. In other words, it is the backplane that contains an array of transistors which are responsible for turning the individual pixels on and off, acting therefore as a determining factor when it comes to display resolution, refresh rate, and power consumption.

Examples of backplane technology include amorphous silicon (aSi), low-temperature polycrystalline silicon (LTPS) and indium gallium zinc oxide (IGZO), whilst LCD and OLED are examples of light emitting material types. Some of the different backplane technologies can be used with different display types, so IGZO can be used with either LCD or OLED displays, albeit that some backplanes are more suitable than others.

Amorphous silicon has been the go-to material for backplane technology for many years, and comes in a variety of different manufacturing methods, to improve its energy efficiency, refresh speeds, and the display’s viewing angle. Today, a-Si displays make up somewhere between 20 and 25 percent of the smartphone display market.

For mobile phone displays with a pixel density lower than 300 pixels per inch, this technology remains the preferable backplane of choice, mainly due to its low costs and relatively simple manufacturing process. However, when it comes to higher resolution displays and new technologies such as AMOLED, a-Si is beginning to struggle.

AMOLED puts more electrical stress on the transistors compared with LCD, and therefore favours technologies that can offer more current to each pixel. Also, AMOLED pixel transistors take up more space compared with LCDs, blocking more light emissions for AMOLED displays, making a-Si rather unsuitable. As a result, new technologies and manufacturing processes have been developed to meet the increasing demands made of display panels over recent years.

LTPS currently sits as the high-bar of backplane manufacturing, and can be spotted behind most of the high end LCD and AMOLED displays found in today’s smartphones. It is based on a similar technology to a-Si, but a higher process temperature is used to manufacture LTPS, resulting in a material with improved electrical properties.

LTPS is in fact the only technology that really works for AMOLED right now, due to the higher amount of current required by this type of display technology. LTPS also has higher electron mobility, which, as the name suggests, is an indication of how quickly/easily an electron can move through the transistor, with up to 100 times greater mobility than a-Si.

For starters, this allows for much faster switching display panels. The other big benefit of this high mobility is that the transistor size can be shrunk down, whilst still providing the necessary power for most displays. This reduced size can either be put towards energy efficiencies and reduced power consumption, or can be used to squeeze more transistors in side by side, allow for much greater resolution displays. Both of these aspects are becoming increasingly important as smartphones begin to move beyond 1080p, meaning that LTPS is likely to remain a key technology for the foreseeable future.

The drawback of LTPS TFT comes from its increasingly complicated manufacturing process and material costs, which makes the technology more expensive to produce, especially as resolutions continue to increase. As an example, a 1080p LCD based on this technology panel costs roughly 14 percent more than a-Si TFT LCD. However, LTPS’s enhanced qualities still mean that it remains the preferred technology for higher resolution displays.

Currently, a-Si and LTPS LCD displays make up the largest combined percentage of the smartphone display market. However, IGZO is anticipated as the next technology of choice for mobile displays. Sharp originally began production of its IGZO-TFT LCD panels back in 2012, and has been employing its design in smartphones, tablets and TVs since then. The company has also recent shown off examples of non-rectangular shaped displays based on IGZO. Sharp isn’t the only player in this field — LG and Samsung are both interested in the technology as well.

The area where IGZO, and other technologies, have often struggled is when it comes to implementations with OLED. ASi has proven rather unsuitable to drive OLED displays, with LTPS providing good performance, but at increasing expense as display size and pixel densities increase. The OLED industry is on the hunt for a technology which combines the low cost and scalability of a-Si with the high performance and stability of LTPS, which is where IGZO comes in.

Why should the industry make the switch over to IGZO? Well, the technology has quite a lot of potential, especially for mobile devices. IGZO’s build materials allow for a decent level of electron mobility, offering 20 to 50 times the electron mobility of amorphous silicon (a-Si), although this isn’t quite as high as LTPS, which leaves you with quite a few design possibilities. IGZO displays can therefore by shrunk down to smaller transistor sizes, resulting in lower power consumption, which provides the added benefit of making the IGZO layer less visible than other types. That means you can run the display at a lower brightness to achieve the same output, reducing power consumption in the process.

One of IGZO’s other benefits is that it is highly scalable, allowing for much higher resolution displays with greatly increased pixel densities. Sharp has already announced plans for panels with 600 pixels per inch. This can be accomplished more easily than with a-Si TFT types due to the smaller transistor size.

Smaller IGZO transistors are also touting superior noise isolation compared to a-Si, which should result in a smoother and more sensitive user experience when used with touchscreens. When it comes to IGZO OLED, the technology is well on the way, as Sharp has just unveiled its new 13.3-inch 8K OLED display at SID-2014.

Essentially, IGZO strives to reach the performance benefits of LTPS, whilst keeping fabrications costs as low as possible. LG and Sharp are both working on improving their manufacturing yields this year, with LG aiming for 70% with its new Gen 8 M2 fab. Combined with energy efficient display technologies like OLED, IGZO should be able to offer an excellent balance of cost, energy efficiency, and display quality for mobile devices.

Innovations in display backplanes aren’t stopping with IGZO, as companies are already investing in the next wave, aiming to further improve energy efficiency and display performance. Two examples worth keeping an eye are on are Amorphyx’ amorphous metal nonlinear resistor (AMNR) and CBRITE.

This developing technology can be manufacturing on a process that leverages a-Si TFT production equipment, which should keep costs down when it comes to switching production, whilst also offering a 40 percent lower cost of production compared with a-Si. AMNR is also touting better optical performance than a-Si and a complete lack of sensitivity to light, unlike IGZO. AMNR could end up offering a new cost effective option for mobile displays, while making improvements in power consumption too.

CBRITE, on the other hand, is working on its own metal oxide TFT, which has a material and process that delivers greater carrier mobility than IGZO. Electron mobility can happily reach 30cm²/V·sec, around the speed of IGZO, and has been demonstrated reaching 80cm²/V·sec, which is almost as high as LTPS. CBRITE also appears to lend itself nicely to the higher resolution and lower power consumption requirements of future mobile display technologies.

Smartphones are already benefiting from improvements in screen technology, and some would argue that things are already as good as they need to be, but the display industry still has plenty to show us over the next few years.

To overcome the technological and economic obstacles of amorphous indium-gallium-zinc-oxide (a-IGZO)-based display backplane for industrial production, a clean etch-stopper (CL-ES) process is developed to fabricate a-IGZO-based thin film transistor (TFT) with improved uniformity and reproducibility on 8.5th generation glass substrates (2200 mm × 2500 mm). Compared with a-IGZO-based TFT with back-channel-etched (BCE) structure, a newly formed ES nano-layer ( 100 nm) and a simultaneous etching of a-IGZO nano-layer (30 nm) and source-drain electrode layer are firstly introduced to a-IGZO-based TFT device with CL-ES structure to improve the uniformity and stability of device for large-area display. The saturation electron mobility of 8.05 cm2/V s and the V th uniformity of 0.72 V are realized on the a-IGZO-based TFT device with CL-ES structure. In the negative bias temperature illumination stress and positive bias thermal stress reliability testing under a ± 30 V bias for 3600 s, the measured V th shift of CL-ES-structured device significantly decreased to - 0.51 and + 1.94 V, which are much lower than that of BCE-structured device (- 3.88 V, + 5.58 V). The electrical performance of the a-IGZO-based TFT device with CL-ES structure implies that the economic transfer from a silicon-based TFT process to the metal oxide semiconductor-based process for LCD fabrication is highly feasible.

To overcome the technological and economic obstacles of amorphous indium-gallium-zinc-oxide (a-IGZO)-based display backplane for industrial production, a clean etch-stopper (CL-ES) process is developed to fabricate a-IGZO-based thin film transistor (TFT) with improved uniformity and reproducibility on 8.5th generation glass substrates (2200 mm × 2500 mm). Compared with a-IGZO-based TFT with back-channel-etched (BCE) structure, a newly formed ES nano-layer (~ 100 nm) and a simultaneous etching of a-IGZO nano-layer (30 nm) and source-drain electrode layer are firstly introduced to a-IGZO-based TFT device with CL-ES structure to improve the uniformity and stability of device for large-area display. The saturation electron mobility of 8.05 cm 2 /V s and the V th uniformity of 0.72 V are realized on the a-IGZO-based TFT device with CL-ES structure. In the negative bias temperature illumination stress and positive bias thermal stress reliability testing under a ± 30 V bias for 3600 s, the measured V th shift of CL-ES-structured device significantly decreased to - 0.51 and + 1.94 V, which are much lower than that of BCE-structured device (- 3.88 V, + 5.58 V). The electrical performance of the a-IGZO-based TFT device with CL-ES structure implies that the economic transfer from a silicon-based TFT process to the metal oxide semiconductor-based process for LCD fabrication is highly feasible.

IGZO-TFT (Indium Galium Zinc Oxide-Thin Film Transistor) is a promising technology for controlling large display areas and large area sensors because of its very low leakage current in the off state and relatively low cost. IGZO has been used as a switching gate for a large area flat-panel detector. The photon counting capability for X-ray medical imaging has been investigated and expected for low-dose exposure and material determination. Here the design and fabrication of a charge sensitive preamplifier and analog counter using IGZO-TFT processes and its performance are reported for the first time to be used for radiation photon counting applications.

A visible-blind ultraviolet (UV) photodetector was designed based on a three-terminal electronic device of thin-film transistor (TFT) coupled with two-terminal p-n junction optoelectronic device, in hope of combining the beauties of both of the devices together. Upon the uncovered back-channel surface of amorphous indium-gallium-zinc-oxide (IGZO) TFT, we fabricated PEDOT:PSS/SnO x /IGZO heterojunction structure, through which the formation of a p-n junction and directional carrier transfer of photogenerated carriers were experimentally validated. As expected, the photoresponse characteristics of the newly designed photodetector, with a photoresponsivity of 984 A/W at a wavelength of 320 nm, a UV-visible rejection ratio up to 3.5 × 10 7 , and a specific detectivity up to 3.3 × 10 14 Jones, are not only competitive compared to the previous reports but also better than those of the pristine IGZO phototransistor. The hybrid photodetector could be operated in the off-current region with low supply voltages (<0.1 V) and ultralow power dissipation (<10 nW under illumination and ∼0.2 pW in the dark). Moreover, by applying a short positive gate pulse onto the gate, the annoying persistent photoconductivity presented in the wide band gap oxide-based devices could be suppressed conveniently, in hope of improving the response rate. With the terrific photoresponsivity along with the advantages of photodetecting pixel integration, the proposed phototransistor could be potentially used in high-performance visible-blind UV photodetector pixel arrays.

An immunosensor is proposed based on the indium-gallium-zinc-oxide (IGZO) electric-double-layer thin-film transistor (EDL TFT) with a separating extended gate. The IGZO EDL TFT has a field-effect mobility of 24.5 cm2 V-1 s-1 and an operation voltage less than 1.5 V. The sensors exhibit the linear current response to label-free target immune molecule in the concentrations ranging from 1.6 to 368 × 10-15 g/ml with a detection limit of 1.6 × 10-15 g/ml (0.01 fM) under an ultralow operation voltage of 0.5 V. The IGZO TFT component demonstrates a consecutive assay stability and recyclability due to the unique structure with the separating extended gate. With the excellent electrical properties and the potential for plug-in-card-type multifunctional sensing, extended-gate-type IGZO EDL TFTs can be promising candidates for the development of a label-free biosensor for public health applications.

In this study, InGaZnO (IGZO) thin film transistors (TFTs) with a dual active layer (DAL) structure are fabricated by inserting a homogeneous embedded conductive layer (HECL) in an amorphous IGZO (a-IGZO) channel with the aim of enhancing the electrical characteristics of conventional bottom-gate-structure TFTs. A highly conductive HECL (carrier concentration at 1.6 × 1013 cm-2, resistivity at 4.6 × 10-3 Ω∙cm, and Hall mobility at 14.6 cm2/Vs at room temperature) is fabricated using photochemical H-doping by irradiating UV light on an a-IGZO film. The electrical properties of the fabricated DAL TFTs are evaluated by varying the HECL length. The results reveal that carrier mobility increased proportionally with the HECL length. Further, a DAL TFT with a 60-μm-long HECL embedded in an 80-μm-long channel exhibits comprehensive and outstanding improvements in its electrical properties: a saturation mobility of 60.2 cm2/Vs, threshold voltage of 2.7 V, and subthreshold slope of 0.25 V/decade against the initial values of 19.9 cm2/Vs, 4.7 V, and 0.45 V/decade, respectively, for a TFT without HECL. This result confirms that the photochemically H-doped HECL significantly improves the electrical properties of DAL IGZO TFTs. PMID:25435832

In this study, InGaZnO (IGZO) thin film transistors (TFTs) with a dual active layer (DAL) structure are fabricated by inserting a homogeneous embedded conductive layer (HECL) in an amorphous IGZO (a-IGZO) channel with the aim of enhancing the electrical characteristics of conventional bottom-gate-structure TFTs. A highly conductive HECL (carrier concentration at 1.6 × 10(13) cm(-2), resistivity at 4.6 × 10(-3) Ω∙cm, and Hall mobility at 14.6 cm(2)/Vs at room temperature) is fabricated using photochemical H-doping by irradiating UV light on an a-IGZO film. The electrical properties of the fabricated DAL TFTs are evaluated by varying the HECL length. The results reveal that carrier mobility increased proportionally with the HECL length. Further, a DAL TFT with a 60-μm-long HECL embedded in an 80-μm-long channel exhibits comprehensive and outstanding improvements in its electrical properties: a saturation mobility of 60.2 cm(2)/Vs, threshold voltage of 2.7 V, and subthreshold slope of 0.25 V/decade against the initial values of 19.9 cm(2)/Vs, 4.7 V, and 0.45 V/decade, respectively, for a TFT without HECL. This result confirms that the photochemically H-doped HECL significantly improves the electrical properties of DAL IGZO TFTs.

The deposition of the top gate dielectric in thin film transistor (TFT)-based dual-gate ion-sensitive field-effect transistors (DG ISFETs) is critical, and expected not to affect the bottom gate TFT characteristics, while providing a higher pH sensitive surface and efficient capacitive coupling between the gates. Amorphous Ta2O5, in addition to having good sensing properties, possesses a high dielectric constant of ˜25 making it well suited as the top gate dielectric in a DG ISFET by providing higher capacitive coupling (ratio of C top/C bottom) leading to higher amplification. To avoid damage of the a-IGZO channel reported to be caused by plasma exposure, deposition of Ta2O5 by e-beam evaporation followed by annealing was investigated in this work to obtain sensitivity over the Nernst limit. The deteriorated bottom gate TFT characteristics, indicated by an increase in the channel conductance, confirmed that plasma exposure is not the sole contributor to the changes. Oxygen vacancies at the Ta2O5/a-IGZO interface, which emerged during processing, increased the channel conductivity, became filled by optimum annealing in oxygen at 400 °C for 1 h, which was confirmed by an x-ray photoelectron spectroscopy depth profiling analysis. The obtained pH sensitivity of the TFT-based DG ISFET was 402 mV pH-1, which is about 6.8 times the Nernst limit (59 mV pH-1). The concept of capacitive coupling was also demonstrated by simulating an a-IGZO-based DG TFT structure. Here, the exposure of the top gate dielectric to the electrolyte without applying any top gate bias led to changes in the measured threshold voltage of the bottom gate TFT, and this obviated the requirement of a reference electrode needed in conventional ISFETs and other reported DG ISFETs. These devices, with high sensitivities and requiring low volumes (˜2 μl) of analyte solution, could be potential candidates for utilization as chemical sensors and biosensors.

In this study, we investigated how the structure and oxygen flow rate (OFR) during the sputter-deposition affects the photo-responses of amorphous indium-gallium-zinc-oxide (a-IGZO)-based photodetector devices. As the result of comparing three types of device structures with one another, which are a global Schottky diode, local Schottky diode, and thin-film transistor (TFT), the IGZO TFT with the gate pulse technique suppressing the persistent photoconductivity (PPC) is the most promising photodetector in terms of a high photo-sensitivity and uniform sensing characteristic. In order to analyze the IGZO TFT-based photodetectors more quantitatively, the time-evolution of sub-gap density-of-states (DOS) was directly observed under photo-illumination and consecutively during the PPC-compensating period with applying the gate pulse. It shows that the increased ionized oxygen vacancy (VO2+) defects under photo-illumination was fully recovered by the positive gate pulse and even overcompensated by additional electron trapping. Based on experimentally extracted sub-gap DOS, the origin on PPC was successfully decomposed into the hole trapping and the VO ionization. Although the VO ionization is enhanced in lower OFR (O-poor) device, the PPC becomes more severe in high OFR (O-rich) device because the hole trapping dominates the PPC in IGZO TFT under photo-illumination rather than the VO ionization and more abundant holes are trapped into gate insulator and/or interface in O-rich TFTs. Similarly, the electron trapping during the PPC-compensating period with applying the positive gate pulse becomes more prominent in O-rich TFTs. It is attributed to more hole/electron traps in the gate insulator and/or interface, which is associated with oxygen interstitials, or originates from the ion bombardment-related lower quality gate oxide in O-rich devices.

We report two-step annealing, high temperature and sequent low temperature, for amorphous indium-gallium-zinc-oxide (a-IGZO) thin-film transistor (TFT) to improve its stability and device performance. The annealing is carried out at 300 oC in N2 ambient for 1 h (1st step annealing) and then at 250 oC in vacuum for 10 h (2nd step annealing). It is found that the threshold voltage (VTH) changes from 0.4 V to -2.0 V by the 1st step annealing and to +0.6 V by 2nd step annealing. The mobility changes from 18 cm2V-1s-1 to 25 cm2V-1s-1 by 1st step and decreases to 20 cm2V-1s-1 by 2nd step annealing. The VTH shift by positive bias temperature stress (PBTS) is 3.7 V for the as-prepared TFT, and 1.7 V for the 1st step annealed TFT, and 1.3 V for the 2nd step annealed TFT. The XPS (X-ray photoelectron spectroscopy) depth analysis indicates that the reduction in O-H bonds at the top interface (SiO2/a-IGZO) by 2nd step annealing appears, which is related to the positive VTH shift and smaller VTH shift by PBTS.

We report a tunneling contact indium-gallium-zinc oxide (IGZO) thin film transistor (TFT) with a graphene interlayer technique in this paper. A Schottky junction is realized between a metal and IGZO with a graphene interlayer, leading to a quantum tunneling of the TFT transport in saturation regions. This tunneling contact enables a significant reduction in the saturation drain voltage Vdsat compared to that of the thermionic emission TFTs, which is usually equal to the gate voltage minus their threshold voltages. Measured temperature independences of the subthreshold swing confirm a transition from the thermionic emission to quantum tunneling transports depending on the gate bias voltages in the proposed device. The tunneling contact TFTs with the graphene interlayer have implications to reduce the power consumptions of certain applications such as the active matrix OLED display.

Device characteristics changes in an a-IGZO thin film transistor under light illumination and at raised temperature have been investigated. Light exposure causes a large leakage current, which is more obvious with an increase in the illumination energy, power and the temperature. The increase in the leakage current is due to the trap assisted photon excitation process that generates electron-hole pairs and the mechanism is enhanced with the additional thermal energy. The leakage current comes from the source side because holes generated in the process drift to the source side and therefore lower the barrier height. The above mechanism has been further verified with experiments of drain bias induced shifts in the threshold voltage and the subthreshold slope.

An amorphous indium-gallium-zinc-oxide (a-IGZO) thin film transistor (TFT) was fabricated by a self-aligned imprint lithography (SAIL) method with a sacrificial photoresist layer. The SAIL is a top-down method to fabricate a TFT using a three-dimensional multilayer etch mask having all pattern information for the TFT. The sacrificial layer was applied in the SAIL process for the purpose of removing the resin residues that were inevitably left when the etch mask was thinned by plasma etching. This work demonstrated that the a-IGZO TFT could be fabricated by the SAIL process with the sacrificial layer. Specifically, the simple fabrication process utilized in this study can be utilized for the TFT with a plasma-sensitive semiconductor such as the a-IGZO and further extended for the roll-to-roll TFT fabrication.

We present a gas sensitive thin-film transistor (TFT) based on an amorphous Indium-Gallium-Zinc-Oxide (a-IGZO) semiconductor as the sensing layer, which is fabricated on a free-standing flexible polyimide foil. The photo-induced sensor response to NO₂ gas at room temperature and the cross-sensitivity to humidity are investigated. We combine the advantages of a transistor based sensor with flexible electronics technology to demonstrate the first flexible a-IGZO based gas sensitive TFT. Since flexible plastic substrates prohibit the use of high operating temperatures, the charge generation is promoted with the help of UV-light absorption, which ultimately triggers the reversible chemical reaction with the trace gas. Furthermore, the device fabrication process flow can be directly implemented in standard TFT technology, allowing for the parallel integration of the sensor and analog or logical circuits.

We present a gas sensitive thin-film transistor (TFT) based on an amorphous Indium–Gallium–Zinc–Oxide (a-IGZO) semiconductor as the sensing layer, which is fabricated on a free-standing flexible polyimide foil. The photo-induced sensor response to NO2 gas at room temperature and the cross-sensitivity to humidity are investigated. We combine the advantages of a transistor based sensor with flexible electronics technology to demonstrate the first flexible a-IGZO based gas sensitive TFT. Since flexible plastic substrates prohibit the use of high operating temperatures, the charge generation is promoted with the help of UV-light absorption, which ultimately triggers the reversible chemical reaction with the trace gas. Furthermore, the device fabrication process flow can be directly implemented in standard TFT technology, allowing for the parallel integration of the sensor and analog or logical circuits. PMID:29373524

We report a high-performance amorphous Indium-Gallium-Zinc-Oxide (a-IGZO) thin-film transistor (TFT) with new copper-chromium (Cu-Cr) alloy source/drain electrodes. The TFT shows a high mobility of 39.4 cm 2 ·V - 1 ·s - 1 a turn-on voltage of -0.8 V and a low subthreshold swing of 0.47 V/decade. Cu diffusion is suppressed because pre-annealing can protect a-IGZO from damage during the electrode sputtering and reduce the copper diffusion paths by making film denser. Due to the interaction of Cr with a-IGZO, the carrier concentration of a-IGZO, which is responsible for high mobility, rises.

In this work, a high-performance inverter based on amorphous indium-gallium-zinc oxide thin-film transistors (TFTs) has been fabricated, which consists of a driver TFT and a load TFT. The threshold voltage (Vth) of the load TFT can be tuned by applying an area-selective laser annealing. The transfer curve of the load TFT shows a parallel shift into the negative bias direction upon laser annealing. Based on x-ray photoelectron spectroscopy analyses, the negative Vth shift can be attributed to the increase of oxygen vacancy concentration within the device channel upon laser irradiation. Compared to the untreated inverter, the laser annealed inverter shows much improved switching characteristics, including a large output swing range which is close to full swing, as well as an enhanced output voltage gain. Furthermore, the dynamic performance of ring oscillator based on the laser-annealed inverter is improved.

We report a high-performance amorphous Indium-Gallium-Zinc-Oxide (a-IGZO) thin-film transistor (TFT) with new copper-chromium (Cu-Cr) alloy source/drain electrodes. The TFT shows a high mobility of 39.4 cm2·V−1·s−1 a turn-on voltage of −0.8 V and a low subthreshold swing of 0.47 V/decade. Cu diffusion is suppressed because pre-annealing can protect a-IGZO from damage during the electrode sputtering and reduce the copper diffusion paths by making film denser. Due to the interaction of Cr with a-IGZO, the carrier concentration of a-IGZO, which is responsible for high mobility, rises. PMID:28773743

In this study, flexible double-gate thin-film transistor (TFT)-based amorphous indium-galliumzinc- oxide (a-IGZO) was fabricated on a polyimide substrate. Double-gate operation with connected front and back gates was compared with a single-gate operation. As a result, the double-gate a- IGZO TFT exhibited enhanced electrical characteristics as well as improved long-term reliability. Under positive- and negative-bias temperature stress, the threshold voltage shift of the double-gate operation was much smaller than that of the single-gate operation.

Decreasing the active layer thickness has been recently reported as an alternative way to achieve fully depleted oxide thin-film transistors for the realization of low-voltage operations. However, the correlation between the active layer thickness and device resistivity to environmental changes is still unclear, which is important for the optimized design of oxide thin-film transistors. In this work, the ambient gas stability of IGZO thin-film transistors is found to be strongly correlated to the IGZO thickness. The TFT with the thinnest IGZO layer shows the highest intrinsic electron mobility in a vacuum, which is greatly reduced after exposure to O2/air. The device with a thick IGZO layer shows similar electron mobility in O2/air, whereas the mobility variation measured in the vacuum is absent. The thickness dependent ambient gas stability is attributed to a high-mobility region in the IGZO surface vicinity with less sputtering-induced damage, which will become electron depleted in O2/air due to the electron transfer to adsorbed gas molecules. The O2 adsorption and deduced IGZO surface band bending is demonstrated by the am

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey