tft lcd spacer quotation

TRIZ, Russian acronym for "Theory of Inventive Problem Solving" is now becoming well known and being applied to the various engineering field in the Western and Asian countries. However, as only few successful examples on the problems in microelectronics are found in the literature. Therefore, the previous work on a small high resolution TFT-LCD (Thin Film Transistor Addressed Liquid Crystal Display) for projection display was investigated and analyzed from TRIZ point of view to see its usefulness to solve engineering problems in the microelectronics field.There was a conflict between existence of spacers necessary to keep cell gap of LCD (Liquid crystal Display) uniform, which is related to the transmission uniformity of the screen, and serious degradation of image quality due to existence of spacers, which are recognized as a bright spot on the dark screen, as the spacer size compared with pixel size becomes large. The problem was analyzed by the TRIZ framework, and the solution to the above conflict in manufacturing an LCD for projection display was found systematically by utilizing TRIZ framework.Also, further problem of conflicting features between “productivity” and “manufacturing precision” and several other issues in production of small TFT-LCD for projection displays are studied by using TRIZ framework, and get to a new device structure and fabrication process as a FIR (Final Ideal Result). In this approach, TFT array formed on the Si wafer is transferred onto the other substrate such as glass with high strain-point, Eagle XG, and AN100, etc. used in the TFT-LCD industry. The hydrogen exfoliation technique and fragile layer are exploited to transfer device layers to the other substrates. In the present proposal, TFTs are perfect single crystal, in contrast to the poly-Si TFT used in the current LCDs, and this eliminates issue of characteristics variation stemming from the grain boundary of Poly-Si.

With the innovations in commercial-electronics products and fierce competition in the global panel industry, most panel manufacturers have adopted the small batch production mode to deal with a wide range of customization. With small batch sizes, productive yield and troubleshooting are considered the top priority, so monitoring capability conducted via virtual metrology (VM) is essentially necessary to satisfy the requirement of process quality. In this article, the real-world dataset involving the photoresist (PR) spacer heights of the color filter (CF) in the array sector of thin-film transistor liquid crystal display (TFT-LCD) manufacturing is investigated. In practice, the PR spacer heights can only be measured in an infrequent manner due to the scheduling restriction. Without taking additional sample measurements, how to design a high-accuracy VM model based on small batch sizes warrants urgent research for the TFT-LCD industry. The proposed framework can be divided into two parts. First, two novel distance-measuring methods are proposed, direct (fully connected) neural network (DNN) and

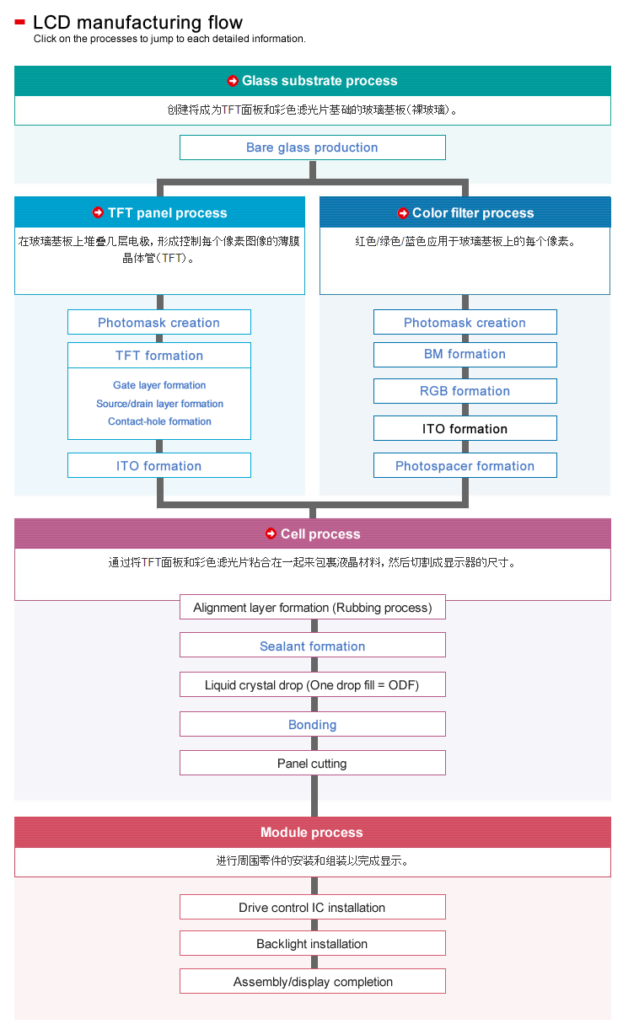

TFT-LCD technology is based on semiconductor IC manufacturing processes, and is unique in that it uses glass substrates rather than traditional silicon wafers. For the TFT manufacturing process, thin film formation, such as CVD and PVD processes, is a very important part. The ODF process has been developed for the assembly of color filters and TFT substrates, and is used in large size LCDs.

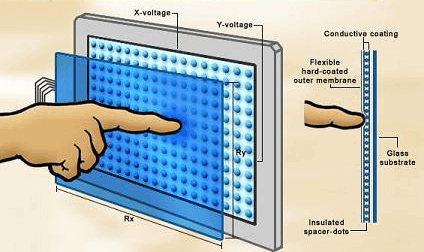

First of all, the movement and arrangement of liquid crystal molecules need electrons to drive, so in the carrier of liquid crystal – TFT glass, there must be able to conduct the part to control the movement of liquid crystal, here will use ITO (Indium TIn Oxide, transparent conductive metal) to do this thing. ITO is transparent, also known as thin film conductive crystal so that it will not block the backlight.

The different arrangement of liquid crystal molecules and the rapid movement changes to ensure that each pixel accurately display the corresponding color, and the image changes precisely and quickly, which requires precision control of the liquid crystal molecules. ITO film requires special processing, as if printed circuitry on a PCB board, drawing conductive lines throughout the LCD board.

For array panels with back-channel etched TFT structure.The main process can be divided into 5 steps (5 lightings) according to the sequence of the layers to be made and the interrelationship between the layers.

The process includes: PECVD triple layer continuous film formation, island lithography, island dry lithography and other processes. After these processes, the final amorphous silicon island for TFT is formed on the glass substrate. The graphics obtained after the process is completed are shown in the following figure.

Specific processes include: S/D metal layer sputtering into a film, S/D lithography, S/D wet lithography, channel dry lithography and other processes. After these processes, the source, drain, channel and data lines of the TFT are finally formed on the glass substrate. At this point, the TFT has been produced. The graphics obtained after the process is completed are shown in the following figure.

The process includes PECVD, photolithography, and dry lithography of vias. After these processes, the final TFT channel protective insulation layer and guide through the hole are formed on the glass substrate. The graphics obtained after the process is completed are shown in the following figure.

Color filters can be produced by various methods; photolithography is a typical method. In photolithography, color filters are produced by exposing a glass substrate coated with a photographic color resist through a photomask. The resist is hardened to form the RGB pattern of the LCD.

When making LCD panels it is impossible to produce them one by one, which is too inefficient, so multiple pieces are processed at once and separated by cutting.

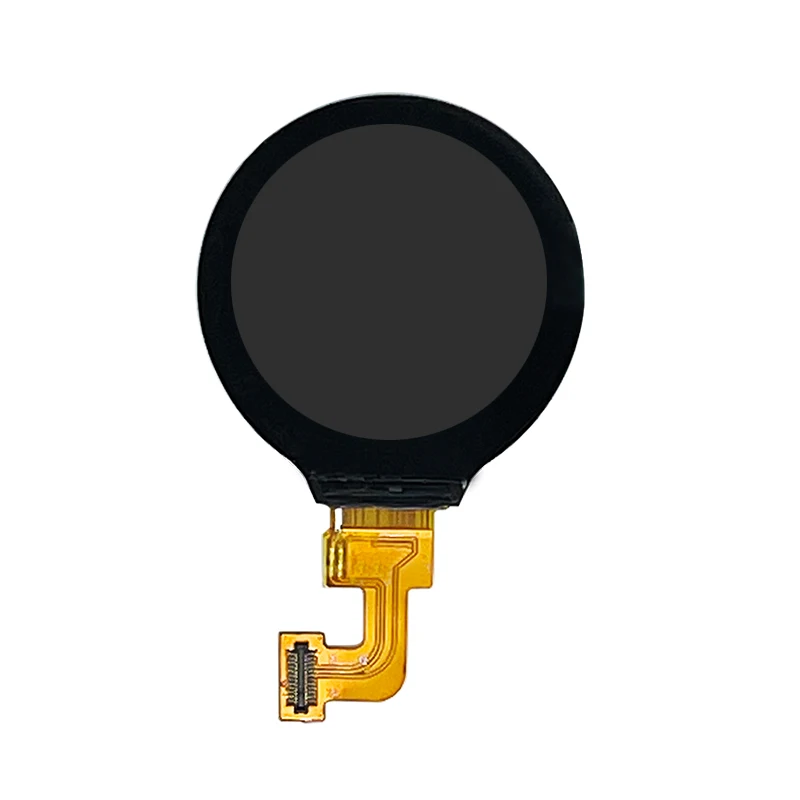

FPD (Flat Panel Display), LCD (Liquid Crystal Display), and TFT (Thin Film Transistor Display) - Flat panel displays are electronic viewing technologies used to enable people to see content in a range of entertainment, consumer electronics, personal computer, and mobile devices, and many types of medical, transportation and industrial equipment. A liquid-crystal display (LCD) is a flat-panel display or other electronic visual display that uses the light-modulating properties of liquid crystals. Liquid crystals do not emit light directly. LCDs are used in a wide range of applications including computer monitors, televisions, instrument panels, aircraft cockpit displays, and indoor and outdoor signage. Small LCD screens are common in portable consumer devices such as digital cameras, watches, calculators, and mobile telephones, including smartphones. A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display (LCD) that uses thin-film transistor (TFT) technology to improve image qualities such as addressability and contrast. TFT LCDs are used in appliances including television sets, computer monitors, mobile phones, handheld video game systems, personal digital assistants, navigation systems and projectors. TFT LCDs are also used in car instrument clusters because they allow the driver to customize the cluster, as well as being able to provide an analogue-like display with digital elements. The production of these panels utilize a variety of materials for testing, and handling including LCD Lift Pins made from Celazole® PBI, and Vespel® PI.

Optical and SEM (scanning electron microscopy) images of fabricated (a, b) CL and (c, d) CLSE pixel structures. The five white line patterns in (d) are the ITO interdigitated pixel and common electrodes. (e) Images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel. (f) The three-black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM) and (g) optical images of pixels without BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines).

Figure 3e shows images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel fabricated in our laboratory, (f) the three black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM), and (g) optical images of panel areas without the BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines). As can be seen in the image from the normal direction, the brightness and contrast of the display area with the top BM and middle BM patterns are almost the same, but the contrast of the display area without the BM is relatively lower because of the lower darkness level of the LC off pixels indicating “HITACHI”. As shown in Fig. 3g, this is due to light leaking through the aperture between the data line and adjacent common lines. Therefore, in the CL structure, the BM on the drain line is necessary to obtain a high contrast ratio by shielding light leakage. This is the same as in the conventional structure. On the contrary, there is no light leakage along the gate line through the gaps between the gate line and edges of the pixel/common electrodes, as is clearly shown in Fig. 3g. This is a unique advantage of the CL structure because the conventional structure must shield these gaps with the BM to prevent light leakage. The suppression of light leakage along the gate line in the CL structure is due to the driving scheme (see Fig. 2b,a for a comparison with the conventional structure). During the holding period (tOFF) in the conventional structure, regardless of the pixel voltage, Vp (including Vp = 0), nonzero Vgp and Vgc are always applied to keep the TFT off, and these voltages are applied to the LC layer, inducing light leakage as reported in

Figure 4a shows the gate voltage (Vg) dependence of the panel brightness, while the inset shows that of the TFT current (transfer characteristics). The gray curves are for the conventional IPS TFT-LCD with the TFT before enhancement, the common line, and the matrix BM (MBM) shown at the top of Fig. 3f. The blue curves are for the proposed CL structure with the enhanced TFT and the stripe BM (SBM) shown in the middle of Fig. 3f. In this case, enhanced TFT characteristics were obtained by using an MNOS TFT without back-channel oxidation that was enhanced by the BTS process. In both structures, the threshold voltages for panel brightness, defined by extrapolating the straight part of the brightness curves, reflect those of the TFT transfer curves defined as Vg at a drain current of 10−12 A, and they are well matched to be 4 V and 9 V, respectively. The maximum brightness for the CL structure is 137% higher than that for the conventional structure, which is due to the increase in the aperture ratio from 38 to 52% that results from the elimination of the common line and the BM covering the gate line.

(a) Dependence of panel brightness and TFT current on gate voltage for the conventional pixel structure of 38% aperture ratio (AR) with matrix black matrix (MBM) over both drain and gate lines and proposed CL pixel structure of 52% AR with strip black matrix (SBM) over only the drain lines. Transfer characteristics before and after bias temperature stress (BTS) treatment are shown in the inset. (b) Charging and (c) holding characteristics of enhanced TFT of the CL structure with gate as a common line. Vg and Vd in the TFT ON state are 30 V and +/−7 V, respectively.

To estimate the charging and holding characteristics of the MNOS-enhanced TFT in the panel, the gate TFT ON and OFF time dependences of the panel brightness were measured (Fig. 4b,c). The charging characteristics in Fig. 4b are plotted as a function of tON at tOFF = 16.6 ms, Vg = 30 V, and Vd = ± 7 V. The holding characteristics in Fig. 4c are plotted as a function of tOFF at tON = 34 μs. 95.1% charging at tON = 34 μs and 95.3% holding at tOFF = 16.6 ms indicate that the enhanced TFT has sufficient charging and holding performance to drive a standard VGA (640 × 480 pixels) panel (the number of scanning lines is estimated as tOFF/tON = 16.6/0.034 = 488).

To confirm the driving conditions for the CL structure without the BM along the gate line (with the SBM), the tOFF dependence of the contrast ratio (CR) in the CL panel was further investigated as shown in Fig. 5a, where CR is plotted as a function of tOFF for the CL panels with the matrix BM (MBM) and the strip BM (SBM). The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. The SBM and MBM panels keep CR higher than 240 with tOFF > 16.6 ms, the frame period of a display panel without flicker being noticeable to the human eye. both panels decrease CR when tOFF is less than 16.6 ms; the CR of the SBM panel decreases faster than the CR of the MBM panel. As shown in the inset, the decrease in CR was due to the increase in dark-state brightness with decreasing tOFF as light leakage increases along the gate line. This light leakage is induced by the voltage Vgp = Vgc = VgON = 30 V applied only for 34 μs during the TFT ON (charging) state, which is 1/488th the duration, tOFF = 16.6 ms, of the TFT OFF (holding) state with Vgp = Vgc = VgOFF = 0 V, but the ratio increases with decreasing tOFF and becomes effective enough to switch on LC layer and induce light leakage. However, it should be stressed again that the CL panel with the normal holding (TFT OFF) time of 16.6 ms does not suffer from the light leakage along the gate line, so the aperture ratio can be increased by removing the BM along the gate line.

Figure 6 indicates the effect of bias temperature stress (BTS) on the TFT characteristics. As the stressing time, tS, of the positive gate stress voltage, Vst = + 77 V, increases from 0 to 3600 s, the transfer (Id-Vg) curve shifts in the positive direction (Fig. 6a). Vth is defined as Vg at which Id = 10−12 A and ΔVth is defined as the Vth shift from the initial value via BTS. As shown in Fig. 6b, ΔVth increases logarithmically with increasing tS: ΔVth = 2.17 + 4.93 × log (tS). The mechanism behind the gate-stress-induced Vth shift is electron tunnel injection from the a-Si:H semiconductor into the SiOx gate insulator. For confirmation, ΔVth of MNOS TFTs with different SiOx thicknesses is plotted as a function of the electric field applied to the SiOx layer in Fig. 6c. Here, the thickness of the SiOx was varied (5, 10, 20, 50 nm), while the SiN thickness was fixed at 200 nm. The electric field applied to SiOx, Eox, was calculated using the following equation,

Effect of bias temperature stress (BTS) on TFT characteristics. (a) The transfer (Id–Vg) curve shifts in the positive direction with positive gate bias stress of Vst = + 77 V over the duration of 0–3600 s. (b) ΔVth, defined as the Vth shift from the initial value via BTS, increases logarithmically with increasing tS, following ΔVth = 2.17 + 4.93 × log (tS). (c) ΔVth of MNOS TFTs with different SiOx thicknesses from 5 to 50 nm as a function of the electric field applied to the SiOx layer.

Figure 7a shows the effect of back-channel oxidation (BCO) and passivation (PAS) on the Id-Vg characteristics of the MNOS TFT. The Id-Vg curve with Vth = 5.1 V is further enhanced to Vth = 10.9 V after BCO, although there is a slight degradation of the slope of the current increase in the sub-threshold region. The slope recovers after PAS without any change to the enhanced characteristics

(a) Effect of back-channel oxidation (BCO) and passivation (PAS) on Id–Vg characteristics of MNOS TFT. (b) Vth and Vth standard deviation, σVth, after BTS and after BCO without BTS treatments and (c) SiOX thickness as a function of position along gate-line, x.

The advantage of BCO over BTS is the uniformity of the enhanced characteristics; Fig. 7b shows the distribution of the enhanced Vth as a function of position along gate-line, x, for the MNOS TFTs connected with a 90-mm-long gate line in the TFT substrate after BTS and BCO treatments. The average value of Vth and the standard deviation, σVth, for pristine TFTs before BTS or BCO, are 5.1 V and 0.35 V, respectively. After BCO, Vth is uniformly enhanced, with an average Vth = 11 V and σVth = 0.4 V without increasing σVth. On the other hand, after BTS, Vth is nonuniformly enhanced with an average Vth = 9.3 V and σVth of 1.4 V. In particular, Vth increases linearly as a function of position along gate-line, x. As the gate SiOx thickness linearly decreases, from (54 nm) to (47 nm) with increasing x as shown in Fig. 7c, the increase in ΔVth after BTS with x is due to increase in the electric field applied to SiOx as shown in Fig. 6c and Eq. 1.

It has been shown that the Vth of the MNOS TFT is independent of the gate SiOx thickness when the thickness is more than 5 nm8a, Vth of the MNOS TFT with the BCO treatment becomes almost independent of the BCO SiOx thickness. As shown in the inset, the thickness of BCO SiOx composed of oxidized a-Si:H linearly increases with BCO processing time, and the Vth increase almost saturates at a BCO SiOx thickness greater than 5 nm. Therefore, the enhanced MNOS TFT after BCO has a uniformly high Vth that is robust to thickness fluctuations of the gate and BCO SiOx layers. BCO also has an advantage over BTS in terms of the stability of Vth as shown in Fig. 8b, which plots the annealing time dependence of Vth for BCO and BTS. In this experiment, the stoichiometry (x) of the gate SiOx was 1.78 for BTS and 1.78 and 1.9 for BCO. The annealing temperature in the N2 atmosphere was 200 °C. In the case of BTS, Vth decreased to the pristine value after approximately 5 h of annealing, while Vth decreased more slowly in the case of BCO. In particular, the annealing time required for Vth to fall to 7 V was 7.5 times longer than that of BTS. Increasing the stoichiometry (x) of the gate SiOx dramatically improved the BCO-enhanced Vth to as much as 11 V, which was stably maintained after 24 h of annealing at 200 °C.

(a) Dependence of Vth on thickness of back-channel oxidized (BCO) SiOX. The inset shows the SiOx thickness dependence on the BCO process time for RF powers of 200 W and 500 W. (b) Stability of Vth as a function of annealing time for three different TFTs with gate SiOx stoichiometry, x = 1.78 and bias temperature stress (BTS), x = 1.78 and BCO, and x = 1.9 and BCO. The temperature of annealing in the N2 atmosphere was 200 °C. (c) Band diagram of back-channel oxidized MNOS TFT. The red arrows show the electric dipoles at the SiOX/a-Si:H and a-Si:H/BCO SiOX interfaces.

A schematic band model for the MNOS TFT with the BCO treatment and the sectional structure of the interface between the a-Si:H and gate and BCO SiOx are shown in Fig. 8c. The uniformly high Vth that is independent of SiOx thickness is due to the dipoles generated at the channel and back-channel interfaces between a-Si:H and SiOx8 of reference

Masuda T, Ajichi Y, Kubo T, Yamamoto T, Shinomiya T, Nakamura M, Shimizu T, Kasai N, Mouri H, Feng XF, Teragawa M (2009) Ultra thin LED backlight system using tandem light guides for large-size LCD-TV. In: IDW09 Proceedings, pp 1857–1860

Wakabayashi K, Mitobe K, Torigoe T (2004) Laser CVD repair technology for final yield improvement method in mass and large size TFT-LCD production process. In: IDW04 Proceedings, pp 623–624

Honoki H, Nakasu N, Arai T, Yoshimura K, Edamura T (2006) In-line automatic defect inspection and repair method for possible highest yield TFT array production. In: IDW06 Proceedings, pp 849–852

A thin-film transistor (TFT) is a special type of field-effect transistor (FET) where the transistor is thin relative to the plane of the device.substrate. A common substrate is glass, because the traditional application of TFTs is in liquid-crystal displays (LCDs). This differs from the conventional bulk metal oxide field effect transistor (MOSFET), where the semiconductor material typically is the substrate, such as a silicon wafer.

TFTs can be fabricated with a wide variety of semiconductor materials. Because it is naturally abundant and well understood, amorphous or polycrystalline silicon was historically used as the semiconductor layer. However, because of the low mobility of amorphous siliconcadmium selenide,metal oxides such as indium gallium zinc oxide (IGZO) or zinc oxide,organic semiconductors,carbon nanotubes,metal halide perovskites.

Because TFTs are grown on inert substrates, rather than on wafers, the semiconductor must be deposited in a dedicated process. A variety of techniques are used to deposit semiconductors in TFTs. These include chemical vapor deposition (CVD), atomic layer deposition (ALD), and sputtering. The semiconductor can also be deposited from solution,printing

Some wide band gap semiconductors, most notable metal oxides, are optically transparent.electrodes, such as indium tin oxide (ITO), some TFT devices can be designed to be completely optically transparent.head-up displays (such as on a car windshield).The first solution-processed TTFTs, based on zinc oxide, were reported in 2003 by researchers at Oregon State University.Universidade Nova de Lisboa has produced the world"s first completely transparent TFT at room temperature.

The best known application of thin-film transistors is in TFT LCDs, an implementation of liquid-crystal display technology. Transistors are embedded within the panel itself, reducing crosstalk between pixels and improving image stability.

As of 2008LCD TVs and monitors use this technology. TFT panels are frequently used in digital radiography applications in general radiography. A TFT is used in both direct and indirect capturemedical radiography.

The most beneficial aspect of TFT technology is its use of a separate transistor for each pixel on the display. Because each transistor is small, the amount of charge needed to control it is also small. This allows for very fast re-drawing of the display.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET in which germanium monoxide was used as a gate dielectric. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. In 1966, T.P. Brody and H.E. Kunig at Westinghouse Electric fabricated indium arsenide (InAs) MOS TFTs in both depletion and enhancement modes.

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard J. Lechner of RCA Laboratories in 1968.dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).electroluminescence (EL) in 1973, using CdSe.active-matrix liquid-crystal display (AM LCD) using CdSe in 1974, and then Brody coined the term "active matrix" in 1975.

A breakthrough in TFT research came with the development of the amorphous silicon (a-Si) TFT by P.G. le Comber, W.E. Spear and A. Ghaith at the University of Dundee in 1979. They reported the first functional TFT made from hydrogenated a-Si with a silicon nitride gate dielectric layer.research and development (R&D) of AM LCD panels based on a-Si TFTs in Japan.

By 1982, Pocket TVs based on AM LCD technology were developed in Japan.Fujitsu"s S. Kawai fabricated an a-Si dot-matrix display, and Canon"s Y. Okubo fabricated a-Si twisted nematic (TN) and guest-host LCD panels. In 1983, Toshiba"s K. Suzuki produced a-Si TFT arrays compatible with CMOS integrated circuits (ICs), Canon"s M. Sugata fabricated an a-Si color LCD panel, and a joint Sanyo and Sanritsu team including Mitsuhiro Yamasaki, S. Suhibuchi and Y. Sasaki fabricated a 3-inch a-SI color LCD TV.

The first commercial TFT-based AM LCD product was the 2.1-inch Epson ET-10Hitachi research team led by Akio Mimura demonstrated a low-temperature polycrystalline silicon (LTPS) process for fabricating n-channel TFTs on a silicon-on-insulator (SOI), at a relatively low temperature of 200°C.Hosiden research team led by T. Sunata in 1986 used a-Si TFTs to develop a 7-inch color AM LCD panel,Apple Computers.Sharp research team led by engineer T. Nagayasu used hydrogenated a-Si TFTs to demonstrate a 14-inch full-color LCD display,electronics industry that LCD would eventually replace cathode-ray tube (CRT) as the standard television display technology.notebook PCs.IBM Japan introduced a 12.1-inch color SVGA panel for the first commercial color laptop by IBM.

TFTs can also be made out of indium gallium zinc oxide (IGZO). TFT-LCDs with IGZO transistors first showed up in 2012, and were first manufactured by Sharp Corporation. IGZO allows for higher refresh rates and lower power consumption.polyimide substrate.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Morozumi, Shinji; Oguchi, Kouichi (12 October 1982). "Current Status of LCD-TV Development in Japan". Molecular Crystals and Liquid Crystals. 94 (1–2): 43–59. doi:10.1080/00268948308084246. ISSN 0026-8941.

Mimura, Akio; Oohayashi, M.; Ohue, M.; Ohwada, J.; Hosokawa, Y. (1986). "SOI TFT"s with directly contacted ITO". IEEE Electron Device Letters. 7 (2): 134–6. Bibcode:1986IEDL....7..134M. doi:10.1109/EDL.1986.26319. ISSN 0741-3106. S2CID 36089445.

Sunata, T.; Yukawa, T.; Miyake, K.; Matsushita, Y.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A large-area high-resolution active-matrix color LCD addressed by a-Si TFT"s". 33 (8): 1212–1217. Bibcode:1986ITED...33.1212S. doi:10.1109/T-ED.1986.22644. ISSN 0018-9383. S2CID 44190988.

Sunata, T.; Miyake, K.; Yasui, M.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A 640 × 400 pixel active-matrix LCD using a-Si TFT"s". IEEE Transactions on Electron Devices. 33 (8): 1218–21. Bibcode:1986ITED...33.1218S. doi:10.1109/T-ED.1986.22645. ISSN 0018-9383. S2CID 6356531.

Nagayasu, T.; Oketani, T.; Hirobe, T.; Kato, H.; Mizushima, S.; Take, H.; Yano, K.; Hijikigawa, M.; Washizuka, I. (October 1988). "A 14-in.-diagonal full-color a-Si TFT LCD". Conference Record of the 1988 International Display Research Conference: 56–58. doi:10.1109/DISPL.1988.11274. S2CID 20817375.

A LCD device includes a plurality of pillar spacers disposed within liquid crystal for achieving a uniform cell gap between the color filter panel and the TFT panel of the LCD device. The pillar spacers are formed on the color filter panel and abut the TFT panel at a portion of the gate electrode exposed from an opening of an organic overcoat.

The present invention relates to a liquid crystal display (LCD) device having a uniform cell gap, and more particularly, to an improvement in the structure of pillar spacers being disposed in the liquid crystal of the LCD device. [0002]

LCD devices have been increasingly used in a variety of applications. The LCD device has a pair of opposing panels which define therebetween a cell gap for receiving therein liquid crystal. A pair of electrodes are disposed sandwiching therebetween the liquid crystal to apply a voltage across the liquid crystal, whereby orientations of the liquid crystal (LC) molecules are controlled to display an image on the front panel of the LCD device. A large number of spacers such as ball spacers or pillar spacers are disposed between both the panels to maintain a uniform cell gap irrespective of an external force being applied between the panels. [0004]

FIG. 9 shows a conventional LCD device, which includes a color filter panel including a color filter substrate [0005] 11, a TFT panel including a TFT substrate 12, and LC layer 13 encapsulated within the cell gap 13 formed between the color filter panel and the TFT panel 12. A plurality of pixels are defined on the TFT panel by electrode lines extending in the column and row directions. Each pixel includes a pixel electrode, a common electrode and a thin film transistor (TFT) for driving the pixel electrode.

A black matrix film [0006] 15, a color film 16, and an overcoat film 17 are consecutively formed on the color filter substrate 11. A gate electrode line 25 disposed for a row of TFTs is shown on the TFT substrate 12. In the region for the black matrix film 15 of the color filter substrate 11, i.e., other than the region of the effective pixel area, a pillar spacer 20A extends from the overcoat film 17 toward the TFT panel to abut the gate electrode 25 formed on the TFT substrate 12.

FIG. 10 shows another conventional LCD device, which is similar to the conventional LCD device of FIG. 9, except for the configuration of the pillar spacer [0007] 20A which extends from the gate electrode 25 toward the color filter panel to abut the overcoat film 17 on the color filter substrate 11 in the another conventional LCD device.

In both the conventional LCD devices of FIGS. 9 and 10, the cell gap [0008] 13 is maintained at a specified distance due to the balance between the compressive stress of the elastic pillar spacers 20A and the compressive load applied between the color filter substrate 11 and the TFT substrate 12.

There is a common problem in both the conventional LCD devices that a relatively small height of the pillar spacers [0009] 20A limited by the narrow cell gap 13 has an insufficient elastic force even though an elastic resin material is used for the pillar spacers 20A. In such a case, the pillar spacers 20A may have a larger strain for a minor deformation thereof, and may be subjected to a plastic deformation out of the elastic deformation range if the strain exceeds a specified deformation rate.

In addition, it is difficult for the pillar spacers [0010] 20A to expand and contract while following the changing distance of the cell gap 13, which changes due to the expansion and contraction of the liquid crystal 14 caused by a temperature change of the LCD device. More specifically, a higher ambient temperature of the LCD device expands the liquid crystal 14 and increases the distance of the cell gap 13 with an insufficient expansion of some pillar spacers 20A, thereby causing distortion of the display screen. On the other hand, a lower ambient temperature of the LCD device contracts the liquid crystal 14 while less contracting the pillar spacers 20A, thereby causing vacuum state of the LC layer 14 causing vacuum bubbles.

Further, an external force applied between both the substrates [0011] 11 and 12 may sometimes cause a plastic deformation of the black matrix film 15, color film 16 or overcoat film 17 due to the abutment of the pillar spacers 20A, thereby causing a local color change of the LCD device. SUMMARY OF THE INVENTION

In view of the above, it is an object of the present invention to provide a LCD device which is capable of suppressing the deformation and color change caused by the spacers disposed in the liquid crystal. [0012]

The present invention provides a liquid crystal display (LCD) device including: first and second panels opposing each other to form a cell gap therebetween, each of the first and second panels including a substrate and at least one first film overlying the substrate adjacent to the cell gap; liquid crystal filled in the cell gap; and a plurality of pillar spacers disposed within the liquid crystal between the first panel and the second panel, the pillar spacer being in contact with the first panel at a position exposed from an opening formed in the first film. [0013]

In accordance with the LCD device of the present invention, the height of the pillar spacers can be increased by the thickness of the first film due to provision of the opening in the first film, whereby the pillar spacers have a large elastic force and thus alleviate the variation of the cell gap. The pillar spacers may be formed on either the first panel or the second panel. [0014]

FIG. 6A is a front view of the TFT panel showing one of the pixels formed on the TFT substrate shown in FIG. 5, and FIG. 6B is a sectional view taken along line Ea-Eb in FIG. 6A. [0021]

Referring to FIG. 1, a LCD device or LCD panel assembly, generally designated by numeral [0027] 10, according to a first embodiment of the present invention includes a color filter panel 18 including a color filter substrate 11, a TFT panel 19 including a TFT substrate 12, and a LC layer including LC molecules 14 and filled in the cell gap 13 between the color filter panel 18 and the TFT panel 19. It is to be noted that some films such as an orientation film are omitted therein for a simplification purpose. The LCD device 10 has a relatively higher value for the effective opening ratio and operates in an in-plane switching (IPS) mode.

The color filter substrate [0028] 11 mounts thereon a black matrix film 15, a color film 16 and an overcoat film 17 deposited on the color filter substrate 11 in this order. In the region where the black matrix film 17 is formed, a plurality of pillar spacers 20 are formed on the overcoat film 17 at specified positions thereof, and extend toward the TFT panel 19. The top of the pillar spacer 20 abuts a gate insulation film 40 formed on the TFT substrate 12. The pillar spacer 20 has a shape of trapezoid in the longitudinal section thereof and a shape of an ellipse in the cross section thereof. The pillar spacer 20 is made of acrylic photosensitive resin of negative type, for example. The acrylic photosensitive resin may be NN-777™ supplied from JSR (Japan Synthetic Rubber) Corporation.

A plurality of gate electrode lines [0029] 25 and a plurality of common electrode lines 26 extend parallel to one another on the TFT substrate 12. An organic insulator film 39 are formed on the gate insulation film 40 covering the gate electrode lines 25 and the common electrode lines 26. The organic insulator film 39 has therein a plurality of openings 37A each exposing a portion of the gate insulation film 40 at which the pillar spacer 20 abuts the gate insulation film 40.

Referring to FIG. 2, the TFT panel [0030] 19 in the LCD device 10 of the present embodiment has conductor lines including a plurality of first common electrode lines 22 extending in the column direction, a plurality of data lines 23 extending below the respective first common electrode lines 22, a plurality of gate electrode lines 25 extending in the row direction, and a plurality of second common electrode lines 26 extending parallel to the gate electrode lines 25 and connected to the first common electrode lines 22 via through-holes. The first common electrode lines 22 and the second common electrode lines 26 define an array of pixel areas.

In each pixel area, a plurality of teeth of a comb-shape pixel electrode [0031] 27 extend parallel to a plurality of teeth of a comb-shape common electrode 29, which is connected to one of the second common electrode lines 26. Each pixel has a TFT 34 which includes a gate electrode as a part of the gate electrode line 25, a source electrode 31 from which the comb-shape pixel electrode 27 extends, and a drain 35 connected to a corresponding data line 23.

As described above, the pillar spacer [0032] 20 abuts the gate insulation film 40. In other words, the pillar spacer 20 abuts the gate electrode 25 via the gate insulation film 40 at a portion exposed from the opening 37A of the organic insulator film 39. The location of the abutment by the top 37 of the pillar spacer 20 resides outside the pixel area, and resides on the gate electrode line 25 having a relatively higher degree of hardness.

FIGS. 3A to [0033] 3C show respective sections of the TFT panel 19 shown FIG. 1, taken along lines Aa-Ab, Ba-Bb and Ca-Cb, respectively, in FIG. 2. It is to be noted that FIG. 1 is taken along line Da-Db passing through the pillar spacer 20 in FIG. 2. In the pixel area shown in FIG. 3A, the gate insulation film 40, an inorganic insulator film 41 and the organic insulator film 39 are consecutively formed on the TFT substrate 12. The first common electrode lines 22, common electrodes 29 and pixel electrodes 27 made of transparent indium-tin-oxide (ITO) are formed on the organic insulator film 39.

In the TFT region of FIG. 3B, the gate insulation film [0034] 40, an amorphous silicon layer 33, an interlayer dielectric film 38, source/drain electrodes 35 and 31, the inorganic insulator film 41 and the organic insulator film 39 are consecutively formed on the TFT substrate 12. In the pixel area shown in FIG. 3C, the gate insulation film 40, inorganic insulator film 41 and organic insulator film 39 are formed in this order on the TFT substrate 12.

As will be understood from FIGS. 3A to [0035] 3C, these regions of the TFT panel 19 are not suited for disposing the pillar spacers 20 because the gate electrode line 25 having a higher degree of hardness is not exposed after the organic insulator film 39 alone is etched. Thus, the region shown in FIG. 1, i.e., the region on the gate electrode line 25 shown in FIG. 2 is used for disposing the pillar spacer 37 because the thin gate oxide film 40 covering the gate electrode line 25 is exposed after the organic insulator film 39 alone is removed.

In the present embodiment, as understood from FIGS. 3A to [0036] 3B, the pillar spacers 20 are not disposed in the vicinity of the TFT 34 where the gate electrode, source electrode 31 and drain electrode 35 meet with one another. This configuration suppresses a change of the transistor characteristics of the TFT 34 due to electrification of the insulator film caused by friction of the pillar spacer 20.

In addition, since the pillar spacer [0037] 20 is not disposed in the vicinity of a step difference on the exposed surface such as a through-hole, the height of the pillar spacer 20 can be maintained accurate, whereby the distance of the cell gap 13 can be accurate. This also reduces the possibility of friction by the pillar spacer 20 in the direction parallel to the panel surface during the fabrication, and alleviates the difficulty in the step of bonding both the panels together. Although the presence of the pillar spacer 20 in the present embodiment makes it difficult to correct the positional relationship between both the panels 18 and 19 after the bonding thereof, this may suppress the occurrence of leakage light by suppressing the correction itself of the positional relationship.

Referring to FIG. 4, there is shown another section of the LCD device of FIG. 1, wherein the pillar spacer [0038] 20 is not disposed. The TFT substrate 12 mounts a polarizing plate 46 on the external surface thereof, and mounts the gate insulation film 40, inorganic insulator film 41, organic insulator film 39 and an orientation film 47 consecutively formed on the internal surface of the TFT substrate 12.

The process for forming the pillar spacers [0040] 20 in the present embodiment will be described hereinafter, with reference to FIG. 4. A gate insulation film 40, an inorganic insulator film 41, an organic insulator film 39 and an orientation film 47 are consecutively formed on a TFT substrate 12, followed by patterning the orientation film 47 and the organic insulator film 39 to form openings (37A in FIG. 1) therein at specified locations.

A black matrix film [0041] 15, one of color films 16 and an overcoat film 17 are consecutively formed on a color filter substrate 11, followed by coating the overcoat film 17 with an acrylic photosensitive resin of negative type. The acrylic photosensitive resin film is then subjected to exposure and development for patterning to form pillar spacers 20 having a uniform height. Since the pillar spacers 20 have a larger height by a value corresponding to the thickness of the organic insulator film 39 compared to the conventional pillar spacers 20A, the pillar spacers 20 in the present embodiment have a higher elasticity over the conventional LCD device. The larger elasticity of the pillar spacers 20 supports the cell gap 13 with superior stability.

Thereafter, the color filter panel [0042] 18 including the substrate 11 and the TFT panel 19 including the substrate 12 are bonded together with a cell gap distance of several micrometers. Liquid crystal 14 is then injected into the cell gap 13 and encapsulated therein by sealing the outer periphery of the resultant panels 18 and 19.

In the configuration of the present embodiment, the height of the pillar surfaces [0043] 20 is increased by forming an opening 37A in the organic insulator film 39 on the TFT substrate 12. This reduces the strain of the pillar spacers 20 with respect to a specified amount of depression or contraction. That is, the pillar spacers 20 have a larger elasticity and a larger maximum amount of elastic deformation, whereby the liquid crystal 14 expanding or contracting due to rise or fall of the ambient temperature allows the pillar spacers 20 to suitably follow the expansion and the contraction of the cell gap 13. This prevents a defect on the display screen at a higher temperature, and prevents vacuum bubbles in the liquid crystal 14 at a lower temperature.

In the structure wherein the pillar spacers [0044] 20 abut the gate electrode 25 with an intervention of an inorganic gate insulator film 40, the cell gap 13 is assured to have a more uniform distance compared to the case that the pillar spacers abut the organic insulator film 39 having a lower degree of hardness.

In the structure of the above embodiment, the pillar spacers [0045] 20 are formed on the overcoat film 17 on the color filter panel 18. However, the pillar spacers 20 may be formed on the color film 16 or the black matrix film 15 exposed from an opening formed in the overcoat film 17 or an opening formed in the overcoat film 17 and the color film 16. This further increases the height of the pillar spacers 20 and increases the elasticity of the pillar spacers 20.

Referring to FIG. 5, a LCD panel according to a second embodiment of the present invention is similar to the LCD panel of the first embodiment except for the operational mode of the LCD panel and the substrate on which the pillar spacers are formed. The LCD panel of the present embodiment operates with a twisted nematic mode. It is to be noted that depiction of the organic insulator film [0046] 39 is omitted in the drawing for a simplification purpose.

The black matrix film [0047] 15, color film 16 and overcoat film 17 consecutively formed on the inner surface of the color filter substrate 11 have openings 54 therein at the locations opposing the gate electrode 65 on the TFT panel 19A. The opening 54 is implemented by forming an opening 15 ain the black matrix film 15, forming an opening 16 aoverlapping the opening 15 aand patterning the overcoat film 17 to etch the same at the opening 16 a. The opening 54 exposes therefrom a portion of the color filter substrate 11, on which a pillar spacer 20 is formed. The pillar spacer 20 extends from the color filter panel 18A toward the TFT panel 19A and directly abuts the gate electrode line 65.

Referring to FIG. 6A, the TFT substrate [0048] 11 in the second embodiment mounts thereon a plurality of data lines 62 extending in the column direction, a plurality of gate electrode lines 65 extending in the row direction, and a plurality of pixels defined by adjacent gate electrode lines 65 and adjacent data lines 62. Each pixel includes a transparent pixel electrode 68 having an area substantially equal the effective area of the pixel, and a TFT 64 disposed at a corner portion of the pixel in association with the pixel electrode 68. The TFT 64 includes a gate electrode extending from a corresponding gate electrode line 65, a source electrode connected to a corresponding pixel electrode 68 and a drain electrode 69 extending from a corresponding data line 62.

Referring to FIG. 6B depicting the TFT panel [0049] 19A shown in FIG. 6A, a gate insulation film 70 is formed on the TFT substrate 12, allowing the data lines 62 to extend thereon. A thin inorganic insulator film 71 is formed on the gate insulation film 70 and the data lines 62, and a transparent pixel electrode 68 is formed on the thin inorganic film 71 at the location defined by the adjacent data lines 62.

The pillar spacers [0050] 20 are disposed outside the pixel area, i.e. the area for the pixel electrode, and have respective top surfaces 67 abutting the gate electrode lines 65 having a higher degree of hardness.

Referring to FIG. 7, a modification from the second embodiment is such that the pillar spacer [0051] 20 is formed on the gate electrode line 65, extends and abuts a portion of the color filter substrate 11 exposed from the opening 54 which is similar to the opening 54 in FIG. 5.

Referring to FIG. 8, another modification from the second embodiment is such that the pillar spacer [0052] 20 penetrates the black matrix film 15, color film 16 and overcoat film 17 at an opening 54A, to abut the gate electrode line 65 formed on the TFT panel 19C. More specifically, the pillar spacers 20 are formed on the color filter substrate 11 before the black matrix film 15, color film 16 and overcoat film 17 are formed. The pillar spacers 20 are made of a material having a lower wettability to the materials for the black matrix film 15, color film 16 and overcoat film 17. Examples of such material for the pillar spacers 20 include silicon-based resins and fluorine-based resins, such as having a contact angle of 30 degrees or higher with respect to water. The material having a lower wettability may be used for the entire body of the pillar spacer 20 or may be used as a coat film for coating the surface of the body of the pillar spacer 20.

In the another modification shown in FIG. 8, after the pillar spacers [0053] 20 are formed on the color filter substrate 11, the black matrix film 15, color film 16 and overcoat film 17 are consecutively and selectively formed in the area other than the areas where the pillar spacers 20 are formed, thereby allowing the pillar spacers 20 protruding from the overcoat film 17 at the opening 54A to abut the gate electrode line 65 on the TFT panel 19C. This also increases the effective height of the pillar spacers 20 acting as elastic members.

As described above, the present invention achieves suppression of a defect in the display panel or variation of brightness caused by insufficient elasticity of the pillar spacers. [0054]

1. A liquid crystal display (LCD) device comprising: first and second panels opposing each other to form a cell gap therebetween, each of said first and second panels including a substrate and at least one first film overlying said substrate adjacent to said cell gap; liquid crystal filled in said cell gap; and a plurality of pillar spacers disposed within said liquid crystal between said first panel and said second panel, said pillar spacer being in contact with said first panel at a position exposed from an opening formed in said first film.

2. The LCD device as defined in claim 1, wherein said first and second panels are thin film transistor (TFT) panel and color filter panel, respectively, and said first film is an organic insulator film.

5. The LCD device as defined in claim 1, wherein said first and second panels are color filter panel and thin film transistor (TFT) panel, respectively, and said at least one first film includes a black matrix film, a color film and an overcoat film.

7. The LCD device as defined in claim 5, wherein said opening is formed by forming said black matrix film, color film and overcoat film after forming said pillar spacers.

8. The LCD device as defined in claim 7, wherein at least a surface of said pillar spacers is made of a material having a contact angle of 30 degrees or higher with respect to water.

9. The LCD device as defined in claim 1, wherein said pillar spacers are disposed outside an area where a thin film transistor is formed or a vicinity thereof.

11. The LCD device as defined in claim 1, wherein said pillar spacer is in contact with said second panel at a position exposed from an opening formed in said first film of said second panel.

Liquid crystal display device having column spacer receiving members formed of the same material as a material of one of the pair of electrodes for applying an electric field to the liquid crystal material

Due to the Plug"n Play concept and the completeness of the MxxEVKs they can be used either for evaluating the Mxx SoM products or setting up a prototype. The MxxDK includes the optional TFT display with touch screen and features a display size of 17,7cm (7"").

Hot Tags: wafer spacer of tyvek, China, manufacturers, suppliers, factory, customized, wholesale, price, quality, quotation, in stock, free sample, made in China, blue wipes, nav ge cleaning swab, ESD Products exporters, bemcot m, Long handled Texwipe Polyester Swabs, ESD Anti Static Bag exporters

Pacer offers an extensive range of colour TFT LCD panels from 1.8″ through the popular 3.5″ and 5.7″ sizes to 82″. Our range includes sunlight readable panels from 5.6″ to 70″, bar cut panels, and SMART TFT displays with built-in control. We offer TFT displays with high brightness, high contrast ratio, wide viewing angle, wide temperature operation, longer lamp life, and lower power consumption.

TFT displays are used extensively in many industrial, commercial and scientific applications, including ATMs, POS terminals, kiosks, security systems, lottery and gambling gaming machines, medical equipment, factory automation, digital advertisement signage, transportation information, and marine equipment.

TFT technology is being used to replace Mono LCD in many applications, and Raystar Optronics now offers a 5.2″ TFT module designed specifically to fit the footprint of the industry standard RG24064-series 240×64 mono graphic STN LCD. The RFS520A can replace traditional STN displays of 8×2 or 16×2 format as it shares the same 16 pin footprint.

Our TFT modules are fully supported with a variety of options including wide operating temperatures, high brightness and contrast, built-in DC-DC and temperature compensation circuitry and most with white LED backlights. Resistive Touchscreens and Projected Capacitive Touchscreens are available for most models. Many panels can be configured as a kit – see our Interface Kits page for more details.

IMPORTANT ANNOUNCEMENT – Mitsubishi has decided to end production of TFT-LCD modules, as the company is no longer able to maintain the products’ competitiveness after significant price falls in the global market. Production of TFT-LCD modules is scheduled to end in June 2022 with a Last Time Buy date of June 2021. Please contact us as soon as possible to discuss last time buy or identification of suitable alternative displays.

Raystar is a professional TFT (Thin Film Transistor) module manufacturer. Whether you need a TFT display with control board, high brightness, wide viewing angle, monochrome or bar type, we have TFT active matrix display models for you to choose from.

LITEMAX® Industrial Display solution provide a wide range of reliable displays from 5.7″ to 85″ including LCD panel modules, open frame LCD displays, outdoor displays, and panel mount monitors. LITEMAX have developed and focused on LCD display technologies such as high brightness technology, optical bonding solutions, and color enhancement technology that bring more add-on value to enhance their products.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey