tft lcd source driver ic free sample

DMC-16230H : Monochrome-Character. Size:n/a Display Format:16*2 Contrast Ratio:3.5:1 Luminance:n/a Backlight:no Backlight Product Category:monochrome-character Type:reflective LCD Mode:clear Viewing Direction: 6:00 Interface: N/a View Angle (h V):n/a N/a Temperature: Medium Extended Temperature.

SA03-11SRWA : Material: Gaaias , Wavelength: 640nm. The Super Bright Red source color devices are made with Gallium Aluminum Arsenide Red Light Emitting Diode. CHARACTER APPEARANCE. INCH DIGIT HEIGHT. MOUNTING ON P.C. BOARDS OR SOCKETS. RUGGED. Notes: 1. All dimensions are in millimeters (inches), Tolerance is �0.25(0.01")unless otherwise noted. 2. s are subject to change whitout notice. Par t No. Dic m A Min.

TLC5970 : 3-Channel , 12-Bit PWM LED Driver W/ Buck DC-DC Converter And Differential Signal Interface The TLC5970 is a three-channel, constant-current sink driver with a buck dc/dc converter and a differential signal interface. Each channel has individually adjustable currents with 4096 PWM grayscale (GS) steps and 128 constant-current sink steps for dot correction.

LH N974-KN-1 : Standard LED - SMD Hyper Red, 645nm 15mcd, 20mA. The OSRAM CHIPLED SMT LED series comes in a small package and is an ideal choice for space-constrained applications, including key / LCD backlighting, eraser arrays, narrow distance displays, or indicator lamps for external modems. OSRAM CHIPLED devices are ideal for designs when high power operating.

PC20-7-TO8 : Photodiodes Low Capacitance 5.05mm Dia Area. s: Manufacturer: Pacific Silicon Sensor ; Product Category: Photodiodes ; RoHS: Details ; Lens Type: Clear ; Type: Low Capacitance PIN Photodiode ; Photodiode Material: Silicon ; Peak Wavelength: 950 nm to 1064 nm ; Maximum Reverse Voltage: 50 V ; Maximum Dark Current: 0.5 nA ; Maximum Rise Time: 50 ns ; Package.

SSL-LX30FT4GD : LEDs -; LED T-3MM 565NM GREEN DIFF. s: Color: Green ; Lens Style/Size: Round with Domed Top, 3mm, T-1 ; Millicandela Rating: 9mcd ; Voltage - Forward (Vf) Typ: 2.2V ; Wavelength - Dominant: - ; Wavelength - Peak: 565nm ; Current - Test: 20mA ; Viewing Angle: 100� ; Lens Type: Diffused, Tinted ; Luminous Flux @ Current - Test: - ; Package / Case: Radial.

HSMD-C191 : Agilent HSMD-C191 Low Profile Chipled. This series of ChipLEDs is designed with the smallest footprint to achieve high density of components on board. The HSMx-C191 has the industry standard 0.8 mm footprint. Its low 0.6 mm profile and wide viewing angle make this LED exceptional for backlighting applications. The available colors in this surface mount series are HER, orange, yellow, green,.

SEL1x10x : Uni-Color LED Lamp. Absolute maximum ratings (Ta=25�C) Symbol IF IFP VR Top Tstg Unit mA mA/�C V �C Rating to +100 Condition Above f=1kHz, tw100�s Electrical Optical characteristics (Ta=25�C) Part Number Forward voltage Reverse current Intensity Peak wavelength Spectrum half width VF Condition IR Condition IV Condition P Condition Chip material (V) IF (�A) VR (mcd) IF (nm).

SHE124PGH : High Brightness Led Lamp. Green Colored lens type 5mm(T-13/4) all plastic mold type Viewing angles : 40� Super luminosity Application Traffic Signal Massage Board Variable message signs(VMS) Power Dissipation Forward Current * Peak Forward Current Reverse Voltage Operating Temperature Storage Temperature 260 for 5 seconds * Soldering Temperature Tsol *1.Duty ratio = 1/16, Pulse.

HT16L21 : RAM Mapping 32×4 LCD Driver The HT16L21 device is a memory mapping and multi-function LCD controller/driver. The display segments of the device are 128 patterns (32 segments and 4 commons) display. It can also support LED drive outputs on certain Segment pins. The software configuration feature of the HT16L21 device makes it suitable for multiple LCD applications.

PT-121-B-C11-EPA : LED Lighting Modules Blue 462nm 540lm @ 30A. » » » LEDs - Engines/Modules: Packaged Functional Assemblies - Blue LEDs - Engines/Modules: Packaged Functional Assemblies - Blue LED Engines and LED Modules represent products that consist of integrated LED solutions. At present, there is no consistently used application definition used.

OPB900W55Z : Photointerruptors Slotted Opt Switch. s: Manufacturer: Optek ; Product Category: Photointerruptors ; RoHS: Details ; Sensing Method: Transmissive ; Maximum Reverse Voltage (Emitter): 2 V ; Slot Width: 9.5 mm ; Aperture Width: 1.27 mm ; Output Device: Photologic, Totem Pole ; Power Dissipation: 300 mW ; Maximum Fall Time: 70 ns ; Maximum Operating.

LCM-480234GF-40CG : Display Modules - LCD, OLED, Graphic *; LCD TFT 4.0" MODULE W/NTSC DEC. s: Display Type: TFT - Color LCD ; Display Mode: * ; Backlight: CCFL - White ; Dot Size: - ; Viewing Area: 82.11mm L x 61.77mm W ; Dot Pixels: 480 x 234 ; Dot Pitch: - ; Interface: -.

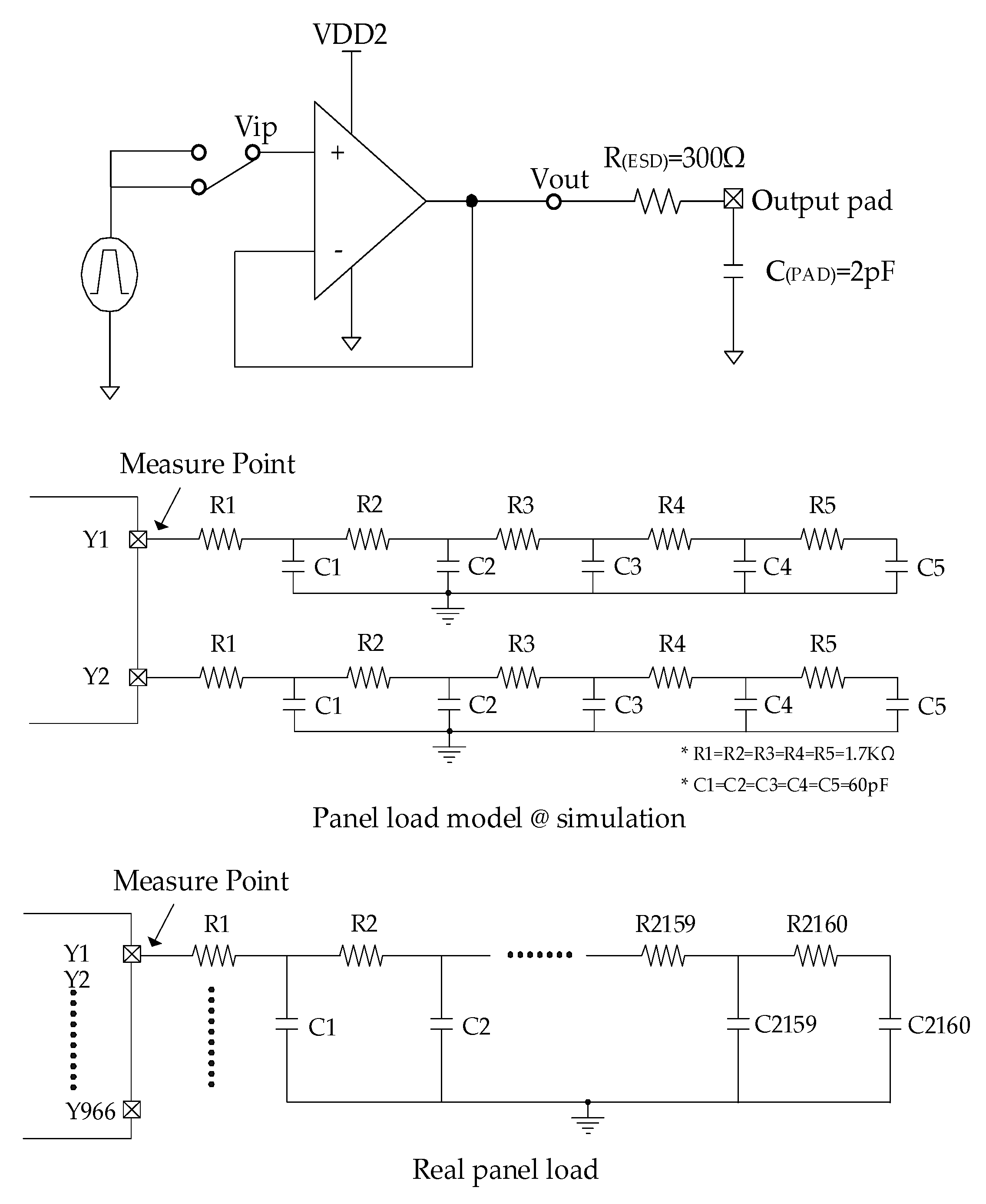

Since the reference voltages are connected to all channels, many DACs may use the same reference voltage. The more DACs there are connected to a single reference voltage, the larger the required C-DAC settling time. This study simulates the settling time for different numbers of connected DACs using a 0.35-μm 5-V CMOS model. Figure 11 shows the simulated results where the settling time is measured at 99.9% of its final voltage for a full swing (0.266 V ~ 4.75 V). The settling time is 5.2 μs when 200 DACs are connected to a single reference voltage. Although a column driver IC contains several hundreds or even up to a thousand DACs, these DACs are distributed to 256 (28) reference voltages. This means that not all the DACs are connected to a single reference voltage. A typical UXGA (1600×1200) display has a pixel clock frequency of 162 MHz and a horizontal scanning time of 9.877 μs [4]. Hence, the proposed column driver is suitable for UXGA displays.

Due to the limited silicon area, the proposed LCD column driver has only four channels. The 10-bit LCD column driver with R-DAC and C-DAC was fabricated using a 0.35-μm 5-V CMOS technology. Table I shows the device sizes used in the proposed column driver, where Rtop, Rmid, Rbot, and Ri are designated in Figure 7. Figure 12 is a photograph of the die. Except for the resistor string of the R-DAC, the die area is 0.2×1.26 mm2 for four channels. Each RGB digital input code is 10-bits wide.

The Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) are typically measured for a DAC. However, it is difficult to determine these two specifications for a nonlinear DAC. To demonstrate the performance of the proposed circuit, the nonlinear gamma voltages are not applied to the R-string and the resistor values of the resistor string are made equal. Since an LCD panel needs several column drivers, the uniformity of different drivers is very important. Figure 13 shows the measured transfer curves of a DAC for eight off-chip column drivers. To show the deviation between different chips, Figure 14 provides an

enlarged view of the transfer curves, where the maximum deviation is 3.5 mV from the mean. This deviation is mainly due to process variations. The approach in this study uses no error correction. Hence, the deviation can be reduced by applying an offset canceling technique to the buffer amplifier. Figures 15(a) and (b) show the DNL values for positive and negative polarities, respectively. Figures 16(a) and (b) show the INL values for positive and negative polarities, respectively. The combination of R-DACs and C-DACs creates two groups of DNL values. The maximum DNL and INL values are 3.83 and 3.84 LSB, respectively. This study uses a 1-LSB voltage of 2.44mV to calculate the INL and DNL values. The linearity, however, is less important than the deviations between off-chip drivers for LCD drivers [2].

Figure 17 shows the measured output waveforms of two neighboring channels under dot inversion for the RGB digital inputs of ‘1111111111.’ Here, the voltage levels for negative and positive polarities are 0.266 V and 4.75 V, respectively. A load resistor of 5 kΩ and a capacitor of 90 pF were used. Figure 18 shows a similar waveform for ‘0000000000’ inputs, where the corresponding voltage levels for negative and positive polarities are 2.425 V and 2.598 V, respectively. These two figures show that the settling time is within 3 μs, which is smaller than that of previously published work [2] and standard UXGA displays [5]. Table II summarizes the performance of the proposed column driver IC. The average area per channel is 0.063 mm2, which is smaller than the reported areas of fully R-DAC-based column drivers [5, 8]. These experimental results show that the proposed column driver is suitable for UXGA LCD-TV applications.

A fully digital driving circuit for thin-film transistor liquid crystal display can offer benefits, including less power consumption and a shortened design schedule. Using the pulsewidth signal to control the moment to stop the ramp voltage, the pixel voltage can be set accurately. In this paper, the possible issues of power consumption, device nonuniformity, and parasitic capacitance are well-studied to prove the feasibility and advantages of the digital driving method. It is prospectively…Expand

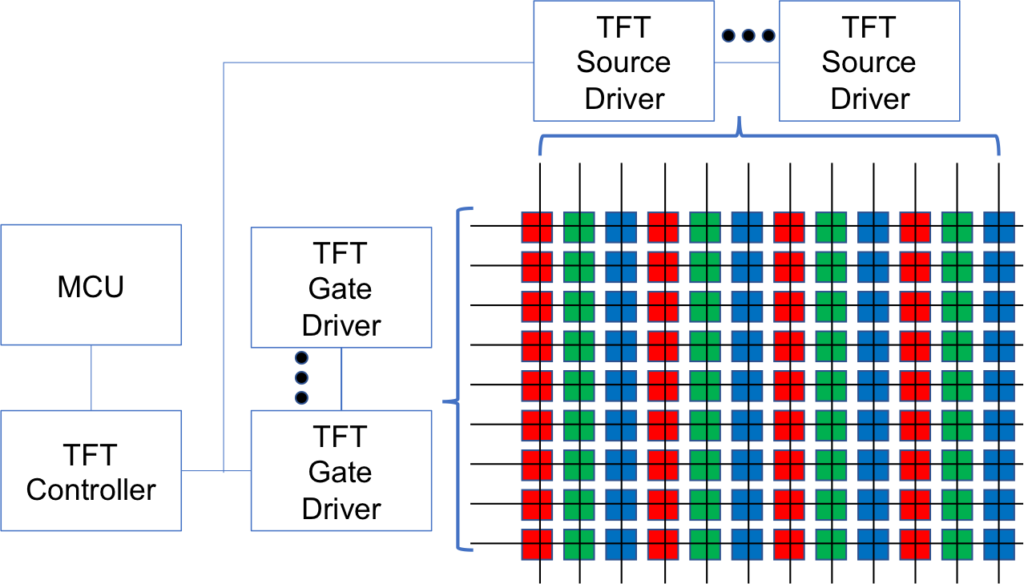

Driver ICs are critical components of TFT-LCD panels. Driver IC receives image data and delivers precise analog voltages or currents to activate the pixels on the display. When voltage is applied to the liquid crystal within each pixel cell, the liquid crystal is bent, thereby changing the intensity of light that passes through each individual pixel. Combined with the colour filter on the front glass substrate, each pixel generates its own colours which, together with other pixels, make up the whole image on the panel.

Driver ICs for mobile phones include gate drivers and source drivers. Gate drivers turn on the transistor within each pixel cell on the horizontal row on the panel. When the transistors are turned on, source drivers will generate voltages that are applied to the liquid crystal within each pixel cell on that row for data input. The combination determines the colours generated by each pixel. Small-sized panel applications, such as mobile phones, require one source driver and one gate driver, which are integrated into a single chip due to space and cost considerations. Large-sized panel applications, such as television display or desktop monitor, normally have multiple gate drivers and source drivers which are installed separately on the panel.

Resolution and number of channels: Resolution refers to the number of pixels in width dimension multiplied by the number of pixels in height dimension. For example, a WVGA colour display screen with 480 x 800 pixels has 1,440 pixels from side to side and 800 pixels from top to bottom, and therefore it has a total number of 384,000 pixels (480 x 800 pixels). Each pixel is a sample of an original image and more samples typically provide more accurate representations of the original image. Therefore, resolution usually determines the level of fine detail within an image displayed on a panel. Each pixel is usually made up of one red column, one green column and one blue column. These three primary colours are combined to make a wide range of colours. For example, a colour display screen with 480 x 800 pixels has 480 red columns, 480 green columns and 480 blue columns for a total of 1,440 columns and 800 rows. Therefore, the display drivers ICs need to drive 1,440 column outputs and 800 row outputs.

Colour depth: Colour depth is the number of colours that can be displayed on a screen, which is determined by the number of shades of a colour, also known as grayscale, which can be shown by panel. The number of distinct colours that can be generated by a pixel depends on the number of bits of the driver IC.

Higher level of integration: Due to the size constraint of mobile phones, the space available for components is usually limited. In order to stay competitive in the market, customers demand for higher levels of integration and simpler module assembly process to manufacture more compact panels and reduce unit costs. Small-sized panel applications require one source driver, one gate driver and timing controller which can be installed as separate semiconductors or as an integrated single-chip driver. Display driver IC manufacturers aim to offer highly integrated chips combining the source driver, gate driver and timing controller, as well as other functional circuits such as memory, power circuit and image processors, into one single chip. Due to the size and power constraints of such driver IC, single-chip driver IC is generally more complex to design.

Driver ICs are critical components of TFT-LCD panels. Driver IC receives image data and delivers precise analog voltages or currents to activate the pixels on the display. When voltage is applied to the liquid crystal within each pixel cell, the liquid crystal is bent, thereby changing the intensity of light that passes through each individual pixel. Combined with the colour filter on the front glass substrate, each pixel generates its own colours which, together with other pixels, make up the whole image on the panel.

Driver ICs for mobile phones include gate drivers and source drivers. Gate drivers turn on the transistor within each pixel cell on the horizontal row on the panel. When the transistors are turned on, source drivers will generate voltages that are applied to the liquid crystal within each pixel cell on that row for data input. The combination determines the colours generated by each pixel. Small-sized panel applications, such as mobile phones, require one source driver and one gate driver, which are integrated into a single chip due to space and cost considerations. Large-sized panel applications, such as television display or desktop monitor, normally have multiple gate drivers and source drivers which are installed separately on the panel.

Resolution and number of channels: Resolution refers to the number of pixels in width dimension multiplied by the number of pixels in height dimension. For example, a WVGA colour display screen with 480 x 800 pixels has 1,440 pixels from side to side and 800 pixels from top to bottom, and therefore it has a total number of 384,000 pixels (480 x 800 pixels). Each pixel is a sample of an original image and more samples typically provide more accurate representations of the original image. Therefore, resolution usually determines the level of fine detail within an image displayed on a panel. Each pixel is usually made up of one red column, one green column and one blue column. These three primary colours are combined to make a wide range of colours. For example, a colour display screen with 480 x 800 pixels has 480 red columns, 480 green columns and 480 blue columns for a total of 1,440 columns and 800 rows. Therefore, the display drivers ICs need to drive 1,440 column outputs and 800 row outputs.

Colour depth: Colour depth is the number of colours that can be displayed on a screen, which is determined by the number of shades of a colour, also known as grayscale, which can be shown by panel. The number of distinct colours that can be generated by a pixel depends on the number of bits of the driver IC.

Higher level of integration: Due to the size constraint of mobile phones, the space available for components is usually limited. In order to stay competitive in the market, customers demand for higher levels of integration and simpler module assembly process to manufacture more compact panels and reduce unit costs. Small-sized panel applications require one source driver, one gate driver and timing controller which can be installed as separate semiconductors or as an integrated single-chip driver. Display driver IC manufacturers aim to offer highly integrated chips combining the source driver, gate driver and timing controller, as well as other functional circuits such as memory, power circuit and image processors, into one single chip. Due to the size and power constraints of such driver IC, single-chip driver IC is generally more complex to design.

This website is using a security service to protect itself from online attacks. The action you just performed triggered the security solution. There are several actions that could trigger this block including submitting a certain word or phrase, a SQL command or malformed data.

![]()

This website is using a security service to protect itself from online attacks. The action you just performed triggered the security solution. There are several actions that could trigger this block including submitting a certain word or phrase, a SQL command or malformed data.

The present invention relates to the technical field of liquid crystal display, and particularly to a source driver, a driving circuit and a driving method for TFT-LCD.

The thin film transistor liquid crystal display (TFT-LCD) is widely used in consumer electronics such as television, computer, mobile phone and the like. Usually, the TFT-LCD comprises a liquid crystal panel having pixel units arranged in a matrix, wherein the driving circuit is provided to drive the pixel units to display.

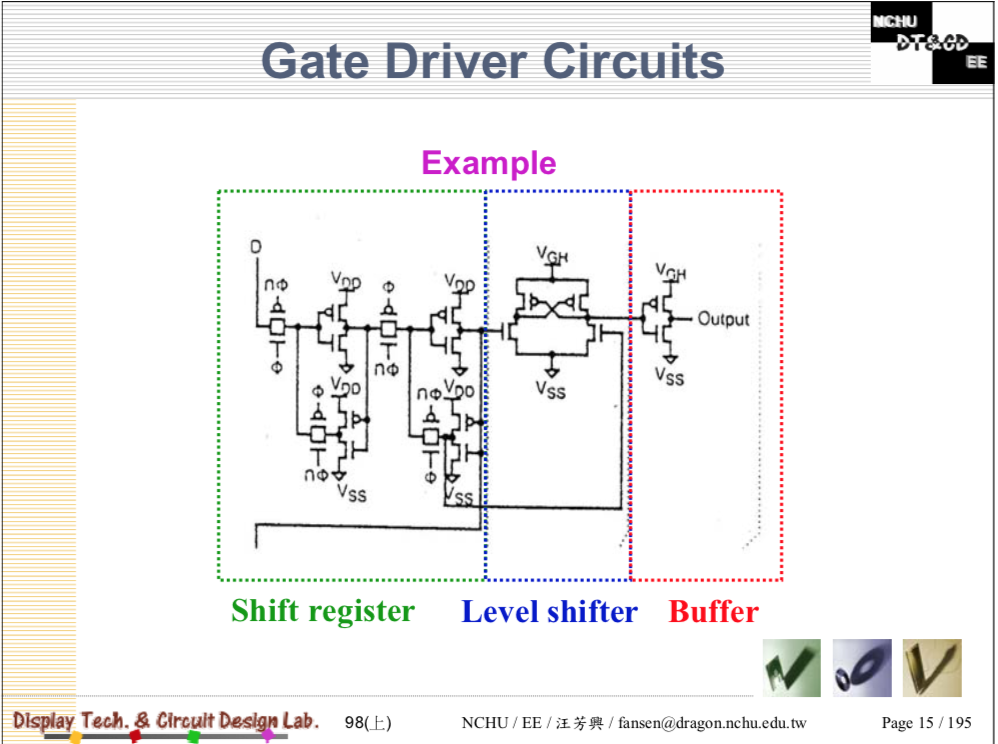

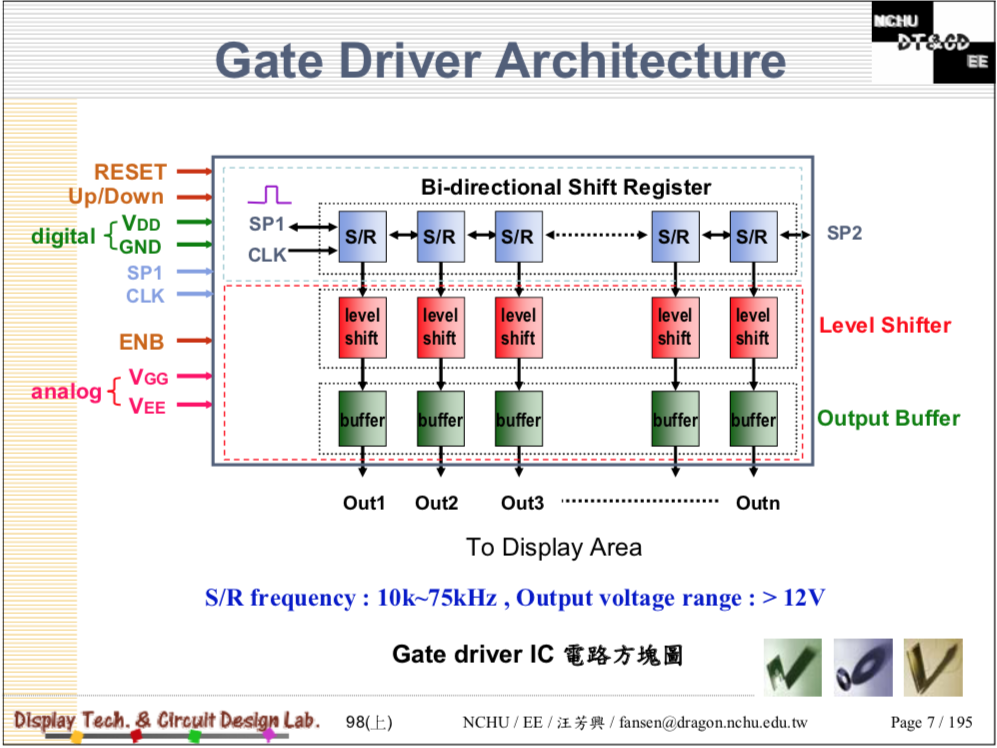

FIG. 1 schematically illustrates a circuit block diagram of a typical TFT-LCD. Referring to FIG. 1, the TFT-LCD device comprises a liquid crystal panel having m×n pixel units arranged in a matrix, m source lines (also called data lines) S1 to Sm and n gate lines G1 to Gn which are intersected with each other and thin film transistors arranged at points where the data lines and the gate lines intersect, source drivers for providing data to the data lines S1 to Sm of the liquid crystal panel, and gate drivers for providing scan pulses to the gate lines G1 to Gn. The gate drivers outputs, in response to a clock signal, the scan pulses on the gate lines G1, G2, . . . Gn (also called scan lines) successively to control turning-on and turning-off of the TFTs on respective gate lines, and the source drivers converts the display data into gray-scale voltages when the TFTs are turned on, so as to charge the pixel units to enable display of data.

The TFT-LCD currently develops towards large size and high resolution. Since the large size of the panel would lead to large RC of the gate lines and the common electrode lines, if there is a large difference between display data (i.e. gray-scale voltages) in two adjacent rows, it would cause the loading capacity of the source driver to be insufficient. Moreover, the VCOM voltage would be affected due to a sudden change in the gray-scale voltages such that the voltage applied on the pixel units is instable. These always result in unfavorable display effects such as artifact and crosstalk.

The present invention seeks to avoid insufficient loading capacity of the source driver and/or unfavorable display effects such as artifact and crosstalk resulting from too large difference between display data of two adjacent rows.

a data register for registering multiple display data, the multiple display data corresponding to a plurality of pixel units in a row of pixel units of the TFT-LCD; a data latch having a first terminal for receiving a first loading pulse and a second terminal for receiving a second loading pulse, the data latch latching the multiple display data in the data register in response to a first edge of the first loading pulse from a first level to a second level and a first edge of the second loading pulse from a first level to a second level; a digital-to-analog converter for converting the multiple display data latched in the data latch into corresponding multiple gray-scale voltages; and an output buffer comprising a plurality of buffer units, for outputting the multiple gray-scale voltages via output ends of the plurality of buffer units; wherein the first loading pulse is provided to the output buffer to enable the output buffer to start to output gray-scale voltages of odd output ends to corresponding TFT sources in response to a second edge of the first loading pulse from the second level to the first level, which second edge immediately follows the first edge, and wherein the second loading pulse is provided to the output buffer to enable the output buffer to start to output gray-scale voltages of even output ends to corresponding TFT sources in response to a second edge of the second loading pulse from the second level to the first level, which second edge immediately follows the first edge; at least the second edge of the first loading pulse is not synchronous with the second edge of the second loading pulse.

In accordance with a second aspect of the present invention, it is provided that a driving circuit for use in a TFT-LCD, comprising: at least one source driver according to the first aspect of the present invention; and a timing controller for providing a first loading pulse and a second loading pulse to the at least one source driver.

In accordance with a third aspect of the present invention, it is provided that a driving method for use in a TFT-LCD, comprising: providing a first loading pulse and a second loading pulse; latching multiple display data according to a first edge of the first loading pulse from a first level to a second level and a first edge of the second loading pulse from a first level to a second level; converting the latched multiple display data into corresponding multiple gray-scale voltages; and outputting the multiple gray-scale voltages via output ends of a plurality of buffer units of an output buffer; wherein outputting the multiple gray-scale voltages comprises: providing the first loading pulse to the output buffer to enable the output buffer to start to output the gray-scale voltages of odd output ends to corresponding TFT sources according to a second edge of the first loading pulse from a second level to a first level, which second edge immediately follows the first edge, and providing the second loading pulse to the output buffer to enable the output buffer to start to output the gray-scale voltages of even output ends to corresponding TFT sources according to a second edge of the second loading pulse from the second level to the first level, which second edge immediately follows the first edge; at least the second edge of the first loading pulse is not synchronous with the second edge of the second loading pulse.

The present invention allows the odd column pixels and the even column pixels not being charged simultaneously by providing two sets of asynchronous loading pulses (TP signals), which can relieve overloading of the source driver (and therefore insufficient charging of pixel electrodes) resulting from too large difference between display data of two adjacent rows and alleviate the pull effect on the VCOM voltage due to a sudden change in pixel voltages. More generally, the present invention can reduce picture quality losses such as artifact and crosstalk of the large-size liquid crystal display.

FIG. 3 schematically illustrates a timing relationship between a first loading pulse, a second loading pulse and a gate scan pulse for use in the source driver in accordance with an embodiment of the present invention;

FIG. 4 schematically illustrates a block diagram of a source driver for use in a TFT-LCD in accordance with another embodiment of the present invention; and

FIG. 2 schematically illustrates a block diagram of a source driver 200 for use in a TFT-LCD in accordance with an embodiment of the present invention. For the purpose of explanation, only elements relevant to the embodiment of the present invention are shown, while elements irrelevant to the embodiment of the present invention, such as shift register, level shifter, gray-scale voltage generation circuit, etc. are omitted. Like this, the source driver 200 may comprise a data register 210, a data latch 220, a digital-to-analog converter 230 and an output buffer 240. In addition, as known in the art, a timing controller is a part of the driving circuit of the TFT-LCD, which may provide the source driver 200 with signals including a video/image signal (display data) and a clock signal.

As shown in FIG. 2, the source driver 200 actually comprises a plurality of output channels (corresponding to a plurality of columns) from the data register 210 to the output buffer 240, each of which is connected to the source of the TFT in a different column of pixel units. When the current row is scanned, the scan pulse from a gate driver controls the TFTs in all the pixel units of this row to become turned on. At that time, the output signal from each output channel charges the pixel electrodes in the pixel units in the current row, realizing driving of the liquid crystal panel.

The data register 210 may comprise a plurality of register units for registering multiple display data. The number of the plurality of register units corresponds to the number of the output channels of the source driver 200. In an example, suppose that the source driver 200 has 384 output channels, the data register 210 may have 384 register units. Depending on the bit width of the display data, each register unit may be implemented by, for example, a plurality of transparent latches.

The data latch 220 may comprise a plurality of latch units. The plurality of latch units may generally latch multiple display data in the data register 210 in response to the rising edge of a loading pulse (TP signal). In accordance with the above supposed example, the data latch 200 may comprise 384 latch units. In the present embodiment, the loading pulse may comprise a first loading pulse and a second loading pulse (discussed below), and the data latch 220 may have a first terminal (not shown) for receiving the first loading pulse and a second terminal (not shown) for receiving the second loading pulse. The data latch 220 may latch the multiple display data in the data register in response to a first edge of the first loading pulse from a first level to a second level and a first edge of the second loading pulse from a first level to a second level. Specifically, the data latch 220 may latch the display data of the data register 210 corresponding to odd output channels in response to a first edge of the first loading pulse from a first level to a second level, and latch the display data of the data register 210 corresponding to even output channels in response to a first edge of the second loading pulse from a first level to a second level.

The digital-to-analog converter 230 may comprise a plurality of digital-to-analog converter (DAC) units. The digital-to-analog converter (DAC) units may convert the multiple display data latched in the data latch 220 into corresponding multiple gray-scale voltages. In accordance with the above supposed example, the digital-to-analog converter 230 may comprise 384 digital-to-analog converter (DAC) units. It should be understood that the digital-to-analog converter 230 may usually perform digital-to-analog conversion by selecting analog voltages generated by a gray-scale voltage generation circuit (not shown) to which the digital data correspond.

The output buffer 240 may comprise a plurality of buffer units. The plurality of buffer units may output the multiple gray-scale voltages selected by the digital-to-analog converter 230 via a plurality of output ends. In accordance with the above supposed example, the output buffer 240 may comprise 384 buffer units. The respective gray-scale voltages outputted from these buffer units are provided to the pixel electrodes (via the TFTs in the pixel units) to control the deflection of liquid crystal molecules, thereby enabling display of data. In the example of FIG. 2, these buffer units are illustrated as voltage followers formed by operational amplifiers OPA, though it may not be the case.

FIG. 3 schematically illustrates a timing relationship between a first loading pulse TPO, a second loading pulse TPE and a gate scan pulse for use in the source driver 200 in accordance with an embodiment of the present invention. The first loading pulse TPO is a loading pulse corresponding to the odd output channels, and the second loading pulse TPE is a loading pulse corresponding to the even output channels.

The embodiments of the present invention are further described below with reference to FIGS. 2 and 3. In FIG. 3, the second loading pulse TPE is illustrated as a delayed version of the first loading pulse TPO (that is, the second loading pulse TPE is obtained by delaying the first loading pulse TPO). In this case, the source driver 200 may comprise a delay circuit (not shown) for delaying the original loading pulse TP (from the timing controller) by a predetermined amount of time. In this way, the original loading pulse TP may act as the first loading pulse TPO, and a delayed version of the original loading pulse TP may act as the second loading pulse TPE. The first loading pulse TPO is provided to the buffer units in the odd output channels of the output buffer 240 such that those buffer units may start to output the gray-scale voltages of odd output ends to corresponding TFT sources in response to a second edge (e.g. falling edge) of the first loading pulse TPO from the second level to the first level. The second loading pulse TPE is provided to the buffer units in the even output channels of the output buffer 240 such that those buffer units may start to output the gray-scale voltages of even output ends to corresponding TFT sources in response to a second edge (e.g. falling edge) of the second loading pulse TPE. As shown in FIG. 3, the second edge of the first loading pulse TPO is not synchronous with the second edge of the second loading pulse TPE. A time interval Δt between the two edges may be set depending on the driving ability of the source driver, and is generally set so as to satisfy an expected TFT charging rate. For instance, for the resolution of 3840×2160, the time interval Δt may be between 0.5 μs and 0.8 μs.

Since the first loading pulse TPO and the second loading pulse TPE are not synchronous, the pixel units in odd columns and the pixel units in even columns are not charged simultaneously, which alleviates adverse consequences resulting from (possible) too large difference between display data of two adjacent rows.

What is discussed above is the situation in which the first loading pulse TPO and the second loading pulse TPE which are not synchronous are always provided, regardless of the actual difference between display data of two adjacent rows. However, in accordance with another embodiment of the present invention, a certain determination mechanism may be introduced such that two loading pulses not synchronous are provided only when the difference between display data of two adjacent rows is determined to be too large; otherwise, the same (original) loading pulse is provided to the pixel units in odd columns and the pixel units in even columns.

FIG. 4 schematically illustrates a block diagram of a source driver 400 for use in a TFT-LCD in accordance with another embodiment of the present invention. In this figure, a data register 410, a data latch 420, a digital-to-analog converter 430 and an output buffer 440 respectively correspond to the data register 210, the data latch 220, the digital-to-analog converter 230 and the output buffer 240 in FIG. 2, and they all will not be described in detail for simplicity.

The source driver 400 may comprise a data difference determination circuit 450, which can determine, upon updating a row of display data, whether the difference between multiple display data in the (n+1)-th row as registered in the data register 410 and multiple display data in the n-th row as latched in the data latch 420 is large or not. For example, in accordance with the above supposed example, each of the data register 410 and the data latch 420 stores 384 display data (corresponding to 384 columns), all of which is inputted to the data difference determination circuit 450 where the difference between two display data on each column is calculated and then compared with a first predetermined threshold so as to obtain a determination result about the difference between display data of two adjacent rows. According to different determination results, the data difference determination circuit 450 provides different inputs to the timing controller (as shown in FIG. 4). The input may be a high level or low level representing a different logical value. For example, the high level may represent large difference between the display data of the (n+1)-th row and the display data of the n-th row. Thereafter, according to the input from the data difference determination circuit 450, the timing controller may provide or may not provide the first loading pulse TPO and the second loading pulse TPE. As stated above, the first loading pulse TPO and the second loading pulse TPE which are not synchronous are provided only when the input indicates that the difference between the display data of the (n+1)-th row and the display data of the n-th row is large; otherwise, a same loading pulse is provided. It should be further understood that said “large difference” may indicate that at least one or more of respective differences between the multiple display data in the (n+1)-th row and the multiple display data in the n-th row is larger than the first predetermined threshold.

FIG. 5 schematically illustrates a block diagram of an implementation of the data difference determination circuit 450 shown in FIG. 4. In the implementation, the data difference determination circuit 450 may comprise a subtracter 451 that may perform subtraction between the multiple display data in the (n+1)-th row and the multiple display data in the n-th row, respectively and a first numeric comparator 452 that may compare each of the subtraction results with the first predetermined threshold TH1, respectively. In accordance with the above supposed example, the 384 display data D1(n+1), D2(n+1), . . . D384(n+1) in the (n+1)-th row and the 384 display data D1(n), D2(n), . . . D384(n) in the n-th row are inputted into the subtracter 451 for subtraction, and 384 corresponding differences S1, S2, . . . , S384 are outputted. The 384 differences are then inputted into the first numeric comparator 452 to be compared with the first predetermined threshold TH1. The first numeric comparator 452 can output 384 comparison results C1, C2, . . . , C384 representing different logical relationships (that is, larger, equal or smaller). The implementations of the subtracter and the first numeric comparator are known in the art, which will not be described here in detail.

In the case that said “large difference” indicates that at least one of the differences between the multiple display data in the (n+1)-th row and the multiple display data in the n-th row is larger than the first predetermined threshold, depending on the signal logic as defined (for example, logic “0” may indicate that the difference is larger than the first threshold, or logic “1” may indicate that the difference is larger than the first threshold), the data difference determination circuit 450 may further comprise a first AND gate or first OR gate 453 for performing an AND operation or OR operation for each of the output results of the first numeric comparator 452. The output of the first AND gate or first OR gate 453 may be provided to the timing controller as an input indicating the determination result of the data difference determination circuit 450.

Alternatively, in the case that said “large difference” indicates that at least a predetermined number of the differences between the multiple display data in the (n+1)-th row and the display data in the n-th row is larger than the first predetermined threshold, in another implementation, the data difference determination circuit 450 may comprise an adder for adding every one of the output results of the first numeric comparator and a second numeric comparator for comparing the addition result with a second predetermined threshold. The output of the second numeric comparator is provided to the timing controller as an input indicating the determination result of the data difference determination circuit 450. For example, if logic “0” indicates that the difference is larger than the first threshold, the addition result being smaller than the second predetermined threshold indicates large difference between the multiple display data in the (n+1)-th row and the multiple display data in the n-th row. Alternatively, if logic “1” indicates that the difference is larger than the first threshold, the addition result being larger than the second predetermined threshold indicates large difference between the multiple display data in the (n+1)-th row and the multiple display data in the n-th row. The implementations of the adder and the second numeric comparator are known in the art and will not be described here in detail.

In practice, the source driver usually takes the form of a source driving chip, and the source driving chip, the gate driving chip, the timing controller and other peripheral circuits together constitute a driving circuit for use in the display panel. In the preceding embodiments, the delay circuit is described as a part of the source driver 200, though it may not be the case. For example, the delay circuit may also be a separate circuit as a part of the driving circuit. Furthermore, in the preceding embodiments, the data difference determination circuit 450 is described as a part of the source driver 400, though it may not be the case. For example, the data difference determination circuit 450 may also be a separate circuit as a part of the driving circuit.

Further, there may be a demand for a plurality of cascaded source driving chips when driving a display panel. For example, as for a SXGA display panel with the resolution of 1280×1024, a row of display data corresponds to 1280×3=3840 pixel units (because one pixel comprises three pixel units of R, G, B), at that time, in accordance with the above supposed example (i.e. a source driving chip having 384 outputs), 10 cascaded source driving chips are required to drive the SXGA display panel. In the case of a plurality of source driving chips, depending on the signal logic as defined (for example, logic “0” may indicate large difference between the multiple display data in the (n+1)-th row and the multiple display data in the n-th row; or logic “1” may indicate the large difference), the driving circuit may further comprise a second AND gate or second OR gate for performing an AND operation or OR operation for the outputs from the data difference determination circuit of each of the plurality of source driving chips. The output of the second AND gate or second OR gate may be provided to the timing controller as a final determination result indicating the difference between display data of two adjacent rows.

Corresponding to the above embodiments described with reference to FIGS. 2 to 5, another embodiment of the present invention further provides a driving method for use in a TFT-LCD, comprising: providing a first loading pulse TPO and a second loading pulse TPE; latching multiple display data according to a first edge of the first loading pulse TPO from a first level to a second level and a first edge of the second loading pulse TPE from a first level to a second level; converting the latched multiple display data into corresponding multiple gray-scale voltages; and outputting the multiple gray-scale voltages via output ends of a plurality of buffer units of an output buffer 240, 440; wherein outputting the multiple gray-scale voltages comprises: providing the first loading pulse TPO to the output buffer 240, 440 such that the output buffer 240, 440 starts to output the gray-scale voltages of odd output ends to corresponding TFT sources according to a second edge of the first loading pulse TPO from the second level to the first level, which second edge immediately follows the first edge, and providing the second loading pulse TPE to the output buffer 240, 440 such that the output buffer 240, 440 starts to output the gray-scale voltages of even output ends to corresponding TFT sources according to a second edge of the second loading pulse TPE from the second level to the first level, which second edge immediately follows the first edge. At least the second edge of the first loading pulse TPO is not synchronous with the second edge of the second loading pulse TPE.

It should be understood that other features and advantages of the driving method have been embodied in the preceding description of the source driver 200, 400 and the driving circuit, and hence are not described here in detail.

Although the preceding discussion includes several specific implementation details, these should not be construed as limitation to any invention or scope possibly claimed, but should be construed as description of the features only limited to specific embodiments of specific inventions. The specific features described in different embodiments of the present specification may also be implemented in the form of combinations in a single embodiment. On the contrary, different features described in a single embodiment may also be implemented separately in multiple embodiments or in any suitable form of sub-combination. In addition, although the features are described previously as functioning in specific combinations, even initially claimed in this way, one or more features from the claimed combination may also be excluded from the combination in some cases, and the claimed combination may be directed to sub-combinations or variants of sub-combinations.

In view of the preceding description in conjunction with reading the drawings, various amendments and modifications to the preceding illustrative embodiments of the present invention may become obvious for the skilled persons of relevant arts. Any and all amendments will still fall within the scopes of the non-limiting and illustrative embodiments of the present invention. In addition, the skilled persons in the field to which these embodiment of the invention belong, upon benefiting from the teachings given by the preceding description and relevant drawings, would conceive of other embodiments of the present invention described herein.

Therefore, it should be understood that the embodiments of the present invention are not limited to the specific ones as disclosed, and amendments and other embodiments are also intended to be included within the scope of the appended Claims. Although specific terms are used herein, they are only used in general and descriptive sense, not for the purpose of limitation.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey