mipi dsi lcd panel datasheet price

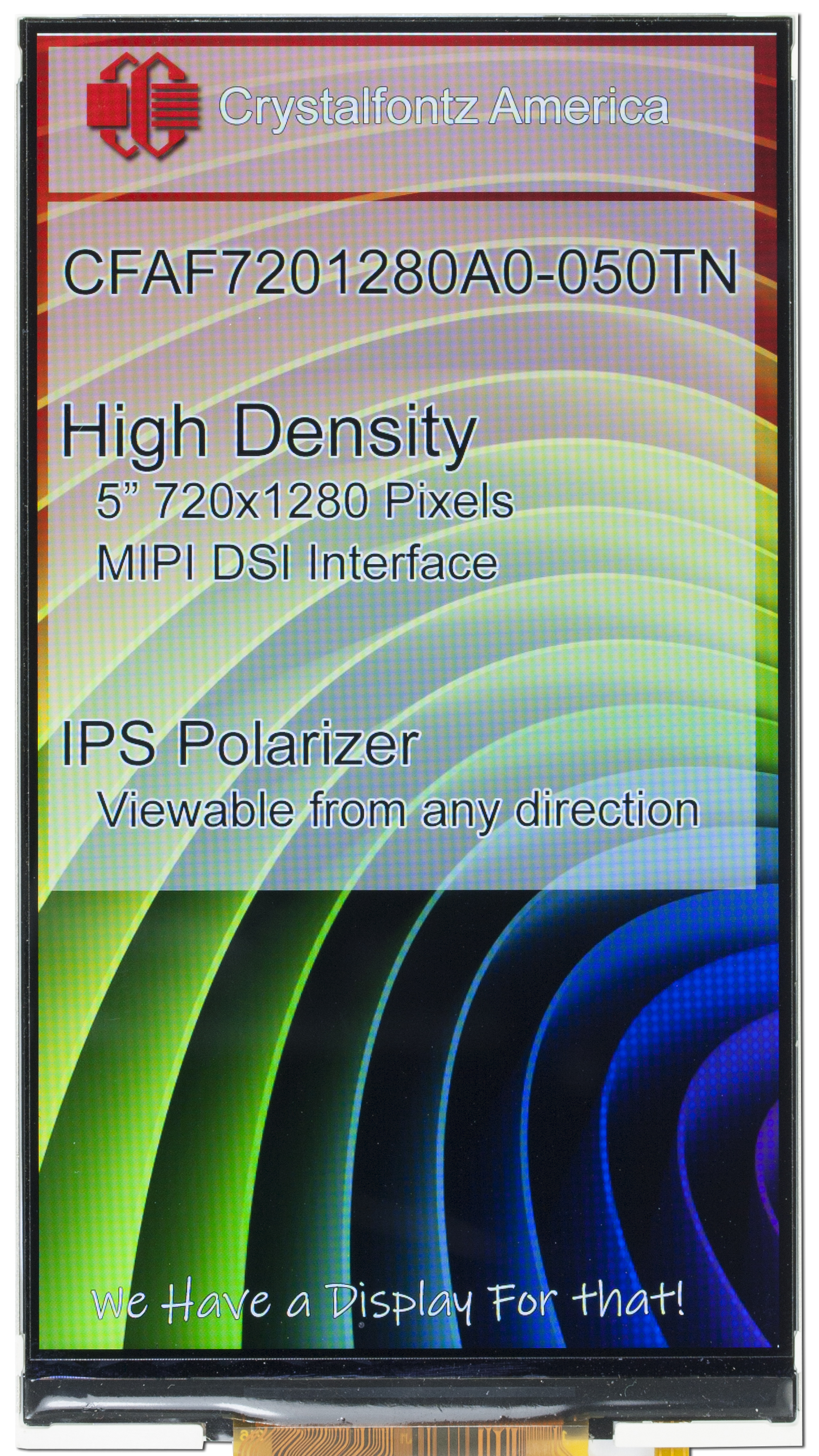

37.72x49.86mmResolution=480x640"Display Type=IPS"Brightness=700-999 Nits (Sun-readable)"Touch Panel=None"CTP Controller=None"Operating Temperature=-30C to 80C"Specifications=/content/E104RB-FW450-N_Spec.pdf"Interface=2-Lane MIPI DSI

First, you need to check whether this display has On-cell or In-cell touch panel, if has, it only needs to add a cover glass on it. If not, it needs an external touch panel.

Because the shape of the cover glass depends on the design of the clients, to avoid infringement of appearance, most of the developers need different customized touch panels.

MIPI Mobile Industry Processor Interface is a relatively new standard, mainly used in mobile device applications. The application can be divided into DSI (display bus interface) serial display interface, CSI (camera serial interface), DPI (display pixel interface). DSI defines a high-speed serial interface between the main processor and the display module. The MIPI TFT LCD module introduced by Raystar has a high-speed advantage compared to the RGB interface. Our MIPI DSI standard TFT LCD display module contains different features, including high brightness, wide temperature, and wide viewing angle, etc. You are able to quickly select your suitable products by using the filters below.

Abstract: toshiba 8GB Nand flash emmc toshiba emmc toshiba 16GB Nand flash emmc TCM9000MD TCM9200MD TOSHIBA eMMC CATALOG TC35893XBG RGB to MIPI DSI LCD toshiba 8GB Nand flash bga

Text: High-Speed Serial ( MIPI DSI ) LCD Controller RAM VGA/FWVGA LCD Controller Parallel (18/24 , . Additionally, the T5GE incorporates an LCD controller that supports LCD display at resolutions up to FWVGA , :4:4, YUV 4:2:2 and YUV 4:2:0 input formats LCD controller FWVGA resolution; support for two LCD , controller that supports LCD display of WVGA size (480 x 800) and can display WVGA and TV through the video , LCD Controller RAM VGA Parallel (18/24-bit RGB) I/O Expander Example 2 BB I C (2

Text: Reset MUX DBI to VEE DBI MUX Reg Bus Control 4-Lane MIPI DSI Client DBI DBI Slave VEE to DBI I2C Slave DPI DPHY DPI DPI 4-Lane MIPI DSI Client DEMUX Figure , DPI 2-Lane MIPI DSI Client DPHY DPI DPI 2-Lane MIPI DSI Client DEMUX Figure 2 , MUX Reg Bus Control 4-Lane MIPI DSI Client DBI DBI Slave VEE to DBI I2C Slave DPI DPHY DPI DPI 2-Lane MIPI DSI Client DEMUX Figure 3: VX3B2F Architecture DBI

Text: low emission levels. MIPI DSI supports DSI video mode and DCS command mode. Another way to lower LCD , device contains an EPD controller and two MIPI DSI ports. The first MIPI DSI port supports four DSI lanes, while the second MIPI DSI port supports three DSI lanes. Each DSI lane can transfer data at up to 1 , controller , MIPI DSI , as well as many key modules such as 2D/3D graphics, HD video codec, ISP, Security, SD , of MIPI DSI (Mobile Industry Processor Interface, Display Serial Interface), a display standard for

Text: with a MIPI Display Serial Interface ( DSI ). The bridge supports an MDDI 1.2 Type 1 with up to 800 , of MDDI. The bridge supports MIPI DSI on the panel side with up to 500 Mbps per data lane times , Features ⢠Solutions are based on the latest versions of industry standard MDDI 1.2 and MIPI DSI , compatibility to MDDI 1.1 is supported. The TC358760XBG is a 49-pin device and supports MDDI and MIPI DSI , module interface â 3 ports LCD interface (Only one port can be used at a time) ⢠MIPI DSI-TX Data

Text: features support for the next generation of peripheral interfaces, through support for MIPI DSI display , KB L1 D-Cache MHz FPU V3.0 WMMX2 EPD HDMI 2xMIPI Parallel Controller DSI 2xMIPI CSI2 , FPU v.3 MIPI DSI USB 2.0 OTG ARMADA 610 PCM 12S MIC Speaker Headset Audio In Vibrator , MTPS 3D, Integrated EPD Controller , 4x Displays, Security Enabled, POP/Discrete and Consumer Package , integrated EPD display controller and advanced 3D graphics, the ARMADA 610 delivers the best combination of

Text: , through support for MIPI DSI display, MIPI CSI camera, MIPI HSI and MIPI SLIMbus. Additional peripheral , FPU v.3 MIPI DSI USB 2.0 OTG ARMADA 618 PCM 12S MIC Speaker Headset Audio In Vibrator , high performance LPDDR memory, a highly lexible display controller capable of four simultaneous , bandwidth peripherals. Legacy peripherals such as Parallel LCD and Parallel Camera interfaces are also , 2xMIPI DSI 2xMIPI CSI2 GPU 2D/3D Graphics 45 MT/sec 200 MP/sec 1 Ports 2 Ports 1 Ports

Text: based on the latest versions of industry standard MIPI DSI 1.01 interface to ensure high speed data , applications. Features ⢠LCD module interface â MIPI DSI-TX Data 3-lane, CLK 1-lane with data rates up to 500 Mbps/lane â Support for XGA size LCD panel when MIPI DPI is selected as Host interface â , connectivity to panel with MIPI DSI protocol. â MIPI DBI Type-B 16-bit bus interface The bridge supports MIPI DSI connectivity ⢠18-bit bus RGB 666 format supported. on the panel side with up to 500 Mbps

Text: features support for the next generation of peripheral interfaces, through support for MIPI DSI display , EPD HDMI 2xMIPI Parallel Controller DSI 2xMIPI CSI2 GPU 2D/3D Graphics 45 MT/sec 200 MP/sec , (SLC/MLC) 8bit eMMC FPU v.3 MIPI DSI USB 2.0 OTG USB 2.0 Host (x3) Accessory Connector , MTPS 3D, Integrated EPD Controller , 4x Displays, Security Enabled, POP/Discrete and Consumer Package , integrated EPD display controller and advanced 3D graphics, the ARMADA 610 delivers the best combination of

Text: peripheral interfaces, through support for MIPI DSI display, MIPI CSI camera, MIPI HSI and MIPI SLIMbus , (SLC/MLC) 8bit eMMC FPU v.3 MIPI DSI USB 2.0 OTG USB 2.0 Host (x3) Accessory Connector , 618 offers support for high performance LPDDR memory, a highly flexible display controller capable of , standard set of lower bandwidth peripherals. Legacy peripherals such as Parallel LCD and Parallel Camera , 2.42 DMIPS/ 32 KB L1 D-Cache MHz FPU V3.0 WMMX2 HDMI 2xMIPI DSI 2xMIPI CSI2 GPU 2D

Text: difficult TC358763XBG supports MIPI DSI (Display Serial Interface) as a LCD interface. TC358763XBG also , : 31.4 mg (Typ.) TC358763XBG supports MIPI® DSI (Display Serial Interface) as a LCD interface , minimize the power consumption in the target system. Features â LCD module interface - MIPI DSI-TX , LCD resolution setting size: 1024 à 1024 â Host interface ï² MIPI DPI 24-bit bus interface ï , : GPIO0 to GPIO6 6 / 17 2014-05-29 TC358763XBG 2. Features â LCD module interface MIPI

Abstract: RGB to MIPI DSI LCD ANX1413 RGB MIPI 4 lanes HDMI TO MIPI MIPI DSI TFT HDMI input MIPI DSI output displayport TO MIPI mipi dsi controller MIPI hdmi

Text: Product Brief ANX1413 Low Power MIPI Timing controller The ANX1812 is an ultra low power timing-controller (TCON) for TFT LCD designed for portable devices such as Tablets and Smartbooks. As a member of , the industry"s lowest power consumption. Standard Compliance MIPI DSI V1.02, MIPI D-PHY 1.0 MIPI , SSCG GPIO Controller 12 GPIOs Figure 1: ANX1413 Block Diagram Revision 0.01 Analogix , controller 2 lanes DisplayPortTM Timing controller 4 lanes DisplayPortTM Timing controller Copyright ©2012

Text: ² MIPI DSI version 1.01, Feb 2008 ï² MIPI D-PHY version 0.9, Oct 2007 ï² MIPI DPI version 2.0, Sep, 2005 ï² MIPI DBI-2 version 2.00, Nov 2005 ï² MIPI DCS Command version 1.02, Dec 2008 â DSI , . 19 MIPI DSI LP transmitter DC characteristics . 20 MIPI DSI HS receiver DC characteristics . 20 MIPI DSI LP receiver DC characteristics

Text: Product Brief TC358764/5 Display Bridge ( MIPI DSI to LVDS) ® Highlights ⢠Display , versions of the industry-standard MIPI DSI 1.01 interface to ensure high-speed data rates of up to 800 , bridge is optimized for mobile devices using a Host processor with MIPI DSI (Display Serial Interface , 4-lane MIPI DSI with data rates up to 800 Mbps per lane, for maximum total bandwidth of 3.2 Gbps , implemented â MIPI DSI version 1.01, Feb 2008 â MIPI D-PHY version 0.9, Oct 2007 â MIPI DCS version

Text: are based on the latest versions of the industry-standard MIPI DSI 1.01 interface to ensure high-speed , product platforms such as MIDs, netbooks, smartbooks and eBooks. TC358764/5 Display Bridge ( MIPI DSI to , Host processor with MIPI DSI (Display Serial Interface) connectivity. The TC358764/5 functions as a , panels. The TC358764/5 bridge can be configured to have up to a 4-lane MIPI DSI with data rates up to 800 , . System Block Diagram of TC358765XBG Features · MIPI standard implemented MIPI DSI version 1.01, Feb

Text: support with one MIPI CSI-2 port with three lanes(1Gb/s per lane, up to 2.5Gb/s total); two MIPI CSI sensors (via external hub) ⢠LCD controller supports 1 MIPI DSI port (3 lanes), up to 720p resolution , SDIO 88PM812 I2S ARMv7 Core GPU PCM MIC Speaker Headset Audio In Vibrator DSI , diverse product portfolio includes switching, transceiver, communications controller , processor, wireless

Text: Interface. ⢠Solutions are based on the latest versions of industry standard MIPI DSI 1.01 interface to ensure high speed data rates of up to 800 Mbps per lane. ⢠Legacy interfaces such as MIPI , display panel. The TC358762XBG bridge supports MIPI DSI dual lane with up to 800 Mbps per data lane , colors. Features ⢠MIPI standard implemented â â â â â MIPI DSI version 1.01, Feb , Baseband or Application Processor MIPI DSI Client REFCLK RESETN DPI/DBI Output DT [23:0

Text: , AAC, AAC+, eAAC+, WMA, and MIDI â Display ⢠Imaging sensor support with one MIPI CSI-2 port with three lanes(1Gb/s per lane, up to 2.5Gb/s total); two MIPI CSI sensors (via external hub) ⢠LCD controller supports 1 MIPI DSI port (3 lanes), up to 720p resolution APPLICATIONS This highly , price. BLOCK DIAGRAM SD/MMC Card NAND Flash eMMC LP-DDR2 GPS DSI PXA968 UART , includes switching, transceiver, communications controller , processor, wireless, power management, and

Text: generation · System integration of embedded controller with MIPI D-PHY display and camera devices · , instruments. To ensure your design operates according to the MIPI D-PHY link and CSI-2 or DSI protocol , build MIPI DSI stimulus from bitmap files with the Image Inserter application · Save hours of , support and decoding MIPI D-PHY DSI 1.01 MIPI D-PHY DSI 1.00 MIPI D-PHY CSI-2 1.00 Yes No Yes , Agilent MIPI D-PHY Protocol Test Solutions N4851A/B MIPI D-PHY Acquisition Probe N4861A/B MIPI

Text: high-performance interfaces, such as PCIe Gen2, Gigabit Ethernet, SATA 3.0, HDMI 1.4, SDXC, MIPI CSI/ DSI and 64 , support Integrated high bandwidth connectivity peripherals Industry latest HDMI1.4, SDXC, MIPI CSI/ DSI , Expansion Connector* i.MX6 1GHz/800MHz Cortex A9 Q/D/U/S Camera CSIx2 (8-bit) MIPI CSI, DSI 24-Bit RGB LCD IF Dual UART 4x4 Key, Memory Bus ESAI, SPDIF MLB, CAN2 I2C2, PWM, GPIO Memory 512MB, Hub USBHost x 4 HDMI 1.4 DISPO, MIPI DSI Camera1 (8bit) x 1 SATA x 1 USBOTG x 1 LVDSO

Text: high-performance interfaces, such as PCIe Gen2, Gigabit Ethernet, SATA 3.0, HDMI 1.4, SDXC, MIPI CSI/ DSI and 64 , support Integrated high bandwidth connectivity peripherals Industry latest HDMI1.4, SDXC, MIPI CSI/ DSI , Expansion Connector* i.MX6 1GHz/800MHz Cortex A9 Q/D/U/S Camera CSIx2 (8-bit) MIPI CSI, DSI 24-Bit RGB LCD IF Dual UART 4x4 Key, Memory Bus ESAI, SPDIF MLB, CAN2 I2C2, PWM, GPIO Memory 512MB, Hub USBHost x 4 (4 Port) LVDS x 2 HDMI x 1 HDMI 1.4 DISPO, MIPI DSI Audio x 1

Text: generation ⢠System integration of embedded controller with MIPI D-PHY display and camera devices â , to the MIPI D-PHY link and CSI-2 or DSI protocol specification, you need real-time insight on the , build MIPI DSI stimulus from bitmap files with the Image Inserter application ⢠Save hours of , frame support DSI Image Extractor 5 www.agilent.com/ï¬nd/ MIPI Agilent N4851A/B Analysis , specification ) Protocol version support and decoding MIPI D-PHY DSI 1.01 MIPI D-PHY DSI 1.00 MIPI D-PHY

Text: CSI-4 port for 2 MIPI CSI sensors, up to 4 data lanes (1Gb/s per lane, up to 2.5Gb/s total) ⢠LCD controller supports 1 MIPI DSI port (4 lanes) with up to 720p resolution ⢠Integrated ISP can support up , PXA988 UART 88W8787 Wi-Fi/BT/FM DSI ARM Cortex A9 ARM Cortex A9 GPU Video Engine , . Marvellâs diverse product portfolio includes switching, transceiver, communications controller

Text: a Host (application or baseband processor) over MIPI DSI or DPI link to drive DisplayPort display , .) translate MIPI DSI or DPI transfers to DisplayPort transfers. As the DisplayPort uses fewer wires compared , Translates MIPI DSI /DPI Link video stream from Host to DisplayPort Link data to external display devices , Receiver ï² MIPI DSI : v1.01 / MIPI D-PHY: v0.90 Compliant. ï² Up to four (4) Data Lanes with , is from MIPI DSI Host. ï² MODE P21: TC358767AXBG uses DisplayPort Tx as single 2-lane DisplayPort

Text: support with one CSI-4 port for 2 MIPI CSI sensors, up to 4 data lanes (1Gb/s per lane, up to 2.5Gb/s total) ⢠LCD controller supports 1 MIPI DSI port (4 lanes) with up to 720p resolution â , 88W8787 Wi-Fi/BT/FM PXA988 UART DSI ARM Cortex A9 ARM Cortex A9 GPU Video Engine , , communications controller , processor, wireless, power management, and storage solutions that power the entire

Text: . MIPI CSI Motor Control SVGA / WVGA Dual Display LCD Interface MIPI DSI HD 720p 30fps, Controller Security Host Interface / MIPI Stacked 256Mb / 512Mb Mobile-DDR Baseband Memory Bus / MIPI CSI Audio/Voice Zero-Power LCD & Audio Bypass Limited to MPU LCDs & Parallel HIF

MIPI Alliance offers a comprehensive portfolio of specifications to interface chipsets and peripherals in mobile-connected devices. The specifications can be applied to interconnect a full range of components—from the modem, antenna and application processor to the camera, display, sensors and other peripherals. Manufacturers use the specifications to optimize performance, simplify the design process, reduce development costs, create economies of scale for their designs, and shorten time-to-market for their products.

MIPI Alliance specifications serve six types of interface needs in a device: physical layer, multimedia, chip-to-chip/interprocessor communications (IPC), device control and data management, system debugging, and software integration.

MIPI Alliance offers its specifications as individual interfaces, enabling companies to use those that suit their own particular needs. Vendors can apply the interfaces with their own high-level features to provide added value or differentiate their products.

MIPI Display Command Set (MIPI DCSSM) v1.5 provides a standardized command set for control functions and supply of data to displays usingMIPI Display Serial Interface 2(DSI-2SM). It defines commands for all setup, control and test functions, including the control of settings such as resolution, width and brightness. DCS v1.5 supports the Video Electronics Standards Association (VESA®) Display Stream Compression (DSC) and VESA Display Compression-M (VDC-M) standards. Optional features support MIPI Display Service Extensions (DSE) v1.0 for automotive functional safety and High-Bandwidth Digital Content Protection (HDCP).

This 5" DSI screen for Raspberry Pi comes from customer returning order.The quality and functionality is exactly same as original OSOYOO 5" DSI screen.You will save 30% from original price.The detail of the original product is as following:

The SN65DSI85 DSI to FlatLink bridge features a dual-channel MIPI D-PHY receiver front-end configuration with 4 lanes per channel operating at 1 Gbps per lane; a maximum input bandwidth of 8 Gbps. The bridge decodes MIPI DSI 18-bpp RGB666 and 24-bpp RGB888 packets and converts the formatted video data stream to a FlatLink compatible LVDS output operating at pixel clocks operating from 25 MHz to 154 MHz, offering a Dual-Link LVDS, Single-Link LVDS, or two Single-Link LVDS interface(s) with four data lanes per link.

The SN65DSI85 is well suited for WQXGA (2560 × 1600) at 60 frames per second, as well as 3D Graphics at WUXGA and True HD (1920 × 1080) resolutions at an equivalent 120 fps with up to 24 bits-per-pixel. Partial line buffering is implemented to accommodate the data stream mismatch between the DSI and LVDS interfaces.

Designed with industry-compliant interface technology, the SN65DSI85 is compatible with a wide range of micro-processors, and is designed with a range of power management features including low-swing LVDS outputs, and the MIPI® defined ultra-low power state (ULPS) support.

The SN65DSI85 is implemented in a small outline 5-mm × 5-mm nFBGA at 0.5-mm pitch package, and operates across a temperature range from –40°C to 85°C.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey