lcd panel bpp manufacturer

BPP-420 understands traditional control codes, such as Tab LF/CR FF/Clear Backspace etc. Additional features are mapped to other control codes or Escape sequences. A quick summary:

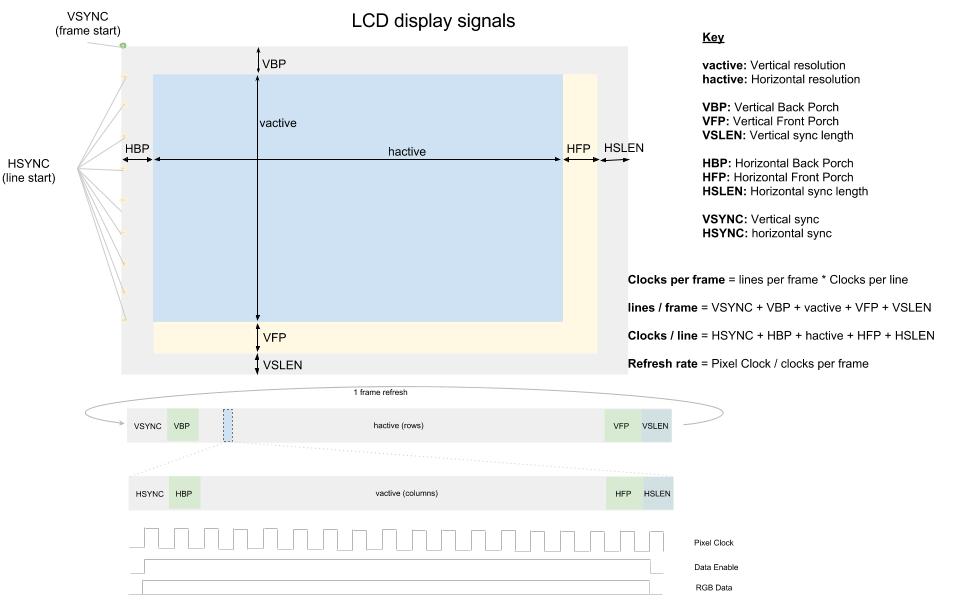

This application note describes the i.MX6 CPU graphical system and the steps to define a new custom TFT (Thin Film Transistor) display panel in Digi Embedded Yocto and discusses the most standard panels available. Some panels may need special consideration.

An LCD panel is a matrix of pixels that are divided into rows and columns. These pixels are individually painted according to different signals and timing parameters, and you can control each pixel"s color individually. The panel is continuously refreshed, typically at around 60 Hz, from the contents of the frame buffer memory. Each memory location on the frame buffer corresponds to a pixel on the LCD panel.

A 1024 x 600 resolution display requires 614400 memory locations, with each location having a number of possible colors. The number of bits needed to describe the available colors is called bits per pixel (bpp). For example, 16 bpp can describe 65536 colors and 24 bits can describe 16777216 colors (known as true color). A panel with 614400 24-bit locations requires a 1800 KB frame buffer.

Every manufacturer provides display timings in a slightly different way and some provide more detail than others. Most LCD panels work with a range of timing parameters.

LCD displays must be created as nodes in the device tree with a display-timings subnode. Display timings binding documentation at Documentation/devicetree/bindings/video/display-timing.txt explains the required timing properties to describe an LCD.lcdname {

hfront-porch is the horizontal front porch, the number of clock pulses (pixels) between the last valid pixel data in the line and the next HSYNC pulse. According to the LCD data format, this value is zero.

vfront-porch is the vertical front porch, the number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse. According to the LCD data format, this value is zero.

NoteThe recommended timings from the LCD datasheet often do not work perfectly, as each platform introduces noise and delays that affect the display"s signals and timings.

This color chart displays a white one-pixel frame at the edges of the LCD (which allows you to verify correct position and width/height), and gradients of red, green, blue, and white (which allow you to verify correct color depth and format).

A common size for LCDs manufactured for small consumer electronics, basic mobile phones and feature phones, typically in a 1.7" to 1.9" diagonal size. This LCD is often used in portrait (128×160) orientation. The unusual 5:4 aspect ratio makes the display slightly different from QQVGA dimensions.

A shared size for older portable video game systems. The nearly-square (but landscape) aspect ratio and coarse pixel resolution gave these games a characteristic visual style. Colour depth ranged from 4 colours (2 bpp) with the original Game Boy, through 16–32 colours (4–5 bpp) with the Atari Lynx and Game Gear, to a maximum of 56 colours (equivalent of 6 bpp) from a wider palette with the Game Boy Color. Also appears as a YouTube resolution option ("144p").

Used with some smaller, cheaper portable devices, including lower-end cellphones and PDAs, and perhaps most commonly in the Nintendo Game Boy Advance (with, in that guise, 32k colours (15 bpp) on-screen).

Half the resolution in each dimension as standard VGA. First appeared as a VESA mode (134h=256 color, 135h=Hi-Color) that primarily allowed 80x30 character text with graphics, and should not be confused with CGA (320x200); QVGA is normally used when describing screens on portable devices (PDAs, pocket media players, feature phones, smartphones, etc.). No set colour depth or refresh rate is associated with this standard or those that follow, as it is dependent both on the manufacturing quality of the screen and the capabilities of the attached display driver hardware, and almost always incorporates an LCD panel with no visible line-scanning. However, it would typically be in the 8-to-12 bpp (256–4096 colours) through 18 bpp (262,144 colours) range.

Up to 6 bpp for Amiga (8 bpp with later models), typically 2–4 bpp for most hi-res applications (saving memory and processing time), 4–5 bpp for games and "fake" 12/18 bpp for static images (HAM mode). Up to 15 bpp for Archimedes and Falcon (12 bpp for TT), but typically 4 bpp in use.

Later, larger monitors (15" and 16") allowed use of an SVGA-like binary-half-megapixel 832×624 resolution (at 75 Hz) that was eventually used as the default setting for the original, late-1990s iMac. Even larger 17" and 19" monitors could attain higher resolutions still, when connected to a suitably capable computer, but apart from the 1152×870 "XGA+" mode discussed further below, Mac resolutions beyond 832×624 tended to fall into line with PC standards, using what were essentially rebadged PC monitors with a different cable connection. Mac models after the II (Power Mac, Quadra, etc.) also allowed at first 16-bit High Colour (65,536, or "Thousands of" colours), and then 24-bit True Colour (16.7M, or "Millions of" colours), but much like PC standards beyond XGA, the increase in colour depth past 8 bpp was not strictly tied to changing resolution standards.

The first PowerBook, released in 1991, replaced the original Mac Portable (basically an original Mac with an LCD, keyboard and trackball in a lunchbox-style shell), and introduced a new 640×400 greyscale screen. This was joined in 1993 with the PowerBook 165c, which kept the same resolution but added colour capability similar to that of Mac II (256 colours from a palette of 16.7 million).

Introduced in 1984 by IBM. A resolution of 640×350 pixels of 16 different colours in 4 bits per pixel (bpp), selectable from a 64-colour palette in 2 bits per each of red-green-blue (RGB) unit.DIP switch options; plus full EGA resolution (and CGA hi-res) in monochrome, if installed memory was insufficient for full colour at above 320×200.

Introduced on MCA-based PS/2 models in 1987, it replaced the digital TTL signaling of EGA and earlier standards with analog RGBHV signaling, using the synonymous VGA connector. As with EGA, the VGA standard actually encompasses a set of different resolutions; 640×480 is sometimes referred to as "VGA resolution" today, however as per the original standard this mode actually only supports 16 colours (4 bpp) at 60 Hz. Other common display modes also defined as VGA include 320×200 at 256 colours (8 bpp) (standard VGA resolution for DOS games that stems from halving the pixel rate of 640×400, but doubling color depth) and a text mode with 720×400 pixels; these modes run at 70 Hz and use non-square pixels, so 4:3 aspect correction is required for correct display.

Furthermore, VGA displays and adapters are generally capable of Mode X graphics, an undocumented mode to allow increased non-standard resolutions, most commonly 320×240 (with 8 bpp and square pixels) at 60 Hz.

The high-resolution mode introduced by 8514/A became a de facto general standard in a succession of computing and digital-media fields for more than two decades, arguably more so than SVGA, with successive IBM and clone videocards and CRT monitors (a multisync monitor"s grade being broadly determinable by whether it could display 1024×768 at all, or show it interlaced, non-interlaced, or "flicker-free"), LCD panels (the standard resolution for 14" and 15" 4:3 desktop monitors, and a whole generation of 11–15" laptops), early plasma and HD ready LCD televisions (albeit at a stretched 16:9 aspect ratio, showing down-scaled material), professional video projectors, and most recently, tablet computers.

Over the course of the early-to-mid-1990s, "SVGA" became a quasi-standard term in PC games, typically referring to a 640×480 resolution using 256 colours (8 bpp) at 60 Hz refresh rate. Many other higher and lower modes were standardized in the VESA BIOS Extensions, leading to the establishment of "SVGA" and "VESA" as catch-all terms encompassing output modes that surpassed the original VGA specifications.

An IBM display standard introduced in 1990. XGA built on 8514/A"s existing 1024×768 mode and added support for "high colour" (65,536 colours, 16 bpp) at 640×480. The second revision ("XGA-2") was a more thorough upgrade, offering higher refresh rates (75 Hz and up, non-interlaced, up to at least 1024×768), improved performance, and a fully programmable display engine capable of almost any resolution within its physical limits. For example, 1280×1024 (5:4) or 1360×1024 (4:3) in 16 colours at 60 Hz, 1056×400 [14h] Text Mode (132×50 characters); 800×600 in 256 or 64k colours; and even as high as 1600×1200 (at a reduced 50 Hz scan rate) with a high-quality multisync monitor (or an otherwise non-standard 960×720 at 60 Hz on a lower-end one capable of high refresh rates at 800×600, but only interlaced mode at 1024×768).I, 640×480×16 NI, high-res text) were commonly used outside Windows and other hardware-abstracting graphical environments.

A widely used aspect ratio of 5:4 (1.25:1) instead of the more common 4:3 (1.33:1), meaning that even 4:3 pictures and video will appear letterboxed on the narrower 5:4 screens. This is generally the native resolution—with, therefore, square pixels—of standard 17" and 19" LCD monitors. It was often a recommended resolution for 17" and 19" CRTs also, though as they were usually produced in a 4:3 aspect ratio, it either gave non-square pixels or required adjustment to show small vertical borders at each side of the image. Allows 24-bit colour in 4 MB of graphics memory, or 4-bit colour in 640 kB.

An enhanced version of the WXGA format. This display aspect ratio was common in widescreen notebook computers, and many 19" widescreen LCD monitors until ca. 2010.

A wide version of the SXGA+ format, the native resolution for many 22" widescreen LCD monitors, also used in larger, wide-screen notebook computers until ca. 2010.

This display aspect ratio is the native resolution for many 24" widescreen LCD monitors, and is expected to also become a standard resolution for smaller-to-medium-sized wide-aspect tablet computers in the near future (as of 2012).

A wide version of the UXGA format. This display aspect ratio was popular on high-end 15" and 17" widescreen notebook computers, as well as on many 23–27" widescreen LCD monitors, until ca. 2010. It is also a popular resolution for home cinema projectors, besides 1080p, in order to show non-widescreen material slightly taller than widescreen (and therefore also slightly wider than it might otherwise be), and is the highest resolution supported by single-link DVI at standard colour depth and scan rate (i.e., no less than 24 bpp and 60 Hz non-interlaced)

A version of the XGA format, the native resolution for many 30" widescreen LCD monitors. Also, the highest resolution supported by dual-link DVI at a standard colour depth and non-interlaced refresh rate (i.e. at least 24 bpp and 60 Hz). Used on MacBook Pro with Retina display (13.3"). Requires 12 MB of memory/bandwidth for a single frame.

Version 2.0 introduces new generalized information blocks primarily intended for UltraHD High Dynamic Range (HDR) displays, such as LCD computer monitors and LCD/OLED televisions with native support for BT.2100 color space and PQ/HLG transfer functions. It also makes optional predefined CRT/LCD timings from DMT and CEA-861 standards, switching to formula-based structures which follow VESA CVT-RB and GTF.

0x28 Tiled display topology block describes displays that consist of multiple physical display panels, each driven by a separate video interface. It is based on block 0x12.

0x0C Display device data block provides information about display panel characteristics for embedded applications, such as display technology, panel type, and pixel response times.

First standard to support 8K resolution (7680 x 4320) at 60 Hz refresh rate with full-color 4:4:4 resolution, including with 30 bits per pixel (bpp) for HDR-10 support

When using only two lanes on the USB-C connector via DP Alt Mode to allow for simultaneous SuperSpeed USB data and video, DP 2.0 can enable such configurations as:Three 4K (3840×2160) displays @144Hz and 30 bpp 4:4:4 HDR (with DSC)

+++ b/drivers/gpu/drm/panel/Kconfig@@ -433,6 +433,15 @@ config DRM_PANEL_TRULY_NT35597_WQXGA Say Y here if you want to enable support for Truly NT35597 WQXGA Dual DSI

+++ b/drivers/gpu/drm/panel/Makefile@@ -46,4 +46,5 @@ obj-$(CONFIG_DRM_PANEL_TPO_TD028TTEC1) += panel-tpo-td028ttec1.o obj-$(CONFIG_DRM_PANEL_TPO_TD043MTEA1) += panel-tpo-td043mtea1.o

The New Bioenno Power 160 Watt Hour Renewable Power Pack, Model BPP-160, replaces the legacy BPP-120 Power Pack with expanded watt-hour capacity, increased run-time, 2 x AC outlets, all in a portable configuration. The BPP-160 continues where the BPP-120 left off, with some great enhancements!

Putting out more power than a 12V 30Ah SLA battery which can only output DC and weighs in at an incredible 23 pounds, the BPP-160 weighs only 3.5 pounds outputs DC, AC and is chargeable through not only the grid but also the sun! Not only that, the BPP-160 features an at-a-glance LCD display showing capacity and usage and features our advanced computer control system.

Current liquid crystal display (LCD) controller designs incorporate display buffers that only support display data in RGB format. As is generally known, RGB format display data varies in color depth from 8, 16, or 24 bit-per-pixel (bpp). Newer LCD controllers incorporating digital video features, such as video input ports, JPEG, and MPEG functionality, require 16 or 24 bpp color depths to properly display live video or still images. Typically, the display data coming from various modules are converted to RGB format before storage into the display buffer. The support for higher color depths and increased display sizes, strains the memory allocation for the display buffer (internal RAM) because a large portion of the resulting manufacturing cost of an LCD controller is determined by the allocation of silicon for embedded RAM.

For current generations of LCD controllers that support a camera interface and a JPEG CODEC, incoming YUV data from these modules are first converted to 16 bpp or 24 bpp (unpacked 32-bits wide) RGB data format by a YUV-RGB Converter (YRC). The converted data is then stored in the display buffer. However, this process decompresses the display data resulting in a larger RAM requirement for storage in the display buffer. For example, YUV 4:2:2 pixel data coming from the camera interface is 16-bits wide and equivalent to 24 bpp. A resultant YUV-RGB conversion to 24 bpp unpacked (32-bits wide) would increase the memory storage requirement by 2 times. A resultant YUV-RGB conversion to 16 bpp would not increase the memory storage requirement but the resulting image fidelity is decreased (color depth from 24 bpp to 16 bpp).

FIG. 1 is a high-level, simplified schematic diagram of the architecture for a device having a liquid crystal display controller configured to solely support display data in RGB format. The components include central processing unit (CPU) 100 in communication with display controller 102. Display controller 102 is in communication with display panel 104. Display controller 102 is configured to convert any incoming YUV formatted data to RGB format prior to storing the data within a memory of the display controller.

In still yet another embodiment, a digital video device is provided. The digital video device includes a central processing unit (CPU). A display controller is also included. The display controller includes a resizer block configured to receive digital video data defined through a YUV color format. The resizer block is capable of scaling and cropping the digital video data. A conversion module configured to compress the digital video data defined through the YUV color format is included in the display controller. A memory region configured to store the compressed digital video data is provided in the display controller. The digital video device includes a display panel configured to display the stored digital video data. A bus over which the CPU, the display controller and the display panel communicate is also provided.

It should be appreciated that each of the above four formats is equivalent to an RGB color depth of 24 bits per pixel (bpp), thereby allowing varying levels of lossy compression. Table 1 illustrates the memory requirements for each YUV format and compression achieved as compared to RGB data at 24 bpp. TABLE 1 YUV Format Memory/Pixel Compression (compared to RGB) 4:4:4 24 bits 1:1 (24 Bpp packed) 1.3:1 (24 Bpp unpacked, 32 bits) 4:2:2 16 bits 1.5:1 4:1:1 12 bits 2:1 4:2:0 12 bits

Table 2 illustrates the memory requirements for a 320×240 image in each of the compressed YUV formats. One skilled in the art will appreciate that the 320×240 image size is characteristic of a display screen for a personal digital assistant (PDA). However, it should be appreciated that the embodiments described herein are not limited to this size screen and may be applied to any suitable size screen. TABLE 2 24 bpp unpacked RGB 16 bpp RGB YUV 4:2:2 YUV 4:1:1 or 4:2:0 300K Bytes 150K Bytes 150K Bytes 112.5K Bytes

With reference to Table 2, YUV data storage would give a best case savings in memory requirements of 62.5% as compared against RGB 24 bpp unpacked data and a 25% savings against RGB 16 bpp. The worst case savings in memory requirements would be 25% against 24 bpp unpacked RGB and no savings against RGB 16 bpp, however, the YUV format offers higher color depth than the RGB format.

FIG. 2 is a high level schematic diagram of the system architecture for a device configured to efficiently utilize a compression state of incoming color data in accordance with one embodiment of the invention. Device 115 includes central processing unit (CPU) 110 display controller 112 and display panel 120. CPU 110 is in communication with display controller 112 through bus 118. Display panel 120 is in communication with display panel controller 112. Display controller 112 includes memory region 114 and sub-sampling module 116. As will be explained further below, sub-sampling module 116 is configured to sub-sample incoming color image data in order to minimize an amount of capacity used in memory 114 to store the incoming color image data. In one embodiment, the incoming color image data is in a YUV format that is received through a 4:2:2 compression scheme. Thus, sub-sampling module 116 may further increase the compression, i.e., convert the 4:2:2 compression scheme to either a 4:1:1 compression scheme or a 4:2:0 compression scheme.

FIG. 3 is a more detailed schematic diagram of the components of a display controller configured to further compress digital video input received in a compressed format in accordance with one embodiment of the invention. Incoming digital data 124 is received by resizer module 126. It should be appreciated that the incoming digital data may originate from any video device, e.g., a digital camera, a video decoder, a Motion Picture Expert Group (MPEG) decoder, etc. Resizer module 126 is configured to adjust a size associated with the incoming digital data for eventual display on a display panel in communication with display controller 112. In one embodiment, resizer module 126 is configured to adjust a crop factor and a scale factor associated with the incoming digital data. That is, by adjusting the crop factor and the scale factor, the image is cropped and scaled, respectively, for output. In other words, the function of the resize and scaler block (resizer module 126) is to trim or scale image data coming from either the Digital Video Input port, or from display memory, i.e., JPEG encode from display memory. Resizer module 126 is associated with a YUV-YUV converter (converter 128) to select the appropriate YUV output format. The output of resizer module 126 and converter 128, which make up sub-sampling module 116, may be stored in display memory or sent to the JPEG CODEC.

Converter 128 is configured to sub-sample the image data in order to further compress the data to conserve space within memory 114. For example, the incoming digital data is typically of a YUV color format which has been compressed through a 4:2:2 compression scheme. Converter 128 will take the color data in the 4:2:2 compression scheme and sub-sample the data to convert the data to a YUV format having either a 4:1:1 compression ratio or a 4:2:0 compression ratio. The further compressed YUV data is then stored in memory 114. As illustrated in Tables 1 and 2, a significant savings may be achieved by storing the further compressed YUV data in memory 114 as opposed to 24 bpp RGB data.

Still referring to FIG. 3, from memory 114, the data may be transmitted through color space conversion module 134 where the YUV color format is converted to RGB color format in order to be displayed on liquid crystal display (LCD) display 120-1. Alternatively, the YUV data stored in memory 114 may be transmitted directly to a device or apparatus configured to accept YUV data. A video encoder or a Motion Picture Expert Group encoder are exemplary devices which can accept the YUV format. As central processing units generally operate on RGB data, CPU 110, when communicating with display controller 112, may utilize color space conversion modules 132-1 and 132-2 to convert the data between RGB format and YUV format. Thus, when writing to display controller 112, then RGB data is converted to YUV data through module 132-2. On the other hand, where the CPU is reading from memory 114 of display controller 112, the YUV data is converted to RGB data through module 132-1. That is, color space conversion (CSC) blocks 132-1 and 132-2 are placed between the CPU host interface and the display buffer to enable the host CPU to still read and write data to the memory in RGB format (or YUV directly by bypassing CSC blocks 132-1 and 132-2). A YUV-RGB Converter (YRC) is implemented in the read path and a RGB-YUV Converter (RYC) is implemented in the write path. It should be appreciated that the YRC output and RYC input is configurable to different bpp modes. In one embodiment, CPU host accesses to the internal register and JPEG CODEC are not converted and the data is read/written directly. The CPU host software should be aware that when display data is written to internal memory, the value read back may be different since the write data may have been downsampled by compression. However, in most display applications, the CPU host rarely requires read back verification of display data from the frame buffer.

FIG. 5 is a flow chart diagram illustrating the method operations for enhancing storage capability for display controller in accordance with one embodiment of the invention. The method initiates with operation 150 where video display data having a color format associated with a first sub-sampling scheme is received. In one embodiment, the video display data is received from a digital video device, e.g., digital camera, video decoder, MPEG decoder. In another embodiment, the first sub-sampling scheme is a 4:2:2 compression scheme associated with YUV color formatted data. The method then advances to operation 152 where a size associated with the video display data is adjusted. Here, a scale factor and a crop factor may be applied to the data in order to adjust the size. That is, the size is adjusted for the eventual display panel to which the data may be output.

The method of FIG. 5 then proceeds to operation 154 where the video display data is compressed through a second sub-sampling scheme. Here, as described above, the 4:2:2 compression scheme sub-sampled to produce either a 4:2:1 compression scheme or a 4:2:0 compression scheme. It should be appreciated that the terms sub-sampled and down sampled may be used interchangeably herein. Thus, through the conversion block mentioned above with reference to FIGS. 3 and 4, the video display data is further compressed in order to store the video display data in memory in the most efficient manner. One skilled in the art will appreciate that hand-held electronic devices are generally limited in the amount of resources, i.e., computing power and memory, therefore, the compression achieved will further reduce the amount of space occupied in memory by the display data. Thus, memory space is freed up for other purposes through the embodiments described herein. The method then moves to operation 156 where the compressed data having the color format is stored. As described above, with reference to FIGS. 3 and 4, the stored data may be accessed and displayed directly by a YUV display device. Alternatively, the stored data may be accessed and converted to an RGB color format for eventual display on a liquid crystal display (LCD) device. Of course, the data may also be accessed and converted eventually to a JPEG file or some other suitable lossy compression scheme for eventually display. Additionally, it should be appreciated that the compressed video display data may be converted to a second color format, e.g., RGB color format, and then stored within memory 114. However, a memory savings associated with the storage of the compressed YUV formatted data would not be achieved here.

In summary, the above-described embodiments allow for the efficient use of memory by utilizing the compression of incoming YUV color data. That is, YUV data having a 4:2:2 format is associated with a bit size of 16 bits per pixel while RGB data is associated with a bit size of 24 bits per pixel. Therefore, it is optimal to store YUV data in a 4:2:2 compression scheme or some other lower compression scheme in memory. The display controller described herein is a LCD controller in one embodiment. However, the display controller is not limited to a LCD controller as the display controller may be any suitable display controller.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey