lvds lcd module free sample

LVDS displays can vary a lot. LVDS displays are not governed by a set of well defined rules like MIPI DSI displays are. Therefore, it is up to the LCD manufacturer and the LVDS display driver IC manufacturer to use LVDS interface as they please, as long as they follow the physical interface and logic levels.

Based on this data, we can pick an LVDS transmitter IC. SN75LVDS84 from Texas Instruments is great for use with LCD displays that can be driven by an STM32.

This 10.1 inch TFT LCD display has a 1024x600 resolution screen with IPS technology, which delivers sunlight readable brightness, better color reproduction, better image consistency, and better optical characteristics at any angle. For extra protection, this 24-bit true color TFT also includes an EMI filter on the input power supply line. This 10.1" display is RoHS compliant with LVDS interface, and does not include a touchscreen. This 10.1" IPS display has been designed with the same mechanical footprint and pinout and includes the same HX8282 driver IC as the TN display, making this a compatible replacement option for the TN models.

NMLCD-21519201080-LVDS is a color active matrix TFT LCD open cell using amorphous silicon TFT"s (Thin Film Transistors) as an active switching devices. This open cell has a 21.5 inch diagonally measured active area with FHD resolutions (1920 horizontal by 1080 vertical pixel array). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical stripe and this module can display 16.7M colors. The TFT-LCD panel used for this module is adapted for a low reflection and higher color type.

Then to enter "Free-Running" mode, the uC in a similar manner issues a "Read Burst" command, holding DQM active until the uC has a chance to release the Data/Command/Address pins. At which point, the uC is completely out of the picture, and the data previously stored in the SDRAM is output right back to its Command/Address inputs. At the end of the first page is a command to read the next page. (Note that even after wiring all the Address/Command pins to DQ pins, there are *several* DQ pins remaining, which can then be used for other purposes, like driving an LCD, etc).

As implemented for the LCD, the last page issues a "Read" command back to Page 0. Thus, the same pages are output continuously and repeatedly (refreshing the LCD image). The simple act of Activating a page in memory causes that memory page to be refreshed. And, again, SDRAM refresh isn"t necessary nearly as often as specified (once every 10 seconds seems to be plenty). Thus, no explicit "refresh" commands are necessary in this case, since each page is cycled through repeatedly.

So, what can be done with these complex jump-patterns... well, imagine it a bit like a flow-chart... Possibly a state-machine. In the case of the LVDS-LCD, rather than writing the same data repeatedly in a linear fashion, we could have several states. The serial data-patterns sent during a Horizontal Front Porch, for instance, are identical, but they must be repeated a dozen or more times in each row, and repeated for every row. Instead of loading a dozen *768 identical patterns in the SDRAM, why not have it loaded once and have it cycle? It takes a bit more real-time control from the microcontroller, but could be useful to jump between states like this. And some of these jumps don"t require uC control at all, such as jumping from the end of each drawn-row to the Horizontal Front Porch. In other words, 768 separate locations all end up jumping to the same location.

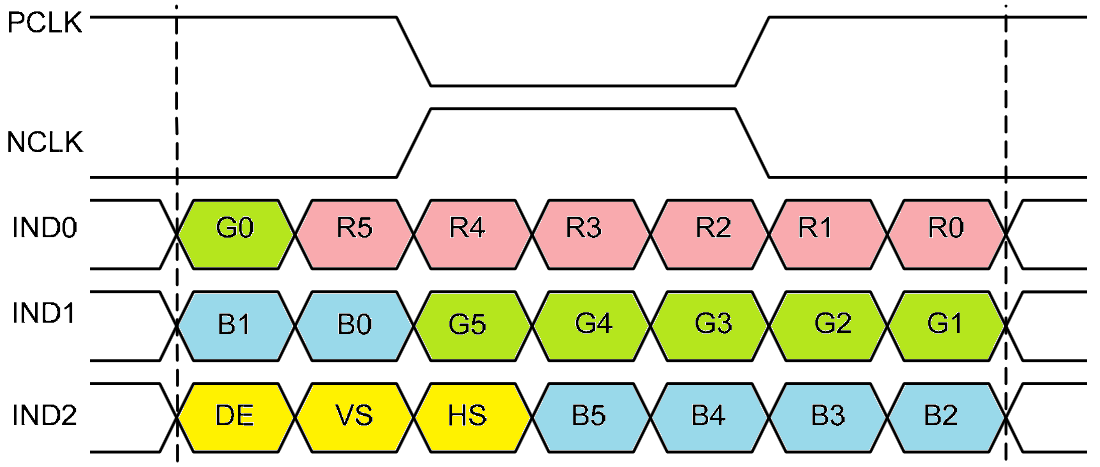

The circuitry has changed slightly, and I"m straying a bit from my desire to avoid glue-logic... In sdramThing2.0, data and Free-Running commands were all stored in the same "group" of chips. Now, data has been moved to the Side-Kick. Since I"m still working with the LCD display (for testing-purposes), this isn"t quite so cut-and-dried. The timing information (Pixel-Clock and DE/Vsync/Hsync, which is combined with the Blue values) is still loaded into the Free-Runner, such that it won"t change when sampling. The other two pins ("Red" and "Green") are connected to the Side-Kick for Sample/Repeat.

The parallel interface typically controls the LCD via 8 data pins and 3 control lines. The control lines used are Enable (E), Register Select (RS), and Read/Write (R/W). RS tells the LCD module if the information being sent is an Instruction or Data. The Enable tells the LCD module that the data or instruction in the register is ready to be interpreted by the LCD Module. Some controllers may have more than one Enable Control Line. The Read/Write tells the module whether to write data or read data from the register.

Serial LCD controllers typically have one Serial Data Line that writes data and cannot read. Normally, a Register Select Line(Sometimes designated A0) is used to tell the controller whether the incoming data is display information or a controller command

SPI, or Serial Peripheral Interface bus, is a synchronous (data is synchronized to the clock) serial data link standard that operates in full duplex mode, which means that devices that can communicate with one another simultaneously. To do this, two data lines are required. With this standard, devices communicate in a master/slave mode, where the master device (host processor) initiates the data and the clock. The LCD module is the (or one of the) peripheral slave device(s) attached to the data bus. Multiple peripherals (display modules and other devices) are addressed on the same serial data bus. However, the LCD module will only listen to the data it sees when the Chip Select line is active (usually low). If the Chip Select line is inactive (usually High), the LCD module listens to the data on the bus, but ignores it. The SDO line is not active when this state occurs. The SPI bus is comprised of four logic signals, two control lines and two data lines and is commonly referred to as SPI (4 wire).

With CS (Chip-Select) the corresponding peripheral device is selected by the LCD Controller. This pin is mostly active-low. In the unselected state the SDO lines are hi-impedance and therefore inactive. The clock line SCL is brought to the device whether it is selected or not. The clock serves as synchronization of the data communication.

The chip select signal CS is optional for a single device system, because you could tie the CS input at the LCD Module low, if the other lines are dedicated to SPI use. This is sometimes called a 3 Wire SPI Interface.

SPI Data transmissions usually involve two shift registers. Most display module applications normally use 8-bit words. However, different size words, such as 12 bit, are also used. By convention, the most significant bit is shifted out of one shift register while the least significant bit is shifted in. The word is then written into memory if the CS (chip-select) is low (active). If not, the data is ignored.

LVDS (Low Voltage Differential Signaling) technology provides a port with low voltage difference and differential signals. Developed by NS Technology Co., the American company uses digital video signal to resolve the excess amount of resource consumed and reducing EMI (Electromagnetic Interference) while transferring high bit rate data using TTL (Transistor-Transistor Logic). LVDS ports are able to perform differential data transfer between PCB traces or balanced cables with a relatively low output voltage swing (350mV), allowing a transfer speed up to several hundred megabit per second with low voltage difference. As a result, low voltage swing and low current drive applications have led to dramatic reduction in resource consumption and noise.

Using single circuit for transfers, the port implements 6 bit data for each primary color signals, thus delivering 18 bit RGB data. This output is also known as the 18 bit or 18 bit LVDS port.

Using two-path dual circuit transfers, the port implements 6 bit data for each primary color signals, delivering 18 bit for single and dual channel data, totaling 36 bit RGB data. This output is also known as the 36 bit or 36 bit LVDS port.

Using single circuit for transfers, the port implements 8 bit data for each primary color signals, delivering 24 bit RDB data. This output is also known as the 24 bit or 24 bit LVDS port.

Using two-path dual circuit transfers, the port implements 8 bit data for each primary color signals, delivering 24 bit for single and dual channel data, totaling 48 bit RGB data. This output is also known as the 48 bit or 48 bit LVDS port.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey