fpga lcd display free sample

The first part of the series discussed the implementation of I2C controller using an FPGA. The focus in this part is interfacing FPGA with LCD. The basics of LCD operation, hardware interconnection and VHDL code along with its description are presented here.

Liquid crystals are materials that exhibit properties of both solids and liquids. These can be classified as nematic, smectic and cholesteric. Nematic liquid crystals are generally used in LCD fabrication with the twisted nematic material being the most common. Fig. 1 shows the construction of a twisted nematic LCD display. As we can see from the figure, it comprises a cell of liquid crystal fluid, conductive electrodes, a set of polarisers and a glass casing.

An LCD controls the transmission of light by changing the polarisation of the light passing through the liquid crystals with the help of an externally applied voltage. As LCDs do not emit their own light, backlighting is used to enhance the legibility of the display in dark conditions. Backlighting is done using incandescent lamps, LEDs or electro-luminescent lamps.

LCDs have the capability to produce both positive as well as negative images. A positive image, defined as a dark image on a light background, is produced when the pixel that is ‘off’ is transparent and a pixel that is ‘on’ is opaque. In these displays, the front and the rear polarisers are perpendicular to each other.

A negative image is a light image on a dark background and is produced when a pixel that is ‘off’ is opaque and a pixel that is ‘on’ is transparent. This mode is typically used only when there is a backlight and the ambient lighting conditions are medium to dim. In these displays, the front and the rear polarisers are aligned to each other.

LCDs can be classified as direct drive and multiplex drive displays depending upon the technique used to drive them. Direct drive displays, also known as static drive displays, have an independent driver for each pixel. The drive voltage in this case is a square waveform having two voltage levels, namely, ground and VCC. However, as the display size increases, the drive circuitry becomes very complex. Hence, multiplex drive circuits are used for larger displays. Such displays reduce the total number of interconnections between the LCD and the driver. These have more than one backplane and the driver produces amplitude-varying, time-synchronised waveforms for both the segments and backplanes.

LCDs are non-emissive devices, that is, they do not generate light of their own. Depending upon the mode of transmission of light in LCDs, these are classified as reflective, transmissive and transreflective displays.

Reflective LCD displays have a reflector attached to the rear polariser which reflects incoming light evenly back into the display. Fig. 2 shows the principle of operation of reflective LCD displays. Such displays rely on the ambient light to operate and do not work in dark conditions. These produce only positive images. The front and the rear polarisers are perpendicular to each other. Such displays are commonly used in calculators and digital wrist watches.

In transmissive LCD displays, back light is used as the light source. Most of these displays operate in the negative mode, with the text displayed in light colour and the background in a dark colour. Fig. 3 shows the basic construction of a transmissive display. Negative transmissive displays have front and rear polarisers in parallel with each other whereas positive transmissive displays have the front and the rear polarisers perpendicular to each other.

Transmissive displays are good for very low light level conditions. They offer very poor contrast when used under direct sunlight because sunlight swamps out the backlighting. These are generally used in medical devices, electronics test and measuring equipment and in laptops.

Transreflective displays are a combination of reflective and transmissive displays (Fig. 4). A white or silver translucent material is applied to the rear of the display, which reflects some of the ambient light back to the observer. It also allows the backlight to pass through. These are good for use in varying light conditions. However, they offer poorer contrast ratios than reflective displays.

This article covers FPGA projects from beginners to expert level. You can find hereFPGA projects for engineering students, cool FPGA projects and FPGA projects used in commercial products. All FPGA projects are with free and downloadable source code, allowing you to use the projects at home or at work. Our goal is to help users understand FPGA’s role in the industry and how FPGAs are used to implement various functions in an electronic products.

The first FPGA project on the list is a standard spread spectrum system is of the “direct sequence” or “frequency hopping” type, or else some combination of these two “hybrids”. In frequency Hopping, the system” hops” from frequency to frequency over a wide band. The pattern in which frequencies are engaged is a role of a code sequence, and the rate of hopping from one frequency to another frequency is a function of the data rate.

This FPGA project aims to design, simulate and develop a transmitter and a receiver for frequency hopped system on FPGA using VHDL. This project’s completion covers the art of secure digital communications that is now being exploited for commercial, industrial and military purposes.

Canny edge detection is a multi-stage algorithm for vision processing that generates a binary output image (edge or no edge for complex vision algorithms such as number plate identification). Detection of Canny edges can eliminate irrelevant image information and provide a clear binary output for each pixel. High-performance computing is traditionally implemented by Canny edge detection. However, you can now implement vision algorithms for low-power mobile applications on embedded platforms. Multiple processing stages include vision algorithms such as Canny. Usually, processors have to fetch, process, and write the input image frame from external memory back to external memory. For the next processing block, the processor repeats this process. This conventional shuffling of memory among blocks is inefficient: In this FPGA project, we have implemented the Canny edge detector with a 9×9 mask. Able to produce 1 pixel-per-clock-cycle. We have successfully implemented on a Virtex4 up to 400Mhz clock frequency. The purpose of this project is to detect the sharp edges from the images.

Direct digital synthesis (DDS) produces an analogue waveform, typically a sinusoidal wave, by generating a digital time-varying signal and then making a digital-to-analogue conversion. Since operations are predominantly digital inside a DDS system, it can offer fast switching between output frequencies, satisfactory frequency resolution, and operation over a wide range of frequencies. Several frequency generation possibilities are available to a designer, ranging from phase-locked-loop (PLL)-based very high-frequency synthesis techniques to dynamic digital-to-analogue converter (DAC) output programming to produce arbitrary waveforms at lower frequencies. But in both communications and industrial applications, the DDS approach is rapidly gaining acceptance for solving frequency (or waveform) generation requirements, since single-chip IC devices can produce programmable analogue output waveforms only and with high resolution and accuracy. In this FPGA project, we have implemented the high-precision Direct Digital Frequency Synthesizer (DDFS) used in digital up/down conversion, and the generation of periodic waveforms. For example, sine wave, cosine wave, square and sawtooth waves. The output is 16-bit signed data samples. This project is ideal for the quadrature signal generation, digital modulation/demodulation and software radio applications. Also, it can be used as oscillators and generation of complex quadrature signals.

A cryptographic hash function is a hashing algorithm. It is a mathematical algorithm that maps arbitrary-size information to a fixed-size hash. In IT, cryptographic hash functions are used commonly. We may use them for digital signatures, authentication codes for messages (MACs) and other authentication types. We can also use them for indexing data in hash tables, for fingerprinting, identifying files, detecting duplicates or as checksums (we can perceive if a sent file didn’t suffer accidental or intentional data corruption). The algorithm for a hash function is designed to be a one-way function that cannot be reversed. Multiple hashing algorithms have, however, been corrupted in recent years. This FPGA project aims to provide the FPGA implementation of the hashing algorithms to generate the hashes for the Proof-of-Work (Pow). In this project, we have developed the Blockchain system to mine the 0xbitcoin. We have used the CVP 13 FPGA board and implement the Keccak-256 algorithm on it. We have achieved the 500 Giga hashes per second.

High-performance digital electronic circuits for onboard processing of return signals in airborne precipitation – radar measurement devices in commercially available fields have been developed – programmable gate arrays (FPGAs). Previously, it was common practice to downlink the radar-return data to a post-processing ground station – an expensive practice that eliminates the near-real-time use of automated targeting data. In theory, a system of about 20 personal computer-type microprocessors could perform onboard processing; compared to such a system, the current FPGA-based processor is much smaller and consumes much less power. Alternatively, an application-specific integrated circuit (ASIC) may be used for onboard processing. However, compared to an ASIC implementation, the current FPGA implementation provides the advantages of (1) greater versatility for research applications such as the current one and (2) lower costs in the limited production volumes typical of research applications. Implementing the radar signal processing techniques on the FPGA is the significant domain. In this FPGA project, we have selected a few algorithms in the FPGA. Implement the Radar Equation along with the pulse compression algorithm, Implement Doppler shift to detect target velocity, and implement pulse-Doppler waveforms.

Implement a constant false alarm rate (CFAR) detection adaptive algorithm on FPGA used in radar systems to detect target signal against a background of noise, clutter and interference. Aim of this project to detect the target from a noisy condition.

The Fast Fourier Transform (FFT) is a fundamental building block used in DSP systems, with applications ranging from Digital MODEMs based on OFDM to algorithms for Ultrasound, RADAR and CT image reconstruction. Although its algorithm is straightforward to understand, for hardware engineers today, the implementation architectures and details’ variants are essential and are an enormous time sink. In this FPGA project, we have implemented the Fast Fourier Transform on the FPGA; we have used the butterfly technique to implement it on the FPGA. The FFT is used to perform the find the frequency component in a complex signals plan. It’s a 4096-point FFT. With device-level fixed point C-models, this FFT project core offers four different architectures and reduces the average implementation time from 3-6 months to the push of a button. It also gives users the opportunity to make complex trade-offs needed by both the DSP algorithm and hardware engineers for all the appropriate algorithms and implementation. The FFT project emphasizes increased dynamic range by growing the support for data and phase factor width up to 34 bits and supporting IEEE single accuracy floating-point data form. By using a higher precision fixed-point FFT internally to achieve comparable noise efficiency.

A Digital Decoder IC is a device that transforms one digital format into another, and the Binary Coded Decimal (BCD) to 7-Segment Display Decoder is one of the most widely used devices for doing this. 7-segment LED (Light Emitting Diode) or LCD (Liquid Crystal Display) style displays offer a very convenient way for numbers, letters or even alpha-numerical characters to display information or digital data. Usually, 7-segment displays consist of seven individual-coloured LEDs (called segments). The correct combination of LED segments needs to be illuminated on display to generate the necessary numbers or HEX characters from 0 to 9 and A to F, correspondingly, and BCD to 7-segment display decoders 74LS47 do just that. A Seven-Segment Display is an indicator widely used to show details to the consumer by FPGA designers. In VHDL code to convert from binary to compatible seven-segment display can be done quickly. Several applications may need one or more seven-segment displays to be used, i.e., counter, stopwatch, current measurement. In this cool FPGA project, we have BCD to 7-segment display decoder. The VHDL entity takes 4-bit BCD as an input and outputs the 7-bit decoded output for driving the display unit. A seven-segment display is being used to display decimal digits. They have LED elements which become active when the input is zero.

The digital clock’s primary purpose is to use the 7-segment panel on the Artix-7 FPGA Board to digitally display the time. By default, the digital clock shows the runtime and the time can be adjusted using the time set allocated to the onboard switch. The alarm role is also configured using the alarm set and the alarm on the kit’s switch. The developed digital clock is a format designed for 24 clocks. For the hardware implementation of the digital clock, this project uses FPGA. The clock starts as soon as the FPGA is turned on. The FPGA and onboard clock will produce the Timing signals. You can set the clock time and the alarm time using the dip switches on the board. Using digital operations: counting, comparing, increasing and decreasing, the suggested digital clock design is improved. Using the time set switch, the clock time can be set, and the alarm time can be set using the alarm set switch. If the clock is equal to the alarm time, the alarm will be on. By using the push buttons on the monitor, minutes and hours can be increased and decremented. In this FPGA project, we have implemented the Digital clock on FPGA. The module has one input “the source clock of the FPGA” and has 3 outputs (hour hand, minute hand, and second hand). We have displayed the output on the Seven Segment Display of the Artix-7 FPGA.

Compression of image processing images can enhance the Device efficiency by minimizing cost and time to minimize without a significant reduction, image storage, and transmission of the picture’s quality. It is possible to describe a monochrome picture with each pixel over a matrix of picture elements (pixels), Described by the grayscale value of 8 bits. This depiction of Image data might require significant storage requirements. Compression of the image aims to decrease the size of the representation and, at the same time, to preserve much of the representation. It can be lossy or lossless compression. Compression with Lossy gives Compared to lossless, a higher reduction in data volume Compression; but just an approximation of the initial compression. It is possible to recreate the image. There are many norms for compression of images and Like Joint Photographic Experts Decompression (CODEC) Team, Format for Graphics Interchange (GIF), Portable Network Graphics (PNG), Picture Labeling Format of File (TIFF). The most commonly used JPEG compression. The type of lossy image compression used and based on the Discrete transform of cosine (DCT). Depending on the details found inside the image and the image, a compressed image in JPEG format may be approximately 10 percent of compression’s original size efficiency. The results in a reduction of 90 percent in the Bandwidth needed. This FPGA project includes a complete JPEG Hardware with 4:1:1 subsampling, able to compress at a rate of up to 42 images per second at the maximum resolution (256×256 @ 60 MHz). The FPGA input is RGB input (row-wise) and outputs to memory the compressed JPEG image.

We built a simple FM receiver on the FPGA that demodulated the FM modulated frequency signal. We have used the dipole antenna to receive the FM signals then used the FM demodulator logic to demodulate the received signal. First, we used the ADC to convert the analogue FM signal to the digital and then process it digitally to remove the carrier waves to get an only pure sound wave from the broadcast station.

In physics, the square root function sqrt(x) is an essential elementary function—Digital signal and image processing, ANN equations. The Field Programmable Gate Arrays (FPGAs) are currently being extended to solve the problem. Problems where the calculations of the function sqrt(x) are necessary. The FPGA manufacturers and third-party companies are proposing various IP cores of sqrt calculation (x). But these IP cores were developed decades ago and typically did not take the characteristics of the latest generations of FPGA into account. They do need upgrades, therefore. An enhanced feature algorithm to calculate sqrt (x) is suggested in this FPGA project, which fits the FPGA implementation I have written a code for finding the square root of a signed number on FPGA using VHDL as a programming interface. The code is based on “Non-Restoring Square Root algorithm”. The code takes one signed number, 32 bit in size and returns the square root, which is also of signed type with 16-bit size. The modified algorithm, CORDIC-like, for It is proposed to derive the square root equation. The algorithm is separated by the reduced sum of Steps proportional to the data given, and the outcome is Width of bits. In VHDL, the algorithm is defined and is Built to enforce the FPGA. This is the most Efficient at the floating-point throughout its implementation Module Square Root.

The detection of errors decides if the data obtained via a medium is Corrupted while transmitting. To achieve this, the transmitter uses a feature to measure and append the checksum value for the data Checksum for the original frame of data. To create a checksum for the received data frame, the receiver uses the same calculation technique and compares the received checksum to the transmitted checksum. If the two checksum values are identical, the data frame obtained is right, and there was no data corruption during transmission or storage. In this FPGA project, we have developed the CRC on FPGA to detect the error in the transmission message. The advantage of the CRC circuit generated is that the input is assumed to be serially fed into the circuit. Meaning, the input can be long and still the FPGA resource usage will remain the same.

A ring counter is a kind of counter made up of flip-flops connected to a shift register, with the last flip-flop output fed to the first one’s input, forming a “circular” or “ring” structure. In hardware design (e.g., ASIC and FPGA design), ring counters are also used for constructing finite-state machines. A binary counter will require an adder circuit that is considerably more complicated than a ring counter and has a more significant propagation delay as the number of bits increases, whereas a ring counter’s propagation delay would be almost constant regardless of the code’s number of bits. In this FPGA project, a ring counter is implemented on the FPGA, consisting of a series of flip flops connected positively. The circuit is an especial type of shift register where the last flip-flop’s output is feedback to the first flip-flop input.

Increased demand for data security is an undeniable fact. To achieve higher security, cryptographic algorithms play an essential role in protecting data from unapproved usage. In this FPGA project, we present a cryptoprocessor using Advanced Encryption Standard (AES). The AES is integrated with a 32-bit general-purpose 5- stage pipelined MIPS processor. The integrated AES module is a fully pipelined module which follows the inner round and outer round pipeline design. The results show that the presented pipeline version of the AES algorithm and the MIPS processor outperform traditional methods. At the operating frequency of 553 MHz, the proposed design can achieve the throughput of 58 Gbps, the latency of 240 ns, and the minimum power consumption of 76 MW.

Instead of reading and writing to individual addresses, an SPI is a good option for communicating with low-speed computers that are accessed intermittently and transfer data streams. An SPI is an excellent option if we can take advantage of its full-duplex capability to send and receive data simultaneously. In VHDL, this design is implemented. The Lattice iCECube2TM Position and Route tool integrated with the Synplify Pro synthesis tool is used for the design execution. The architecture uses an ultra-low-density FPGA iCE40TM and can be targeted to other members of the iCE40 family.

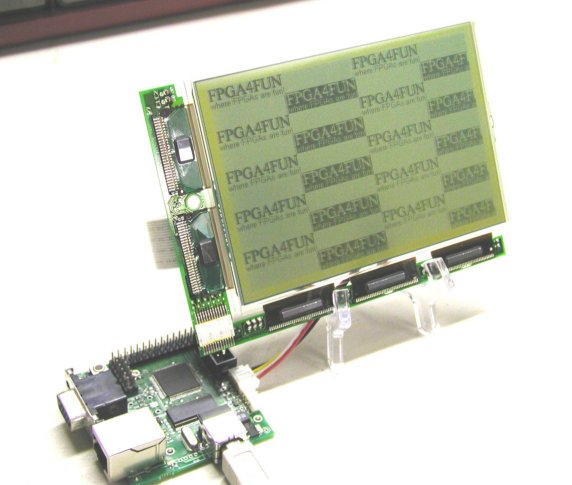

Freedom on what is displayed (frame-buffer/on-the-fly video/sprites/hardware mouse cursor ... or any combination of these)Easy to attach to microcontrollers

Prior to be able to display anything on the panel, we need to generate video-sync signals (H-sync and V-sync).The LCD used for this project has the following characteristics:Monochrome, with a 480x320 resolution (about 150000 pixels).

Not shown above is how the RAM is written. The easiest is to treat it as a ROM (the RAM content is part of the FPGA configuration, and doesn"t change while the FPGA is running).

The drawback of rasterized bitmaps is that you require a large enough RAM to hold the state of each pixel of the bitmap. That"s expensive using internal FPGA RAM, so external RAM is often used instead.

RotozoomA Rotozoom is an efficient method to display a bitmap with linear geometric distortions. In particular, that allows easy rotating and zooming of a picture.

Let"s assume the word "Hello" is somewhere on the screen. In ASCII, that uses 5 bytes (0x48, 0x65, 0x6C, 0x6C, 0x6F). Our simple character generator uses one RAM to hold the characters to display, and one ROM to hold the font.

A few details:Because my LCD panel takes 4-pixels per clock, we need 2 clocks for 1 character width (1 character width=8 pixels). That"s why "Character RAM" uses "CounterX[6:1]" instead of "CounterX[5:0]" above.

The 6x8 font allows for more characters to be displayed (and looks better on the panel too!). My particular panel width is 480 pixels, which translates conveniently into 80 columns.

IP listNEW : LT24 / ILI9341 LCD display Application Note !We’ll show you how to use this LCD display (which has the reputation of being complex) with two Reference Designs : one purely Hardware and one using an embedded processor.

_Ready for Telephone-type Numeric Keypad, but easy to adapt to any matrix keyboard.2-lines LCD Display Controller in VHDL. (FREE IP)This VHDL controller (compact and very efficient) handles the venerable and ubiquitous 2x16 LCD.R/C Servo Controller. (FREE IP)A Cascadable 8-bits ( 0.7° resolution) Pulse Width controller to drive standard and widely available R/C Servos. Great for Hobbyist robotics projects.High Performance 32 bits parallel CRC16 calculation (FREE IP)Calculate over 6 Gigabits per second on cheap FPGA (Cyclone III).For personal use only !6809 System This is not really a free IP but you can try this complete 6809 system on an FPGA board.Simple PS/2 Controller (FREE IP)This simple and very compact version is suitable to read from a PS/2 keyboard.

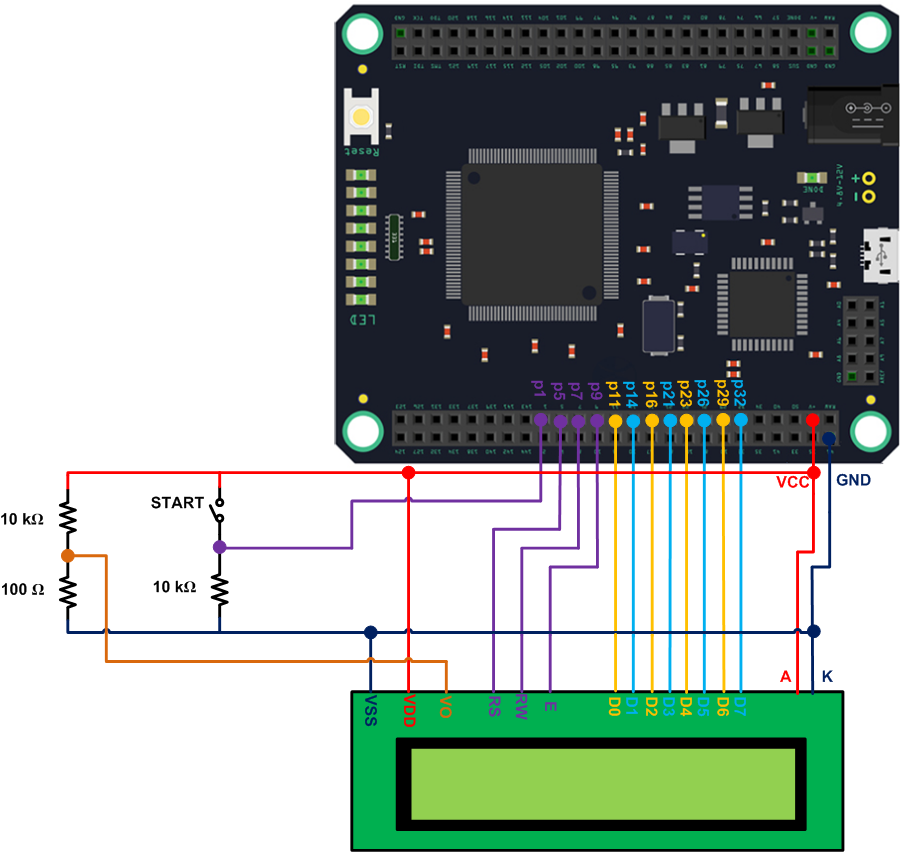

In this example, we will develop a driver for the 16x2 character LCD on the ML505/6/7 board. The LCD driver will be mostly a Microblaze design, as opposed to being an IP design. The physical interface to the LCD will be made through a GPIO peripheral. The signal timing requirements of the LCD will be achieved by using a Timer peripheral. The functions contained in the software application will control what is shown on the LCD. The main function of the software application will provide a simple example of how to clear the display, write a message on the LCD and to change the cursor location.

The design is built on the interface specifications contained in the LCD datasheet. The connections to the FPGA are found on page 12 of the ML50x schematics. It is recommended that you read those documents before following this design.

We have now created an instance of the GPIO peripheral in our design. Later, we will modify the constraints file to connect the GPIO peripheral IO port to the LCD.

We now add a timer peripheral to the project to allow the Microblaze to measure time delays. A delay function will be used to create the required signal timing for the LCD interface. Follow these steps to add the peripheral:

The GPIO peripheral that we added to the design must be linked to the external pins on the FPGA that in turn connect to the LCD. The LCD interface consists of the 7 signals listed below. They are shown with pin description, pin name from the LCD datasheet, and the net name from the ML505 schematic. In brackets are the corresponding FPGA pins that they connect to on the ML505 board.

The software application controls the LCD interface signals by writing to the GPIO peripheral. It contains several functions for performing the signal sequences for writing characters to the LCD, moving the cursor, etc. To achieve the required signal timing, the application contains a delay function that uses the Timer peripheral.

The software application simply initializes the LCD, clears the display and writes a message over the two lines. The LCD should look as shown in the image below.

I want to build on the design created in Workshop 4 of the Summer of FPGA series with the Ultra96-V2. That workshop created a design to use the UART click board and a PWM IP to drive the backlight on a LCD Mini Click board. The foundation of what follows is that design, and I"m assuming that if you are following along, you have that in place and you can fill in the simple blanks without me describing them in detail. I have additional useful posts associated with that workshop:

In Part One, I tested a design for emitting an SPI signal from the PL to the Low Speed Header that the Click Mezzanine sits in. In this part, I will incorporate that design into the existing solution and create the actual PS software that will interact with the LCD Mini Click.

The LCD Mini Click has a digipot that, by default, powers up at midrange (actually, it is a non-volatile potentiometer so it powers up to its last setting.) When the LCD operates in 2-line mode then the contrast is too low for the text to be visible at the default setting so the contrast must be adjusted. This is accessed via the "AN" pin on the MikroBus (or, as labelled on the Click Board, CS2) and unfortunately that pin is allocated as an input to the ADC on the Click Mezzanine so there is no direct way of addressing the digipot. A number of possible solutions were given in the comments on Post One of this series, but I"ve taken the approach of cross-wiring the CS pin on MikroBus 2 to the AN pin on MikroBus 1 using a temporary, non-soldered solution. In MikroBus 2 I have the I2c/USB UART click board and the CS pin is not connected so is free to use. By wrapping a thin wire around the board"s CS and AN pins before engaging them into the MikroBus headers, the wire makes a connection and is held firmly in place between the bottom of the boards and the headers. A resistance check on my DMM ensures that there is no cross-connection of neighbouring pins when in place. The advantage is this is a temporary fix and doesn"t require me to solder anything and risk damaging the boards.

In Vitis, most of the work will be creating the software interface that sends commands to the LCD Mini Click, based on the actual LCD used. As mentioned in Part One, the LCD is a Topway LMB162XFW module and a readable data sheet is availablehere. It uses a Sitronix ST7066U LCD controller/Driver and a data sheet is available here (although see below for an update on this statement!) Note that there is a much clearer command table in the Sitronix datasheet on page 17 and an even clearer one in the data sheet for the HD44780 linked in the text further below.

Open the project created as part of Workshop 4: this already contains the code for operating the UART Click and PWM of the LCD Mini Click. You could also start from scratch if you"re just going to use my code rather than write your own.

I could just build on these but I don"t like the name which references the LCD backlight - I"m going to do more - and the location the projects are stored also reflects that name. I"ll create a new Application Project called Ultra96v2_LCD_Mini_Click, using the Standalone on psu_cortexa53_0 domain and use an Empty C++ Application template. To make it simple, I can copy the Ultra96_v2_LCD_Backlight source files into the new project, renaming as necessary - I"ve called it lcd_example_app.c. I also imported the code from my SPI_Test application created in Part One so that I can use that for reference; later I deleted it as it was no longer required. My application src directory looks like this:

If you want to have a go at writing your own code, then the following will be useful and save you a bit of research time. Checking the schematic for the LCD Mini Click:

The Port Expander, MCP23S17, is using the Port B GPIOs and the LCD is only wired with 4 data pins thus operates in 4-bit mode; note that pins labelled RS and E are used in the writing of data to the LCD driver IC, HD44780U. The MCP23S17 address pins A0, A1 and A2 are connected to ground giving the driver an address of 0x00. This will need to be reflected in the code written.

The data sheet for the LCD refers to the driver IC as ST7066U which is a Hitachi HD44780U equivalent. Actually, the data sheet is a little confused as it also refers to a ST7066U or equivalent. During development, I found that the initialisation of the LCD was correctly achieved following the HD44780U datasheet, rather than the ST7066U data sheet, and thus that"s the one I used going forward.

For writing instruction data, the RS pin is kept low (Register Select, not Reset!). To actually write in valid data the E pin must be toggled on then off (and should start off). The high-order nibble is sent before the low-order nibble. I couldn"t find timings for the pulses but the instruction table does give execution times - I just need to build in suitable delays. I"m not building a generic library for the LCD so I"m only implementing what is necessary for my own purposes.

The LCD is a 16x2 device but the driver is designed for 40x2. Therefore, each line can contain up to 40 characters although only 16 are shown on the display (to use all 80 you would need to amend the buffer size I use in the software.) To display off-screen characters, the display can be shifted left which will move off the left character and bring on a new right character. The display DRAM addresses are consecutive so writing 45 characters, for example, will display characters 0 to 15 on line 1; 16 to 39 will be off-display on line 1; 40 to 44 will be on line 2. Essentially, this can be viewed as "wraparound".

As the point wasn"t too create a fully functional LCD Mini Click library I haven"t implemented all the possible features of the LCD, e.g. no display shift. Extending it with the extra few features available will be simple enough for anyone who wants to give it a go as the underlying software is well documented and modular:Class (H and CPP) that encapsulates the SPI functionality

I am currently taking my first digital electronics class and my final project is a calculator written in VHDL using a Basys3 board, 16-key keypad, and a 16x2 LCD display with parallel interface, all provided by Digilent. I took a look at the provided example code from the resource library and I just had some questions about how it works. Now, the example code declares a constant before any of the processes, and this constant is an array of std_logic_vectors so it holds a preloaded message "Hello From Digilent" with the necessary function sets and all that preceding the message. In my case, I have to have a way to display the inputs from the keypad on the display and also display the output on the 2nd line of the display. I have the main logic part of the calculator settled, I just want to know how I can direct these signals from the keypad and the output of the computational module (as in the sum, difference, product, etc.) to the LCD display. I have never played with a display before now and never used VHDL or any type of board like the Basys3 before this class, so I guess I"m still quite novice and don"t understand a good part of what the example code is telling me. I do get that the state machine is just cycling through the values in the constant and waits for certain delays to pass through before transitioning between certain states.

Since the values on the display have to be updated live as the user inputs numbers from the keypad and also when there is a value computed, how can I shift from having a constant with a preloaded message to something that can update itself as needed? My idea was keep the idea of the array of std_logic_vectors but only have one value (rather than the 23 or 24 that are preloaded in the current example code) that will update with every key press. I"ll have two of these, one for the inputs (to show the numbers and operations on the first line) and one for the output (to show on the second line). I"m thinking maybe I declare a variable within a process that will update and be sensitive to the key presses?

Also, I tried looking around the reference manual and such but I could not find the function code for how to display information on the 2nd line; so far, stuff only displays on the first line.

Sorry this is such a bulky post. I have had a lot of questions and my professor hasn"t been around much. Also, part of this project is learning to interface with new components, so in my case the keypad and lcd display, and I"m not having much luck without any guidance unfortunately. Thank you for taking the time to read this!

When choosing a development board, consider what you get with it and what you want to use it for. FPGAs are ideal for use with high speed peripherals, and in general it is much easier to buy a board that contains the part you want, rather than trying to add one on later (and inevitably giving up and upgrading to a more capable board). Examples of things you might want, and are quite difficult to add yourself:

I like having a board with many (at least 8) SPST switches and LEDs, and momentary buttons. Unlike a microcontroller where it"s relatively easy to spit debug information out of a serial port or to an LCD with a single C function call, debugging FPGA designs is a bit harder. LEDs provide a zero fuss way to break out internal signals for visualisation - if you"re tracking the progress of a complex state machine, you can light up an LED when it gets to a certain point without adding any extra logic. While these are easy enough to add yourself, I find that it"s better to get a board that has them so that you don"t waste valuable user IOs or waste time investigating failures caused by your terrible soldering skills.

If you would like to connect high speed devices (above 10-20 MHz) to your FPGA, make sure your board has an interface connector that supports the speeds you"ll be using. Look for ground wires interspersed regularly between signal wires, high speed connectors (not just 0.1" headers), PCB trace length equalisation, and impedance control. Few of the cheap boards bother with any of these.

A long-standing complaint with vendor FPGA design tools is that they are generally enormous, complicated, slow, buggy, closed source, and are either expensive or have annoying license requirements. The open source community has made great progress in recent years to reimplement parts or all of the FPGA design toolchain and to address all of these concerns.

Tim "mithro" Ansell has an open offer to send FPGA hardware to anyone who has time to contribute to open source FPGA projects but doesn"t have any hardware.

$56Zynq 7010512MB DDR3, micro SD slot, 100 Mbit Ethernet, two LEDs, 62 length-matched and paired FPGA I/Os and 15 processor I/Os. Some documentation is available at QMTech"s site and there are some observations in this EEVBlog thread, where there are some complaints about a lack of decoupling.

$159/$179Zynq 7010/ 70201GB DDR, 16MB flash, TF socket, gigabit Ethernet, CAN, USB2.0 OTG, USB-UART, HDMI output, 90 or 106 user I/Os (with 39 LVDS pairs), accelerometer and temperature sensor, JTAG, two buttons, 4 switches, four LEDs, and a buzzer. An "IO Cape" breakout board ($35) provides three Pmod connectors, camera and LCD connectors, and 0.1" header I/O pins.

$214Zynq 7010512MB, 128 Mb flash, micro SD, gigabit Ethernet, 802.11/b/g/n WiFi and Bluetooth 4.2/LE, USB for JTAG, UART, and OTG, HDMI Tx/Rx, VGA, stereo audio output, light and temperature sensors, 4*7 Seg LEDs, 5 LEDs, 4 slide switches, 31 PL I/Os and 4 PS I/Os. A 2x16 LCD module is included, and camera and TFT LCD modules are available.

$79Artix 35T4 switches, 5 buttons, 7 LEDs, JTAG 256MB DDR3, 16MB flash, Arduino shield connector, one PMOD, and some sort of high speed connector which supports expansion boards with HDMI and VGA. Larger FPGA sizes will apparently be available too.

$149Artix 200TA PCIe x4 gen 2 development board with an NVMe (2280 Key M) connector. It has 1GB DDR3, 256 Mb flash, 1 LED, and 12 I/Os (including four LVDS pairs). This is the same form factor as the LiteFury, with larger FPGA and memory.

$149Artix 50T128 Mb flash, 2Gb DDR, USB and JTAG programming interfaces, gigabit Ethernet, HDMI input and output, GTP interface, micro SD, 3x7 segement segment displays, 6 buttons, 8 DIP switches, and 80 I/Os (40 length-matched differential pairs).

$149Artix 35TUSB-UART, 12-bit VGA output, USB HID host, 16 switches, 16 LEDs, 5 buttons, a 4-digit 7-segment display, 4 PMODs with XADC inputs on one of them. A device-locked Vivado Design Edition is available for $10.

$320, $159 academicArtix 100TPushing the limits of "cheap" unless you qualify for academic pricing, but attractive if you need the larger FPGA. Includes 5 PMOD connectors (40 low speed I/Os), 128MB DDR RAM, 16MB flash, 10/100 Ethernet, USB HID host, SD card, VGA, accelerometer, microphone, audio out, 16 switches, 16 LEDs, 8 7-segment displays, 5 buttons. The Artix"s internal ADC is available on one of the ports.

$165Artix 35TA full-featured development board with 32MB SDRAM, SPI flash, USB-JTAG and USB-UART, 802.11 b/g/n via an ESP-12F module, BLE, 12-bit VGA, HDMI out, 4 ADC channels, temperature and light sensors, 12-bit DAC, 2x16 LCD, 4x7 segment display, Micro SD, 16 SPDT switches, 5 buttons, 16 LEDs, a buzzer, and 31 I/Os. Compatible SPI TFT display and CMOS camera modules are also available.

$69XC7S50An educational platform with an associated digital logic course. It features HDMI output, ADC, four servo controllers, 8-digit 7-segment display, 4 SPST buttons, 16 switches, 16 LEDs and 2 RGB LEDs, 4 PMODs, PWM audio output, USB programming/UART, and BLE ($10 extra)

$137XC7S15A development board with an array of onboard peripherals. It features 802.11 b/g/n WiFi and Bluetooth 4/BLE, VGA output, 8-channel ADC, DAC, temperature and light sensors, USB-UART and USB-JTAG, 2x16 LCD, 4 7-segment displays, 16 slide switches, 5 SPST buttons, a buzzer, 16 LEDs, and 26 I/Os.

$34 deliveredLX9A "no name" board apparently available only on eBay. It has a Spartan-6 LX9, 4-digit 7 segment display, RS232 interface, 12-bit VGA, PS2, 8 LEDs, 3 buttons, 8-bit DIP switch, two PMOD interfaces, 26 digital I/Os, JTAG and SPI flash.

$89-258LX9/LX16A slightly baffling array of FPGA boards. Two that caught my eye were the 5I25, which is a PCI card with a Spartan-6 LX9 for $89 and the 6I25 (PCI Express) for $109.

₹ 8,500 ($132)LX9A development board with 8MB SPI flash, USB JTAG programmer, USB UART, WiFi, Bluetooth, VGA, 8-channel 12-bit ADC, 12-bit DAC, temperature sensor, LDR, 2x16 LCD, 4*7 segment display, buzzer, 16 SPST switches, 16 LEDs, 5 buttons, and external CMOS camera and TFT display modules.

$30.00100EA controller board with 8 LEDs, three SPST buttons, 35 I/Os, and USB programmer. It forms the foundation of a robotics and automation ecosystem, supporting up to nine simultaneous peripherals sold by the same manufacturer, complete with an FPGA code generation tool and Linux API.

$3050AA board with a 16Mbit of SPI flash, 8 LEDs, 6 SPST switches, 8 DIP switches, 3 7-segment displays, VGA and stereo audio output, 39 I/Os (including four PMOD connectors), and USB JTAG.

$53200AAn Arduino shield that is intended to be an audio and video coprocessor for Arduino applications, but could be repurposed as a general-purpose FPGA interface board with the Arduino form factor. VGA and audio outputs, with SPI flash.

$24ICE40UP5KA revised version of the original UPDuino with non-EOL parts, a stronger connector, and improved signal integrity. It also provides 32 I/Os, 4MB SPI flash with support for qSPI, RGB LED, USB programmer, an open source design, and compatibility with the tinyFPGA bootloader.

$60ICE40 HX1K4 LEDs, 2 SPST buttons, two 7-segment LED displays, micro USB for programming and USB-UART, VGA, and a PMOD I/O connector. It is designed to be used in conjunction with the tutorials available at nandland.

90 EURiCE40Currently taking pre-orders. It provides an FPGA supported by the open source Lattice synthesis toolchain and 200 I/Os (via PMOD and flat flex connectors). It is designed to be connected to a Raspberry Pi 2B / B+.

$115/$155ECP5 12F/45F/85FAn open hardware design with many code examples and projects. It has 56 I/Os (28 differential pairs), 32 MB SDRAM, SPI flash, micro SD, 8 user LEDs, 7 buttons, audio, composite and digital video output, ESP32 for WiFI and Bluetooth, FM/ASK receiver (and transmitter?), 8-channel 12-bit ADC, RTC, USB-serial, and USB-to-FPGA.

$262LFE3-35EAVery occasionally reduced to $99 on special, but still one of the cheaper PCI-Express (x1) development boards with 64-Mbit flash, 1 Gbit DDR3, four SMA connectors (one full-duplex SERDES channel), dual gigabit Ethernet, expansion connectors, 14-segment alpha-numeric display, switches and LEDs, and USB programmer. It appears that the FPGA device requires a licensed version of the design software, but this is also available for $99 for the first year. Pricing options beyond the first year are not very clear.

$61M2S010A small FPGA module with integrated 166 MHz ARM Cortex-M3, 8 MB SDRAM, 8 MB QSPI Flash, JTAG and UART over USB, 3 pin header for Live Probe, 9 LEDs, 1 button, one PMOD, and a total of 31 I/Os.

$71-$123M2S005-M2S090A module with an integrated 166 MHz 32-bit ARM Cortex-M3. On board are 64 MB RAM, 16 MB flash, and 10/100 Ethernet. Also available is a $179 Starter Kit, which includes an FPGA module as well as USB/Ethernet connectors and a prototyping area.

$99A2F200M3FIntegrated 100 MHz ARM Cortex-M3, 10/100 Ethernet PHY and on-chip MAC, USB-serial, on-board USB programming interface, OLED display, 8 LEDs, two user switches, and an indeterminate number of analog and digital outputs. It looks like a very interesting and inexpensive board for developing mixed FPGA/microcontroller applications.

$5910CL006A board intended for study purposes. It includes USB-serial and USB programming, 8 DIP switches, 6 7-segment displays, 8 LEDs, thermistor, potentiometer, photoresistor, 4 buttons, VGA, AD/DA, gigabit Ethernet, and two PMOD connectors.

$1795CGTFD9EPacks 4 Gb DDR RAM, 4 Mb SRAM, high speed mezzanine connector with four 3.125 Gbps transceivers, 40 GPIOs, Arduino-compatible header with analog inputs, configuration flash, USB programmer, HDMI output, audio, 18 LEDs, 10 slide switches, 4 debounced buttons, CPU reset button, 4 seven segment displays, micro SD socket, and USB UART.

$199, $150 academic5CSEMA5FContains an integrated dual core ARM Cortex-A9. The board has 64 MB SDRAM, 1GB DDR3, micro SD, dual USB 2.0 host, gigabit Ethernet, PS/2, IR emitter and receiver, around 80 digital I/Os, 8 * 12-bit 1MSPS ADC inputs, VGA, audio codec, analog TV video input, four buttons, 10 switches, 11 LEDs, 6 * 7-seg displays, accelerometer, USB-serial, and USB programmer.

$119, 81 academic3C168Mbyte SDRAM, 4 Mbyte flash, SD card socket, USB programmer, 3 buttons, 10 switches, 10 LEDs, 4 seven-segment displays, 16x2 LCD interface, VGA output, RS232 and PS/2 interfaces, and 72 I/Os.

$28-77Cyclone IIA range of cheap boards from Shenzhen, most with RAM and a variety of I/O including LCDs, 7-segment LEDs, VGA, switches, etc. Again they"re great value if you already have some experience with FPGAs, are comfortable reading schematics and don"t require any vendor support.

$7510M08A MAX 10 board that is a drop-in replacement for an Arduino Uno, and comes with FPGA-accelerated hardware components that can be used from Arduino sketches. It features 5V I/Os, Arduino-compatible ADCs, and USB-serial.

$110Cyclone IIContains an FT2232H USB interface chip to provide high speed data transfer. It has a total of 80 to 96 I/Os (split between the FPGA and FT2232H, and depending on who you ask) with a 0.1" spacing.

Some interesting and less well known FPGA vendors. Take the time to listen to the very interesting interview with Efinix CEO Sammy Cheung on The Amp Hour.

$5.90GOWIN GW1N-1-LVA very low cost board with 1152 LUT4s. It has a RGB LCD driver (supporting 800x480) and FPC connector, 8MB PSRAM, 34 I/O, RGB LED, and USB-C for power supply and programming.

$17.90Anlogic EG4S201 MB flash, 64 Mbit SRAM, RGB LED, TF card socket, FPC sockets for LCD or VGA adaptors and camera or ADC, resistive touch screen controller, USB-JTAG, and 72 I/Os.

KNJN Pluto ($29-$129) a range of small boards with various FPGAs. No on-board peripherals, so they seem more suited to dropping in to a larger project than as a standalone development tool.

If you manufacture or know of any other cheap FPGA development boards, please let me know so that I can include them on this list. Review units will be cheerfully accepted! :)

There is a long and comprehensive list of boards at FPGA-FAQ that includes a couple of other cheap options - there are a number of Spartan-3 generation boards that I haven"t listed.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey