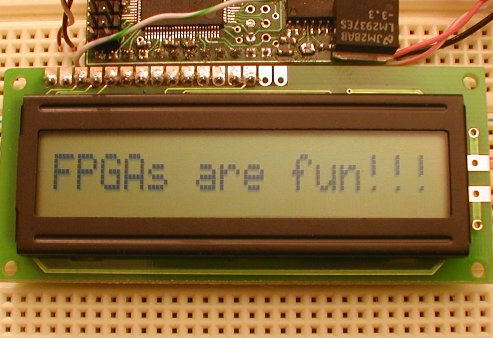

fpga lcd display quotation

Is any one having the datasheet of 16x2 lcd shipped from terasic. I bought the lcd with de1 but I did not get any manuals or datasheet. Can any one tell me how to interface or is there a datasheet available?:confused:

ELBERT V2 is a simple but versatile FPGA Learning/Development board featuring Xilinx Spartan 3A FPGA. An excellent choice for beginners and advanced learners for experimenting and learning system design with FPGAs. This development board features Xilinx XC3S50A 144 pin FPGA with a maximum of 108 user IOs (Some IOs are dedicated to system and peripherals). USB interface provides a fast and easy configuration download to the onboard SPI flash. You don’t need a programmer or special downloader cable to download bitstream to Elbert. ELBERT V2 features a stable clock source that is derived from the onboard configuration controller. ELBERT V2 incorporates LEDs, switches, and other peripherals for curious users to get started with the “Hello World” program in a matter of minutes.

Please review our latest addition to the FPGA family Narvi Spartan 7 FPGA Module featuring Xilinx’s Spartan-7 FPGA which can be the solution to develop and prototype applications.

This application note describes the interfacing of Ampire AM-800480STMQW-TA1 display to BoraEVB and BoraXEVB. Main characteristics of this 7" TFT LCD panel are:

To interface the display a small adapter board is needed. It interfaces J22 connector on BoraEVB side and provides a 20-pin connector to directly attach display cable.

is also equipped with a linear regulator generating 2.5V. This voltage is used as power supply for the VDDIO_BANK13 rail. This voltage is required to implement LVDS differential pairs that drive display.

integrates a pad (denoted as TP1) that is used to connect 5V power supply generated by MOD2 PSU of BoraEVB. This additional power rails is required by display backlight circuitry.

In case of BoraXEVB, no adapter board is needed. LCD panel is directly connected to J26 connector where PL bank 13"s signals implementing LVDS interface are routed (see page 14 of the schematics). I/O voltage of bank 13 is set to 2.5V by configuring JP25 as shown in the following table.

To implement frame buffer, a portion of main SDRAM is used. This area is allocated at runtime by linux frame buffer driver. Even if LCD is 18 bpp, each pixel is represented by 32-bit word in memory. In fact each pixel is in RGB666 format, so for each colour only the six most significant bits of the frame buffer RGB888 are used to drive the display.

(*) This signal is used to control backlight. It is usually driven by a PWM signal whose duty cycle is proportional to backlight intensity. For the sake of simplicity, in this project this signal is driven by a GPIO, thus only two intensity levels are supported (0% and 100%). This is a CMOS 2.5V level signal. Make sure that voltage levels of this signal are compatible with LCD backlight input.

(*) This signal is used to control backlight. It is usually driven by a PWM signal whose duty cycle is proportional to backlight intensity. For the sake of simplicity, in this project this signal is driven by a GPIO, thus only two intensity levels are supported (0% and 100%). This is a CMOS 2.5V level signal. Make sure that voltage levels of this signal are compatible with LCD backlight input.

Why should it damage the board? On each GPIO are two different VCC"s: VCC_SYS and VCC3P3. According to the user manual (http://www.terasic.com.tw/cgi-bin/page/archive_download.pl?language=english&no=593&fid=75023fa36c9bf...) VCC_SYS is 5V and VCC3P3 is 3.3V. But I can"t get voltages beyond 3.3V for the pins. So I need to change the voltage for the LCD to 3.3V and the voltage of the pins to 2.5V, right?

In between of these you will see a small green connector board, which is our own 7-inch LCD Breakout board with the required switch-mode power supply for powering the LED backlight, together with the interface connector with the 18-bit color signals, Pixel Clock, Data Enable and PWM.

In the datasheet of the display you will be able to find the specific timing parameters of these signals, which also explains when to display the color data of each pixel.

At page 6 of the datasheet of our display we can see the timing table. From this table we will notice the required CLK frequency of around 33.26MHz. Generating this Pixel clock source is one of the major aspects of generating the video signal.

Within the code for the FPGA I have decided to use the built in DCM (Digital Clock Manager) periphiral of the FPGA’s, to generate 33.33MHz from the on board 50MHz oscillator. This is done by diving the Input frequency by 27 and then multiply this by 18.

Now when we have this clock signal internally in the FPGA too, we can use this signal to count the clock pulses, equal to each ‘pixel’, and then we are ready to create the timing of the DE signal.

When we have done a single line scan there is 479 more to go within the visisble display area. Yet again we do also have some ‘off-screen’ lines, in this case between 10 and 110 lines, to do the sync.

The Hcount is used to take care of the current Horizontal pixel, going from 0 to 799 when inside the visible display area, and then continuing from 799 to about 1200 for the ‘off-screen’ pixels.

The Vcount is used to take care of the current Vertical pixel, going from 0 to 479 when inside the visible display area, and then continuing from 479 to about 590 for the ‘off-screen’ pixels.

Finally it is now just a matter of setting the 18-bit digital color lines to the proper pixel color at each clock cycle and then we have a functioning display system.

The Terasic Multi-touch LCD Module (MTL) is an all-purpose capacitive touch-screen for FPGA applications and provides multi-touch gesture and single-touch support. An IDE cable with an IDE to GPIO adapter (ITG) is used to interface with various Terasic FPGA development boards through a 2x20 GPIO interface on the MTL.

This article covers FPGA projects from beginners to expert level. You can find hereFPGA projects for engineering students, cool FPGA projects and FPGA projects used in commercial products. All FPGA projects are with free and downloadable source code, allowing you to use the projects at home or at work. Our goal is to help users understand FPGA’s role in the industry and how FPGAs are used to implement various functions in an electronic products.

The first FPGA project on the list is a standard spread spectrum system is of the “direct sequence” or “frequency hopping” type, or else some combination of these two “hybrids”. In frequency Hopping, the system” hops” from frequency to frequency over a wide band. The pattern in which frequencies are engaged is a role of a code sequence, and the rate of hopping from one frequency to another frequency is a function of the data rate.

This FPGA project aims to design, simulate and develop a transmitter and a receiver for frequency hopped system on FPGA using VHDL. This project’s completion covers the art of secure digital communications that is now being exploited for commercial, industrial and military purposes.

Canny edge detection is a multi-stage algorithm for vision processing that generates a binary output image (edge or no edge for complex vision algorithms such as number plate identification). Detection of Canny edges can eliminate irrelevant image information and provide a clear binary output for each pixel. High-performance computing is traditionally implemented by Canny edge detection. However, you can now implement vision algorithms for low-power mobile applications on embedded platforms. Multiple processing stages include vision algorithms such as Canny. Usually, processors have to fetch, process, and write the input image frame from external memory back to external memory. For the next processing block, the processor repeats this process. This conventional shuffling of memory among blocks is inefficient: In this FPGA project, we have implemented the Canny edge detector with a 9×9 mask. Able to produce 1 pixel-per-clock-cycle. We have successfully implemented on a Virtex4 up to 400Mhz clock frequency. The purpose of this project is to detect the sharp edges from the images.

Direct digital synthesis (DDS) produces an analogue waveform, typically a sinusoidal wave, by generating a digital time-varying signal and then making a digital-to-analogue conversion. Since operations are predominantly digital inside a DDS system, it can offer fast switching between output frequencies, satisfactory frequency resolution, and operation over a wide range of frequencies. Several frequency generation possibilities are available to a designer, ranging from phase-locked-loop (PLL)-based very high-frequency synthesis techniques to dynamic digital-to-analogue converter (DAC) output programming to produce arbitrary waveforms at lower frequencies. But in both communications and industrial applications, the DDS approach is rapidly gaining acceptance for solving frequency (or waveform) generation requirements, since single-chip IC devices can produce programmable analogue output waveforms only and with high resolution and accuracy. In this FPGA project, we have implemented the high-precision Direct Digital Frequency Synthesizer (DDFS) used in digital up/down conversion, and the generation of periodic waveforms. For example, sine wave, cosine wave, square and sawtooth waves. The output is 16-bit signed data samples. This project is ideal for the quadrature signal generation, digital modulation/demodulation and software radio applications. Also, it can be used as oscillators and generation of complex quadrature signals.

A cryptographic hash function is a hashing algorithm. It is a mathematical algorithm that maps arbitrary-size information to a fixed-size hash. In IT, cryptographic hash functions are used commonly. We may use them for digital signatures, authentication codes for messages (MACs) and other authentication types. We can also use them for indexing data in hash tables, for fingerprinting, identifying files, detecting duplicates or as checksums (we can perceive if a sent file didn’t suffer accidental or intentional data corruption). The algorithm for a hash function is designed to be a one-way function that cannot be reversed. Multiple hashing algorithms have, however, been corrupted in recent years. This FPGA project aims to provide the FPGA implementation of the hashing algorithms to generate the hashes for the Proof-of-Work (Pow). In this project, we have developed the Blockchain system to mine the 0xbitcoin. We have used the CVP 13 FPGA board and implement the Keccak-256 algorithm on it. We have achieved the 500 Giga hashes per second.

High-performance digital electronic circuits for onboard processing of return signals in airborne precipitation – radar measurement devices in commercially available fields have been developed – programmable gate arrays (FPGAs). Previously, it was common practice to downlink the radar-return data to a post-processing ground station – an expensive practice that eliminates the near-real-time use of automated targeting data. In theory, a system of about 20 personal computer-type microprocessors could perform onboard processing; compared to such a system, the current FPGA-based processor is much smaller and consumes much less power. Alternatively, an application-specific integrated circuit (ASIC) may be used for onboard processing. However, compared to an ASIC implementation, the current FPGA implementation provides the advantages of (1) greater versatility for research applications such as the current one and (2) lower costs in the limited production volumes typical of research applications. Implementing the radar signal processing techniques on the FPGA is the significant domain. In this FPGA project, we have selected a few algorithms in the FPGA. Implement the Radar Equation along with the pulse compression algorithm, Implement Doppler shift to detect target velocity, and implement pulse-Doppler waveforms.

Implement a constant false alarm rate (CFAR) detection adaptive algorithm on FPGA used in radar systems to detect target signal against a background of noise, clutter and interference. Aim of this project to detect the target from a noisy condition.

The Fast Fourier Transform (FFT) is a fundamental building block used in DSP systems, with applications ranging from Digital MODEMs based on OFDM to algorithms for Ultrasound, RADAR and CT image reconstruction. Although its algorithm is straightforward to understand, for hardware engineers today, the implementation architectures and details’ variants are essential and are an enormous time sink. In this FPGA project, we have implemented the Fast Fourier Transform on the FPGA; we have used the butterfly technique to implement it on the FPGA. The FFT is used to perform the find the frequency component in a complex signals plan. It’s a 4096-point FFT. With device-level fixed point C-models, this FFT project core offers four different architectures and reduces the average implementation time from 3-6 months to the push of a button. It also gives users the opportunity to make complex trade-offs needed by both the DSP algorithm and hardware engineers for all the appropriate algorithms and implementation. The FFT project emphasizes increased dynamic range by growing the support for data and phase factor width up to 34 bits and supporting IEEE single accuracy floating-point data form. By using a higher precision fixed-point FFT internally to achieve comparable noise efficiency.

A Digital Decoder IC is a device that transforms one digital format into another, and the Binary Coded Decimal (BCD) to 7-Segment Display Decoder is one of the most widely used devices for doing this. 7-segment LED (Light Emitting Diode) or LCD (Liquid Crystal Display) style displays offer a very convenient way for numbers, letters or even alpha-numerical characters to display information or digital data. Usually, 7-segment displays consist of seven individual-coloured LEDs (called segments). The correct combination of LED segments needs to be illuminated on display to generate the necessary numbers or HEX characters from 0 to 9 and A to F, correspondingly, and BCD to 7-segment display decoders 74LS47 do just that. A Seven-Segment Display is an indicator widely used to show details to the consumer by FPGA designers. In VHDL code to convert from binary to compatible seven-segment display can be done quickly. Several applications may need one or more seven-segment displays to be used, i.e., counter, stopwatch, current measurement. In this cool FPGA project, we have BCD to 7-segment display decoder. The VHDL entity takes 4-bit BCD as an input and outputs the 7-bit decoded output for driving the display unit. A seven-segment display is being used to display decimal digits. They have LED elements which become active when the input is zero.

The digital clock’s primary purpose is to use the 7-segment panel on the Artix-7 FPGA Board to digitally display the time. By default, the digital clock shows the runtime and the time can be adjusted using the time set allocated to the onboard switch. The alarm role is also configured using the alarm set and the alarm on the kit’s switch. The developed digital clock is a format designed for 24 clocks. For the hardware implementation of the digital clock, this project uses FPGA. The clock starts as soon as the FPGA is turned on. The FPGA and onboard clock will produce the Timing signals. You can set the clock time and the alarm time using the dip switches on the board. Using digital operations: counting, comparing, increasing and decreasing, the suggested digital clock design is improved. Using the time set switch, the clock time can be set, and the alarm time can be set using the alarm set switch. If the clock is equal to the alarm time, the alarm will be on. By using the push buttons on the monitor, minutes and hours can be increased and decremented. In this FPGA project, we have implemented the Digital clock on FPGA. The module has one input “the source clock of the FPGA” and has 3 outputs (hour hand, minute hand, and second hand). We have displayed the output on the Seven Segment Display of the Artix-7 FPGA.

Compression of image processing images can enhance the Device efficiency by minimizing cost and time to minimize without a significant reduction, image storage, and transmission of the picture’s quality. It is possible to describe a monochrome picture with each pixel over a matrix of picture elements (pixels), Described by the grayscale value of 8 bits. This depiction of Image data might require significant storage requirements. Compression of the image aims to decrease the size of the representation and, at the same time, to preserve much of the representation. It can be lossy or lossless compression. Compression with Lossy gives Compared to lossless, a higher reduction in data volume Compression; but just an approximation of the initial compression. It is possible to recreate the image. There are many norms for compression of images and Like Joint Photographic Experts Decompression (CODEC) Team, Format for Graphics Interchange (GIF), Portable Network Graphics (PNG), Picture Labeling Format of File (TIFF). The most commonly used JPEG compression. The type of lossy image compression used and based on the Discrete transform of cosine (DCT). Depending on the details found inside the image and the image, a compressed image in JPEG format may be approximately 10 percent of compression’s original size efficiency. The results in a reduction of 90 percent in the Bandwidth needed. This FPGA project includes a complete JPEG Hardware with 4:1:1 subsampling, able to compress at a rate of up to 42 images per second at the maximum resolution (256×256 @ 60 MHz). The FPGA input is RGB input (row-wise) and outputs to memory the compressed JPEG image.

We built a simple FM receiver on the FPGA that demodulated the FM modulated frequency signal. We have used the dipole antenna to receive the FM signals then used the FM demodulator logic to demodulate the received signal. First, we used the ADC to convert the analogue FM signal to the digital and then process it digitally to remove the carrier waves to get an only pure sound wave from the broadcast station.

In physics, the square root function sqrt(x) is an essential elementary function—Digital signal and image processing, ANN equations. The Field Programmable Gate Arrays (FPGAs) are currently being extended to solve the problem. Problems where the calculations of the function sqrt(x) are necessary. The FPGA manufacturers and third-party companies are proposing various IP cores of sqrt calculation (x). But these IP cores were developed decades ago and typically did not take the characteristics of the latest generations of FPGA into account. They do need upgrades, therefore. An enhanced feature algorithm to calculate sqrt (x) is suggested in this FPGA project, which fits the FPGA implementation I have written a code for finding the square root of a signed number on FPGA using VHDL as a programming interface. The code is based on “Non-Restoring Square Root algorithm”. The code takes one signed number, 32 bit in size and returns the square root, which is also of signed type with 16-bit size. The modified algorithm, CORDIC-like, for It is proposed to derive the square root equation. The algorithm is separated by the reduced sum of Steps proportional to the data given, and the outcome is Width of bits. In VHDL, the algorithm is defined and is Built to enforce the FPGA. This is the most Efficient at the floating-point throughout its implementation Module Square Root.

The detection of errors decides if the data obtained via a medium is Corrupted while transmitting. To achieve this, the transmitter uses a feature to measure and append the checksum value for the data Checksum for the original frame of data. To create a checksum for the received data frame, the receiver uses the same calculation technique and compares the received checksum to the transmitted checksum. If the two checksum values are identical, the data frame obtained is right, and there was no data corruption during transmission or storage. In this FPGA project, we have developed the CRC on FPGA to detect the error in the transmission message. The advantage of the CRC circuit generated is that the input is assumed to be serially fed into the circuit. Meaning, the input can be long and still the FPGA resource usage will remain the same.

A ring counter is a kind of counter made up of flip-flops connected to a shift register, with the last flip-flop output fed to the first one’s input, forming a “circular” or “ring” structure. In hardware design (e.g., ASIC and FPGA design), ring counters are also used for constructing finite-state machines. A binary counter will require an adder circuit that is considerably more complicated than a ring counter and has a more significant propagation delay as the number of bits increases, whereas a ring counter’s propagation delay would be almost constant regardless of the code’s number of bits. In this FPGA project, a ring counter is implemented on the FPGA, consisting of a series of flip flops connected positively. The circuit is an especial type of shift register where the last flip-flop’s output is feedback to the first flip-flop input.

Increased demand for data security is an undeniable fact. To achieve higher security, cryptographic algorithms play an essential role in protecting data from unapproved usage. In this FPGA project, we present a cryptoprocessor using Advanced Encryption Standard (AES). The AES is integrated with a 32-bit general-purpose 5- stage pipelined MIPS processor. The integrated AES module is a fully pipelined module which follows the inner round and outer round pipeline design. The results show that the presented pipeline version of the AES algorithm and the MIPS processor outperform traditional methods. At the operating frequency of 553 MHz, the proposed design can achieve the throughput of 58 Gbps, the latency of 240 ns, and the minimum power consumption of 76 MW.

Instead of reading and writing to individual addresses, an SPI is a good option for communicating with low-speed computers that are accessed intermittently and transfer data streams. An SPI is an excellent option if we can take advantage of its full-duplex capability to send and receive data simultaneously. In VHDL, this design is implemented. The Lattice iCECube2TM Position and Route tool integrated with the Synplify Pro synthesis tool is used for the design execution. The architecture uses an ultra-low-density FPGA iCE40TM and can be targeted to other members of the iCE40 family.

CRTs can be abundant if you have good places in your local community to look, but they are getting trickier to track down each passing year. And while nothing’s stopping you from using a modern LCD for retro gaming, you may want to track down a square-shaped LCD (mostly 4:3 aspect ratio) so your classic content seems a bit more “at home” — avoiding those black bars.

So whether you’re looking for a cheap 4:3 LCD to use with your MiSTER FPGA setup, have a classic personal computer, or just want something for watching “full screen” video content or a emulation box to run on, I’m hoping this guide is helpful in your shopping.

Granted LCDs, especially older models, aren’t ideal for retro gaming compared to CRTs. LCDs often down’t have as deep of black colors and there is input lag involved among some other issues.

However, LCDs are easier to move around and store and use less electricity. And even though there are many die-hard CRT fans out there, there are also many long-time retro fans that have been using the recommended monitors below for a while and been happy with their performance. I’ve even quoted and handful of enthusiasts to give you a good perspective on these recommendations. And don’t forget, eventually LCDs might be much easier to find and purchase remotely then the CRTs counterparts.

Early LCD monitors may show a lack of technical maturity, however, near some of the later ones that we are focusing on have some decent IPS technology with reasonable color and response times.

In the end, I thought this would be a fun, lighthearted look at some options for those that are interested. If you have any commentary on the matter, please share your thoughts and suggestions in the comments section below. Just be respectful — not looking for CRT vs LCD wars

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey