thin-film transistor tft display factory

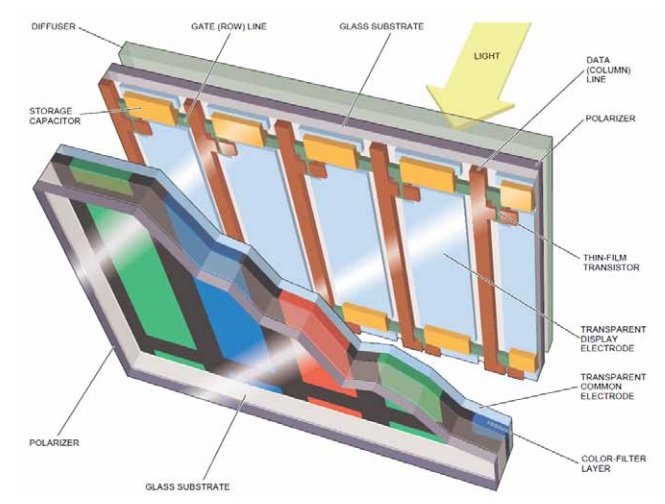

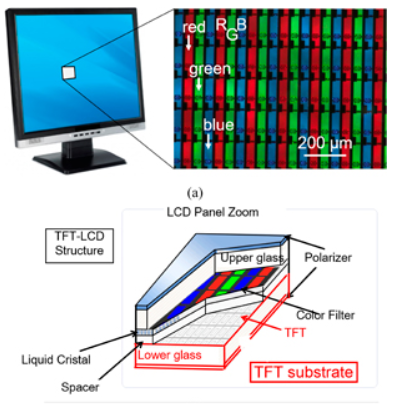

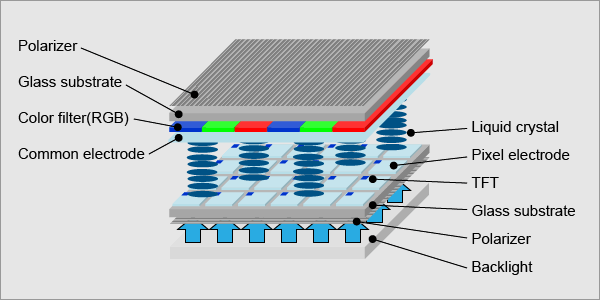

A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display that uses thin-film-transistor technologyactive matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven (i.e. with segments directly connected to electronics outside the LCD) LCDs with a few segments.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968. In 1971, Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated a 2-by-18 matrix display driven by a hybrid circuit using the dynamic scattering mode of LCDs.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).active-matrix liquid-crystal display (AM LCD) using CdSe TFTs in 1974, and then Brody coined the term "active matrix" in 1975.high-resolution and high-quality electronic visual display devices use TFT-based active matrix displays.

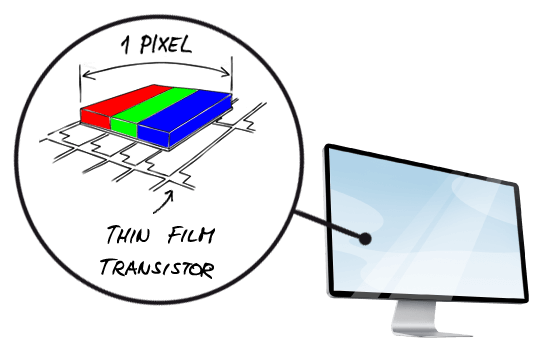

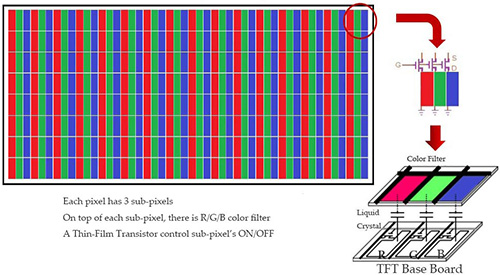

The liquid crystal displays used in calculators and other devices with similarly simple displays have direct-driven image elements, and therefore a voltage can be easily applied across just one segment of these types of displays without interfering with the other segments. This would be impractical for a large display, because it would have a large number of (color) picture elements (pixels), and thus it would require millions of connections, both top and bottom for each one of the three colors (red, green and blue) of every pixel. To avoid this issue, the pixels are addressed in rows and columns, reducing the connection count from millions down to thousands. The column and row wires attach to transistor switches, one for each pixel. The one-way current passing characteristic of the transistor prevents the charge that is being applied to each pixel from being drained between refreshes to a display"s image. Each pixel is a small capacitor with a layer of insulating liquid crystal sandwiched between transparent conductive ITO layers.

The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. However, rather than fabricating the transistors from silicon, that is formed into a crystalline silicon wafer, they are made from a thin film of amorphous silicon that is deposited on a glass panel. The silicon layer for TFT-LCDs is typically deposited using the PECVD process.

Polycrystalline silicon is sometimes used in displays requiring higher TFT performance. Examples include small high-resolution displays such as those found in projectors or viewfinders. Amorphous silicon-based TFTs are by far the most common, due to their lower production cost, whereas polycrystalline silicon TFTs are more costly and much more difficult to produce.

The twisted nematic display is one of the oldest and frequently cheapest kind of LCD display technologies available. TN displays benefit from fast pixel response times and less smearing than other LCD display technology, but suffer from poor color reproduction and limited viewing angles, especially in the vertical direction. Colors will shift, potentially to the point of completely inverting, when viewed at an angle that is not perpendicular to the display. Modern, high end consumer products have developed methods to overcome the technology"s shortcomings, such as RTC (Response Time Compensation / Overdrive) technologies. Modern TN displays can look significantly better than older TN displays from decades earlier, but overall TN has inferior viewing angles and poor color in comparison to other technology.

Most TN panels can represent colors using only six bits per RGB channel, or 18 bit in total, and are unable to display the 16.7 million color shades (24-bit truecolor) that are available using 24-bit color. Instead, these panels display interpolated 24-bit color using a dithering method that combines adjacent pixels to simulate the desired shade. They can also use a form of temporal dithering called Frame Rate Control (FRC), which cycles between different shades with each new frame to simulate an intermediate shade. Such 18 bit panels with dithering are sometimes advertised as having "16.2 million colors". These color simulation methods are noticeable to many people and highly bothersome to some.gamut (often referred to as a percentage of the NTSC 1953 color gamut) are also due to backlighting technology. It is not uncommon for older displays to range from 10% to 26% of the NTSC color gamut, whereas other kind of displays, utilizing more complicated CCFL or LED phosphor formulations or RGB LED backlights, may extend past 100% of the NTSC color gamut, a difference quite perceivable by the human eye.

In 2004, Hydis Technologies Co., Ltd licensed its AFFS patent to Japan"s Hitachi Displays. Hitachi is using AFFS to manufacture high end panels in their product line. In 2006, Hydis also licensed its AFFS to Sanyo Epson Imaging Devices Corporation.

A technology developed by Samsung is Super PLS, which bears similarities to IPS panels, has wider viewing angles, better image quality, increased brightness, and lower production costs. PLS technology debuted in the PC display market with the release of the Samsung S27A850 and S24A850 monitors in September 2011.

TFT dual-transistor pixel or cell technology is a reflective-display technology for use in very-low-power-consumption applications such as electronic shelf labels (ESL), digital watches, or metering. DTP involves adding a secondary transistor gate in the single TFT cell to maintain the display of a pixel during a period of 1s without loss of image or without degrading the TFT transistors over time. By slowing the refresh rate of the standard frequency from 60 Hz to 1 Hz, DTP claims to increase the power efficiency by multiple orders of magnitude.

Due to the very high cost of building TFT factories, there are few major OEM panel vendors for large display panels. The glass panel suppliers are as follows:

External consumer display devices like a TFT LCD feature one or more analog VGA, DVI, HDMI, or DisplayPort interface, with many featuring a selection of these interfaces. Inside external display devices there is a controller board that will convert the video signal using color mapping and image scaling usually employing the discrete cosine transform (DCT) in order to convert any video source like CVBS, VGA, DVI, HDMI, etc. into digital RGB at the native resolution of the display panel. In a laptop the graphics chip will directly produce a signal suitable for connection to the built-in TFT display. A control mechanism for the backlight is usually included on the same controller board.

The low level interface of STN, DSTN, or TFT display panels use either single ended TTL 5 V signal for older displays or TTL 3.3 V for slightly newer displays that transmits the pixel clock, horizontal sync, vertical sync, digital red, digital green, digital blue in parallel. Some models (for example the AT070TN92) also feature input/display enable, horizontal scan direction and vertical scan direction signals.

New and large (>15") TFT displays often use LVDS signaling that transmits the same contents as the parallel interface (Hsync, Vsync, RGB) but will put control and RGB bits into a number of serial transmission lines synchronized to a clock whose rate is equal to the pixel rate. LVDS transmits seven bits per clock per data line, with six bits being data and one bit used to signal if the other six bits need to be inverted in order to maintain DC balance. Low-cost TFT displays often have three data lines and therefore only directly support 18 bits per pixel. Upscale displays have four or five data lines to support 24 bits per pixel (truecolor) or 30 bits per pixel respectively. Panel manufacturers are slowly replacing LVDS with Internal DisplayPort and Embedded DisplayPort, which allow sixfold reduction of the number of differential pairs.

The bare display panel will only accept a digital video signal at the resolution determined by the panel pixel matrix designed at manufacture. Some screen panels will ignore the LSB bits of the color information to present a consistent interface (8 bit -> 6 bit/color x3).

With analogue signals like VGA, the display controller also needs to perform a high speed analog to digital conversion. With digital input signals like DVI or HDMI some simple reordering of the bits is needed before feeding it to the rescaler if the input resolution doesn"t match the display panel resolution.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

K. H. Lee; H. Y. Kim; K. H. Park; S. J. Jang; I. C. Park & J. Y. Lee (June 2006). "A Novel Outdoor Readability of Portable TFT-LCD with AFFS Technology". SID Symposium Digest of Technical Papers. AIP. 37 (1): 1079–82. doi:10.1889/1.2433159. S2CID 129569963.

Kim, Sae-Bom; Kim, Woong-Ki; Chounlamany, Vanseng; Seo, Jaehwan; Yoo, Jisu; Jo, Hun-Je; Jung, Jinho (15 August 2012). "Identification of multi-level toxicity of liquid crystal display wastewater toward Daphnia magna and Moina macrocopa". Journal of Hazardous Materials. Seoul, Korea; Laos, Lao. 227–228: 327–333. doi:10.1016/j.jhazmat.2012.05.059. PMID 22677053.

A thin-film transistor (TFT) is a special type of field-effect transistor (FET) where the transistor is thin relative to the plane of the device.substrate. A common substrate is glass, because the traditional application of TFTs is in liquid-crystal displays (LCDs). This differs from the conventional bulk metal oxide field effect transistor (MOSFET), where the semiconductor material typically is the substrate, such as a silicon wafer.

TFTs can be fabricated with a wide variety of semiconductor materials. Because it is naturally abundant and well understood, amorphous or polycrystalline silicon was historically used as the semiconductor layer. However, because of the low mobility of amorphous siliconcadmium selenide,metal oxides such as indium gallium zinc oxide (IGZO) or zinc oxide,organic semiconductors,carbon nanotubes,metal halide perovskites.

Because TFTs are grown on inert substrates, rather than on wafers, the semiconductor must be deposited in a dedicated process. A variety of techniques are used to deposit semiconductors in TFTs. These include chemical vapor deposition (CVD), atomic layer deposition (ALD), and sputtering. The semiconductor can also be deposited from solution,printing

Some wide band gap semiconductors, most notable metal oxides, are optically transparent.electrodes, such as indium tin oxide (ITO), some TFT devices can be designed to be completely optically transparent.head-up displays (such as on a car windshield).The first solution-processed TTFTs, based on zinc oxide, were reported in 2003 by researchers at Oregon State University.Universidade Nova de Lisboa has produced the world"s first completely transparent TFT at room temperature.

The best known application of thin-film transistors is in TFT LCDs, an implementation of liquid-crystal display technology. Transistors are embedded within the panel itself, reducing crosstalk between pixels and improving image stability.

As of 2008LCD TVs and monitors use this technology. TFT panels are frequently used in digital radiography applications in general radiography. A TFT is used in both direct and indirect capturemedical radiography.

The most beneficial aspect of TFT technology is its use of a separate transistor for each pixel on the display. Because each transistor is small, the amount of charge needed to control it is also small. This allows for very fast re-drawing of the display.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET in which germanium monoxide was used as a gate dielectric. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. In 1966, T.P. Brody and H.E. Kunig at Westinghouse Electric fabricated indium arsenide (InAs) MOS TFTs in both depletion and enhancement modes.

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard J. Lechner of RCA Laboratories in 1968.dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).electroluminescence (EL) in 1973, using CdSe.active-matrix liquid-crystal display (AM LCD) using CdSe in 1974, and then Brody coined the term "active matrix" in 1975.

A breakthrough in TFT research came with the development of the amorphous silicon (a-Si) TFT by P.G. le Comber, W.E. Spear and A. Ghaith at the University of Dundee in 1979. They reported the first functional TFT made from hydrogenated a-Si with a silicon nitride gate dielectric layer.research and development (R&D) of AM LCD panels based on a-Si TFTs in Japan.

By 1982, Pocket TVs based on AM LCD technology were developed in Japan.Fujitsu"s S. Kawai fabricated an a-Si dot-matrix display, and Canon"s Y. Okubo fabricated a-Si twisted nematic (TN) and guest-host LCD panels. In 1983, Toshiba"s K. Suzuki produced a-Si TFT arrays compatible with CMOS integrated circuits (ICs), Canon"s M. Sugata fabricated an a-Si color LCD panel, and a joint Sanyo and Sanritsu team including Mitsuhiro Yamasaki, S. Suhibuchi and Y. Sasaki fabricated a 3-inch a-SI color LCD TV.

The first commercial TFT-based AM LCD product was the 2.1-inch Epson ET-10Hitachi research team led by Akio Mimura demonstrated a low-temperature polycrystalline silicon (LTPS) process for fabricating n-channel TFTs on a silicon-on-insulator (SOI), at a relatively low temperature of 200°C.Hosiden research team led by T. Sunata in 1986 used a-Si TFTs to develop a 7-inch color AM LCD panel,Apple Computers.Sharp research team led by engineer T. Nagayasu used hydrogenated a-Si TFTs to demonstrate a 14-inch full-color LCD display,electronics industry that LCD would eventually replace cathode-ray tube (CRT) as the standard television display technology.notebook PCs.IBM Japan introduced a 12.1-inch color SVGA panel for the first commercial color laptop by IBM.

TFTs can also be made out of indium gallium zinc oxide (IGZO). TFT-LCDs with IGZO transistors first showed up in 2012, and were first manufactured by Sharp Corporation. IGZO allows for higher refresh rates and lower power consumption.polyimide substrate.

Brody, T. Peter (November 1984). "The Thin Film Transistor - A Late Flowering Bloom". IEEE Transactions on Electron Devices. 31 (11): 1614–1628. Bibcode:1984ITED...31.1614B. doi:10.1109/T-ED.1984.21762. S2CID 35904114.

Petti, Luisa; Münzenrieder, Niko; Vogt, Christian; Faber, Hendrik; Büthe, Lars; Cantarella, Giuseppe; Bottacchi, Francesca; Anthopoulos, Thomas D.; Tröster, Gerhard (2016-06-01). "Metal oxide semiconductor thin-film transistors for flexible electronics". Applied Physics Reviews. 3 (2): 021303. Bibcode:2016ApPRv...3b1303P. doi:10.1063/1.4953034.

Wager, John. OSU Engineers Create World"s First Transparent Transistor Archived 2007-09-15 at the Wayback Machine. College of Engineering, Oregon State University, Corvallis, OR: OSU News & Communication, 2003. 29 July 2007.

Fortunato, E. M. C.; Barquinha, P. M. C.; Pimentel, A. C. M. B. G.; Gonçalves, A. M. F.; Marques, A. J. S.; Pereira, L. M. N.; Martins, R. F. P. (March 2005). "Fully Transparent ZnO Thin-Film Transistor Produced at Room Temperature". Advanced Materials. 17 (5): 590–594. Bibcode:2005AdM....17..590F. doi:10.1002/adma.200400368. S2CID 137441513.

Brody, T. P.; Kunig, H. E. (October 1966). "A HIGH‐GAIN InAs THIN‐FILM TRANSISTOR". Applied Physics Letters. 9 (7): 259–260. Bibcode:1966ApPhL...9..259B. doi:10.1063/1.1754740. ISSN 0003-6951.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

Mimura, Akio; Oohayashi, M.; Ohue, M.; Ohwada, J.; Hosokawa, Y. (1986). "SOI TFT"s with directly contacted ITO". IEEE Electron Device Letters. 7 (2): 134–6. Bibcode:1986IEDL....7..134M. doi:10.1109/EDL.1986.26319. ISSN 0741-3106. S2CID 36089445.

Sunata, T.; Yukawa, T.; Miyake, K.; Matsushita, Y.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A large-area high-resolution active-matrix color LCD addressed by a-Si TFT"s". 33 (8): 1212–1217. Bibcode:1986ITED...33.1212S. doi:10.1109/T-ED.1986.22644. ISSN 0018-9383. S2CID 44190988.

Sunata, T.; Miyake, K.; Yasui, M.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A 640 × 400 pixel active-matrix LCD using a-Si TFT"s". IEEE Transactions on Electron Devices. 33 (8): 1218–21. Bibcode:1986ITED...33.1218S. doi:10.1109/T-ED.1986.22645. ISSN 0018-9383. S2CID 6356531.

Nagayasu, T.; Oketani, T.; Hirobe, T.; Kato, H.; Mizushima, S.; Take, H.; Yano, K.; Hijikigawa, M.; Washizuka, I. (October 1988). "A 14-in.-diagonal full-color a-Si TFT LCD". Conference Record of the 1988 International Display Research Conference: 56–58. doi:10.1109/DISPL.1988.11274. S2CID 20817375.

Manufacturer of standard & custom touch screen displays & thin film transistor touchscreen monitors. Features include 17 in. to 23 in. LCD, rugged steel & aluminum construction, optional resistive or capacitive touch-screens, light textured powder coated black color, contrast filters, transmissive daylight modification, hard coated vandal shields, 16.7 million display colors, anti-glare hard coating, analog RGB input, weight ranging 13 lbs to 24 lbs & 1280 x 1024 SXGA or 1600 x 1200 UXGA resolution. Applications include use for rack, wall, panel or kiosk installations in commercial, military & broadcast industries. One year limited warranty. RoHS compliant. Meet NEMA & Military Spec.

Orient Display sunlight readable TFT displays can be categorized into high brightness TFT displays, high contrast IPS displays, transflective TFT displays, Blanview TFT displays etc.

The brightness of our standard high brightness TFT displays can be from 700 to 1000 nits. With proper adding brightness enhancement film (BEF) and double brightness enhancement film (DBEF) and adjustment of the LED chips, Orient Display high brightness TFT products can achieve 1,500 to 2,000 nits or even higher luminance. Orient Display have special thermal management design to reduce the heat release and largely extend LED life time and reduce energy consumption.

Our high contrast and wide viewing angle IPS displays can achieve contrast ratio higher than 1000:1 which can make readability under strong sunlight with lower backlight luminance. High brightness IPS displays have been widely accepted by our customers with its superb display quality and it has become one of the best sellers in all our display category.Transflective display is an old monochrome display technology but it has been utilized in our color TFT line for sunlight readable application. Orient Display has 2.4” and 3.5” to choose from.

Blanview TFT displays are the new technology developed by Ortustech in Japan. It can provide around 40% of energy consumption for TFT panels which can use smaller rechargeable or disposable batteries and generate less heat. The price is also lower than traditional transflective TFT displays. Orient Display is partnering with the technology inventor to provide 4.3” and 5.0”.

Orient Display can also provide full customized or part customized solutions for our customers to enhance the viewing experience. Orient Display can provide all the different kinds of surface treatments, such as AR (Anti-reflection); AG (Anti-glare), AF (Anti-finger print or Anti-smudge); AS (Anti-smashing); AM (Anti-microbial) etc. Orient Display can also provide both dry bonding (OCA, Optical Clear Adhesive), or wet bonding (OCR, Optical Clear Resin and OCG, Optical Clear Glue) to get rid of light reflective in air bonding products to make the products much more readable under sunlight and be more robust.

Touch panels have been a much better human machine interface which become widely popular. Orient Display has been investing heavy for capacitive touch screen sensor manufacturing capacity. Now, Orient Display factory is No.1 in the world for automotive capacitive touch screen which took around 18% market share in the world automotive market.

Based on the above three types of touch panel technology, Orient Display can also add different kinds of features like different material glove touch, water environment touch, salt water environment touch, hover touch, 3D (force) touch, haptic touch etc. Orient Display can also provide from very low cost fixed area button touch, single (one) finger touch, double finger (one finger+ one gesture) touch, 5 finger touch, 10 points touch or even 16 points touch.

Considering the different shapes of the touch surface requirements, Orient Display can produce different shapes of 2D touch panel (rectangle, round, octagon etc.), or 2.5D touch screen (round edge and flat surface) or 3D (totally curved surface) touch panel.

Considering different strength requirements, Orient Display can provide low cost chemical tampered soda-lime glass, Asahi (AGC) Dragontrail glass and Corning high end Gorilla glass. With different thickness requirement, Orient Display can provide the thinnest 0.5mm OGS touch panel, to thickness more than 10mm tempered glass to prevent vandalizing, or different kinds of plastic touch panel to provide glass piece free (fear) or flexible substrates need.

Of course, Orient Display can also offer traditional RTP (Resistive Touch Panel) of 4-wire, 5-wire, 8-wire through our partners, which Orient Display can do integration to resistive touch screen displays.

Engineers are always looking for lower cost, faster, more convenient interfaces to transmit signals and to accept data and commands. The numbers of available interfaces available in the market can be dazzling. Orient Display follows market trends to produce various kind of interfaces for our customers to choose.

Genetic Interfaces: Those are the interfaces which display or touch controller manufacturers provide, including parallel, MCU, SPI(,Serial Peripheral Interface), I2C, RGB (Red Green Blue), MIPI (Mobile Industry Processor Interface), LVDS (Low-Voltage Differential Signaling), eDP ( Embedded DisplayPort) etc. Orient Display has technologies to make the above interface exchangeable.

High Level Interfaces: Orient Display has technologies to make more advanced interfaces which are more convenient to non-display engineers, such as RS232, RS485, USB, VGA, HDMI etc. more information can be found in our serious products. TFT modules, Arduino TFT display, Raspberry Pi TFT display, Control Board.

From the MOSFET, the TFT was born. The TFT varies from standard MOSFETs, or bulk MOSFETs, because, as the name implies, it uses thin films. The TFT began a new era of electronics. In 1968, just six years after the first TFT development, Bernard J. Lechner of RCA shared his idea of the TFT Liquid Crystal Display (LCD), something that would boom in popularity in our modern times. The TFT LCD was then first created in 1973 at the Westinghouse Research Laboratories. These LCDs were composed of pixels controlled by transistors. In FETs, substrates were just the semiconductor material, but in manufacturing TFT LCDs, glass substrates were used so that the pixels could be displayed.

But that was not the end of TFT developments. Soon after, in 1974, T. Peter Brody, one of the developers of the TFT LCD, and Fang-Chen Luo created the first active-matrix LCD (AM LCD). An active matrix controls each pixel individually, meaning that each pixel’s respective TFT had its signal actively preserved. This opened doors to better performance and speed as displays became more complex.

Though TFTs can use a variety of materials for their semiconductor layers, silicon has become the most popular, creating the silicon-based TFT, abbreviated as Si TFT. As a semiconductor device, the TFT, as well as all FETs, use solid-state electronics, meaning that electricity flows through the structure of the semiconductor layer rather than vacuum tubes.

Due to the variety in silicon’s possible structures, the Si TFT’s characteristics can vary as well. The most common form is amorphous silicon (A-Si), which is deposited during the first step of the semiconductor fabrication process onto the substrate in low temperatures. It is most usable when hydrogenated into the form A-Si:H. This then significantly alters the properties of A-Si; without the hydrogen, the material struggles with doping (the introduction of impurities to increase mobility of charges); in the form A-Si:H, however, the semiconductor layer becomes much more photoconductive and dopable. The A-Si:H TFT was first developed in 1979 which is stable at room temperature and became the best option for AM LCDs which consequently began rising in popularity after this breakthrough.

The biggest difference between these forms, notably A-Si and poly-Si, is that charge carriers are much more mobile and the material is much more stable when it comes to using poly-Si over A-Si. When creating complicated and high-speed TFT-based displays, poly-Si’s characteristics allow for this. Yet, A-Si is still very important due to its low-leakage nature, meaning that leakage current is not lost as heavily when a dielectric insulator is not totally non-conductive.

Several years later, another development was made in 2012 in the form of indium gallium zinc oxide (IGZO) which allowed for a more powerful display in terms of refresh rates and more efficiency in terms of power consumption. This semiconducting material, as stated in the name, uses indium, gallium, zinc, and oxygen. Though it is a form of zinc oxide (ZnO), the addition of indium and gallium allows this material to be deposited in a uniform amorphous phase but also maintaining the oxide’s high carrier mobility.

As TFTs began to increase their presence in display technology, transparent semiconductors and electrodes became more appealing to the manufacturers. Indium tin oxide (ITO) is an example of a popular transparent oxide used for its appearance, good conductivity, and ease of deposition.

Research of the TFT with different materials has led to the application of threshold voltage, or how much voltage is needed to turn on the device. This value is greatly dependent on thickness and choice of the oxide. When it comes to the oxide, this relates back to the idea of leakage current. With thinner layers and certain types of oxide, the leakage current may be greater, but this in turn could lower threshold voltage, as leakage into the device will also increase. In order to tap into the TFT’s potential for low power consumption, the lower the threshold voltage, the better the device’s appeal.

Another branch of development that stemmed from the TFT is that of organic TFTs (OTFT). First created in 1986, OTFTs usually use solution-casting of polymers, or macromolecules. This device made people hesitant, as it tended to have a slow carrier mobility, meaning slow response times. However, researchers have carried out experimentation with the OTFT because it has potential to be applied to displays different from those that traditional TFTs are used for, such as flexible, plastic displays. This research still continues today. With its simpler processing than traditional silicon technology, the OTFT holds much potential for modern day and future technologies.

Global Thin Film Transistor (TFT) Display Market, By Technology (Plasma Display (PDP), Organic Light Emitting Diode (OLED), Other), Type (Twisted Nematic, In-Plane Switching, Advanced Fringe Field Switching, Multi-Domain Vertical Alignment, Advanced Super View, Cell Technology), Panel Type (A_MVA, ASV, MVA, S_PVA, P-IPS), End Use (Domestic Use, Industrial Use) – Industry Trends and Forecast to 2029

Liquid crystal are considered highly light valves or electo-optic transducers. These thin film transistors are known to be simple electronic control devices widely fabricated on a large transparent substrates. They enable fabrication of electronic display.

Global Thin Film Transistor (TFT) Display Market was valued at USD 270.26 million in 2021 and is expected to reach USD 968.64 million by 2029, registering a CAGR of 17.30% during the forecast period of 2022-2029. Twisted Nematic accounts for the largest type segment in the respective market owing to its low cost. The market report curated by the Data Bridge Market Research team includes in-depth expert analysis, import/export analysis, pricing analysis, production consumption analysis, and pestle analysis.

A thin-film-transistor display refers to a form of LCD that uses TFT technology for enhancing image quality including addressability and contrast. These displays are commonly utilized in mobile phones, handheld video game systems, projectors, computer monitors, television screens, navigation systems and personal digital assistants.

Technology (Plasma Display (PDP), Organic Light Emitting Diode (OLED), Other), Type (Twisted Nematic, In-Plane Switching, Advanced Fringe Field Switching, Multi-Domain Vertical Alignment, Advanced Super View, Cell Technology), Panel Type (A_MVA, ASV, MVA, S_PVA, P-IPS), End Use (Domestic Use, Industrial Use)

Panasonic Corporation (Japan), LG Display Co., Ltd (South Korea), HannStar Display Corporation (Taiwan), AU Optronics Corp. (Taiwan), Chi Mei Corporation. (Taiwan), SAMSUNG (South Korea), SHARP CORPORATION (Japan), Schneider Electric (France), Siemens (Germany), Mitsubishi Electric Corporation (Japan), SONY INDIA. (India), FUJITSU (Japan), Chunghwa Picture Tubes, LTD. (Taiwan), Barco.(Belgium), BOE Technology Group Co., Ltd. (China), Innolux Corporation (Taiwan), Advantech Co., Ltd (Taiwan), among others.

The increase in the smartphone and tablet proliferation acts as one of the major factors driving the growth of thin film transistor (TFT) display market. Technological advancements are leading a radical shift from traditional slow, bulky and imprecise resistive mono touch to highly sensitive multi-touch capacitive screen have a positive impact on the industry.

The rise in number of electronic readers and growing demand for on-the-move information accelerate the market growth. The development of easy-to-use display devices drives the growth of the market.

The increase in application areas of large e thin film transistor (TFT) display due to the advantages offered by these paper displays in terms of user experience, manufacturing cost, readability, and energy consumption further influence the market.

Additionally, rapid urbanization, change in lifestyle, surge in investments and increased consumer spending positively impact the thin film transistor (TFT) display market.

On the other hand, high cost associated with the manufacturing is expected to obstruct market growth. Also, lack of awareness and low refresh rate are projected to challenge the thin film transistor (TFT) display market in the forecast period of 2022-2029.

This thin film transistor (TFT) display market report provides details of new recent developments, trade regulations, import-export analysis, production analysis, value chain optimization, market share, impact of domestic and localized market players, analyses opportunities in terms of emerging revenue pockets, changes in market regulations, strategic market growth analysis, market size, category market growths, application niches and dominance, product approvals, product launches, geographic expansions, technological innovations in the market. To gain more info on thin film transistor (TFT) display market contact Data Bridge Market Research for an Analyst Brief, our team will help you take an informed market decision to achieve market growth.

The COVID-19 has impacted thin film transistor (TFT) display market. The limited investment costs and lack of employees hampered sales and production of electronic paper (e-paper) display technology. However, government and market key players adopted new safety measures for developing the practices. The advancements in the technology escalated the sales rate of the thin film transistor (TFT) display as it targeted the right audience. The increase in sales of devices such as smart phones and tablets across the globe is expected to further drive the market growth in the post-pandemic scenario.

The thin film transistor (TFT) display market is segmented on the basis of technology, type, panel type and end-use. The growth amongst these segments will help you analyze meager growth segments in the industries and provide the users with a valuable market overview and market insights to help them make strategic decisions for identifying core market applications.

The thin film transistor (TFT) display market is analysed and market size insights and trends are provided by country, technology, type, panel type and end-use as referenced above.

The countries covered in the thin film transistor (TFT) display market report are U.S., Canada, Mexico, Brazil, Argentina, Rest of South America, Germany, Italy, U.K., France, Spain, Netherlands, Belgium, Switzerland, Turkey, Russia, Rest of Europe, Japan, China, India, South Korea, Australia, Singapore, Malaysia, Thailand, Indonesia, Philippines, Rest of Asia-Pacific, Saudi Arabia, U.A.E, South Africa, Egypt, Israel, Rest of Middle East and Africa (MEA).

North America dominates the thin film transistor (TFT) display market because of the introduction of advanced technology along with rising disposable income of the people within the region.

The thin film transistor (TFT) display market competitive landscape provides details by competitor. Details included are company overview, company financials, revenue generated, market potential, investment in research and development, new market initiatives, global presence, production sites and facilities, production capacities, company strengths and weaknesses, product launch, product width and breadth, application dominance. The above data points provided are only related to the companies" focus related to thin film transistor (TFT) display market.

Winstar Display offers a series of medium size O-Film TFT (Thin Film Transistor) displays featuring with wider viewing angle Technology. Most industrial application of TFT-LCD glasses that are available in the market are TN-LCD type. However, TN technology suffers from phenomenon called gray scale inversion. This means the display have one viewing side in which color of the image change suddenly after exceeding specified view angle. Therefore, the normal TFT models we offer which the viewing angle are limited. Winstar offers an O-Film TFT solution to enhance TN glass viewing angle and can overcome gray scale inversion.

The present invention relates to the field of display technology, and in particular to a thin-film transistor (TFT), a manufacturing method thereof, an array substrate, a display device and a barrier layer.

Flat-panel display devices such as liquid crystal displays (LCDs) and organic light-emitting diode (OLED) displays in the field of display technology have occupied a special place in the field of flat-panel display due to the advantages of light weight, small thickness, low power consumption, high brightness, high definition and so on. In particular, large-size, high-resolution and high-definition flat-panel display devices such as LCD TVs have been dominant in the current flat-panel display market.

Currently, image signal delay is a key factor restricting a large-size, high-resolution and high-definition flat-panel display device. More specifically, image signal delay is mainly determined by the signal resistance R of gate electrodes, gate lines or data lines and relevant capacitance C on a substrate. With the constantly increased size of the display device and the constantly increased resolution, the signal frequency applied by a drive circuit is constantly increased as well; and image signal delay becomes more seriously. In an image display period, a gate line is turned on and pixels are charged; but due to image signal delay, some pixels are not sufficiently charged, resulting in the non-uniform brightness in the displayed images and hence seriously affecting the display quality of the images. In addition, when the resistance of gate electrodes, gate lines or data lines is reduced, image signal delay is reduced, and hence the image quality can be improved.

As copper (Cu) ions can be easily diffused, and particularly diffused to a gate electrode protective layer, a semiconductor layer or a passivation layer at a high temperature, the performances of a thin film transistor (TFT) can be seriously affected. In particular, in the subsequent high-temperature heating processes on the TFT, due to the increased activity, the copper (Cu) ions can penetrate through an insulating barrier layer and into the semiconductor layer, and hence the performances of the TFT can be seriously affected, and consequently the image quality may become poorer, and even the normal operation of the TFT can be destroyed.

Embodiments of the present invention provide a thin film transistor (TFT), a manufacturing method thereof, an array substrate, a display device and a barrier layer. The present invention is used for improving the performances of the TFT and hence improving image quality.

To realize the above objection, a thin-film transistor (TFT) of an embodiment of the invention comprises: a gate electrode, a source electrode, a drain electrode, a semiconductor layer, a gate electrode insulating layer and a first metal barrier layer, which are disposed on a substrate; the gate electrode insulating layer is disposed between the gate electrode and the semiconductor layer; and the first metal barrier layer is disposed between the source/drain electrodes and the gate electrode insulating layer, and the first metal barrier layer is arranged on the same layer as the semiconductor layer and configured to prevent interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode.

For example, preferably, the first metal barrier layer is made of a metal oxide semiconductor material different from that of the semiconductor layer. Because the metal oxide semiconductor material can prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, it can improve the performances of the TFT and image quality.

For example, preferably, the TFT further comprises: a second metal barrier layer disposed between the first metal barrier layer and the source/drain electrodes and configured to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode so as to further improve the performances of the TFT and image quality.

For example, preferably, the structure of the TFT is as follows: the gate electrode is disposed on the substrate; the gate electrode insulating layer is disposed on the gate electrode; the semiconductor layer and the first metal barrier layer are disposed on the gate electrode insulating layer; the etching barrier layer is disposed on the semiconductor layer; and the second metal barrier layer is disposed on the semiconductor layer and the first metal barrier layer, and a source/drain electrode layer is disposed on the second metal barrier layer.

Or, the structure of the TFT is as follows: the source/drain electrode layer is disposed on the substrate; the second metal barrier layer is disposed on the source/drain electrode layer; the etching barrier layer is disposed on the second metal barrier layer; the semiconductor layer and the first metal barrier layer are disposed on the etching barrier layer; the gate electrode insulating layer is disposed on the semiconductor layer; and the gate electrode is disposed on the gate electrode insulating layer.

For example, preferably, the structure of the TFT is as follows: the gate electrode is disposed on the substrate; the gate electrode insulating layer is disposed on the gate electrode; the semiconductor layer and the first metal barrier layer are disposed on the gate electrode insulating layer; and the source electrode and the drain electrode are disposed on the first metal barrier layer.

Or, the structure of the TFT is as follows: the source electrode and the drain electrode are disposed on the substrate; the semiconductor layer and the first metal barrier layer are disposed on the source electrode and the drain electrode; the gate electrode insulating layer is disposed on the semiconductor layer and the first metal barrier layer; and the gate electrode is disposed on the gate electrode insulating layer.

For example, preferably, the structure of the TFT is as follows: the gate electrode is disposed on the substrate; the gate electrode insulating layer is disposed on the gate electrode; the semiconductor layer and the first metal barrier layer are disposed on the gate electrode insulating layer; the second metal barrier layer is disposed on the semiconductor layer and the first metal barrier layer; and the source electrode and the drain electrode are disposed on the first metal barrier layer.

Or, the structure of the TFT is as follows: the source electrode and the drain electrode are disposed on the substrate; the second metal barrier layer is disposed on the source electrode and the drain electrode; the semiconductor layer and the first metal barrier layer are disposed on the second metal barrier layer; the gate electrode insulating layer is disposed on the semiconductor layer and the first metal barrier layer; and the gate electrode is disposed on the gate electrode insulating layer.

For example, preferably, the first metal barrier layer is disposed at a position corresponding to the source electrode and the drain electrode, so as to simplify the structure of the TFT as much as possible.

For example, preferably, the second metal barrier layer is disposed at a position corresponding to the source electrode and the drain electrode, so as to simplify the structure of the TFT as much as possible.

An array substrate provided by an embodiment of the invention comprises the TFT which is provided with a first metal barrier layer only, and the first metal barrier layer prevents the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, thus improving the performances of the TFT and image quality.

For example, preferably, the array substrate further comprises: a data line and a gate line, in which the data line is connected with the source electrode of the TFT; the gate line is connected with the gate electrode of the TFT; and the first metal barrier layer is disposed at a position corresponding to the source electrode, the drain electrode and the data line; or,

the first metal barrier layer is disposed at a position corresponding to the source electrode, the drain electrode, the gate line and the data line, and the first metal barrier layer prevents the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, thus improving the performances of the TFT and image quality, and at the same time further prevent interdiffusion between the materials for the gate line and the data line, thus improving the performances of the TFT and image quality.

An array substrate provided by an embodiment of the invention comprises the TFT which is provided with both the first metal barrier layer and the second metal barrier layer, for further improving the performances of the TFT and image quality.

For example, preferably, the array substrate further comprises: a data line and a gate line, in which the data line is connected with the source electrode of the TFT; the gate line is connected with the gate electrode of the TFT;

the second metal barrier layer is disposed at a position corresponding to the source electrode, the drain electrode and the data line; or, the second metal barrier layer is disposed at a position corresponding to the source electrode, the drain electrode and the gate line; or, the second metal barrier layer is disposed at a position corresponding to the source electrode, the drain electrode, the gate line and the data line. The provision of the second metal barrier layer can further prevent the interdiffusion between the materials for forming the source electrode, drain electrode, the data line, and the gate line, further improving the performances of the TFT and image quality.

A display device provided by an embodiment of the invention comprises the above array substrate, comprising the TFT which is provided with a first metal barrier layer only, and can realize a display device having small image signal delay and good image quality.

A display device provided by an embodiment of the invention comprises the array substrate the above array substrate, comprising the TFT which is provided with both the first metal barrier layer and the second metal barrier layer, and can realize a display device having small image signal delay and good image quality.

A method for manufacturing a TFT provided by an embodiment of the invention, comprises: forming patterns of a gate electrode, a source electrode, a drain electrode and a semiconductor layer; and forming patterns of a gate electrode insulating layer and a first metal barrier layer, in which the gate electrode insulating layer is disposed between the gate electrode and the semiconductor layer; and the first metal barrier layer is disposed between the source/drain electrodes and the gate electrode insulating layer and arranged on the same layer as the semiconductor layer. The first metal barrier layer can prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, thus improving the performances of the TFT and image quality

For example, preferably, the method further comprises the process of forming a pattern of a second metal barrier layer, in which the second metal barrier layer is disposed between the first metal barrier layer and the source/drain electrodes, which can further improve the performances of the TFT and image quality.

In the TFT provided by the embodiment of the present invention, a first metal barrier layer is disposed between source/drain electrodes and a gate electrode insulating layer and configured to prevent the interdiffusion of materials for forming the source/drain electrodes and materials for forming a gate electrode, so as to improve the performances of the TFT and image quality. Moreover, a second metal barrier layer is disposed between the source/drain electrodes and the first metal barrier layer and configured to further prevent the interdiffusion between the material for forming the source/drain electrodes and the material for fondling the gate electrode, so as to improve the performances of the TFT and image quality.

Embodiments of the present invention provide a thin film transistor (TFT), a manufacturing method thereof, an array substrate, a display device and a barrier layer. The present invention is used for improving the performances of the TFT and hence improving image quality.

In general, a TFT at least comprises a gate electrode, a source electrode, a drain electrode and a semiconductor layer, which are disposed on a substrate, and a gate electrode insulating layer disposed between the gate electrode and the semiconductor layer. The source electrode and the drain electrode may be collectively referred to as a source/drain electrode layer, and the film layer of the TFT, in which the source/drain electrode layer is provided, is referred to as an SD layer. Moreover, the TFT further comprises an etching barrier layer disposed between the semiconductor layer and the source/drain electrodes. Generally, an etching barrier layer is not required to be disposed for an amorphous silicon TFT and a polysilicon TFT. As for a metal oxide TFT, in order to prevent the etching for the patterns of the source/drain electrodes from affecting the semiconductor layer made of a metal oxide, the etching barrier layer may be arranged. But there may be also the case that the semiconductor layer is made of a certain type of metal oxides and at the same time the etching barrier layer is not required. Furthermore, the TFT provided by the embodiment of the present invention further comprises a barrier layer disposed between the source/drain electrodes and the gate electrode insulating layer and configured to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, and the barrier layer is a first metal barrier layer which is configured to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, so as to improve the performances of the TFT and image quality.

At least one of the source electrode, the drain electrode and the gate electrode in the TFT provided by an embodiment of the present invention is made of copper or copper alloy of low resistivity. Of course, the present invention is not limited thereto, and the objective of the embodiment of the present invention is to adopt the first metal barrier layer to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode. In addition, other materials for forming the gate electrode, the source electrode and the drain electrode, which have high diffusibility, are also applicable to the present invention, for instance, gold and silver.

The first type of TFT, on a substrate, comprises a gate electrode, a source electrode, a drain electrode and a semiconductor layer, a gate electrode insulating layer disposed between the gate electrode and the semiconductor layer, an etching barrier layer disposed between the semiconductor layer and the source/drain electrodes, and a first metal barrier layer disposed between the source/drain electrode layer and the gate electrode insulating layer, in which the first metal barrier layer is arranged on the same layer as the semiconductor layer and configured to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode.

The second type of TFT, on a substrate, comprises a gate electrode, a source electrode, a drain electrode and a semiconductor layer, a gate electrode insulating layer disposed between the gate electrode and the semiconductor layer, and a first metal barrier layer disposed between the gate electrode insulating layer and the source/drain electrodes, in which the first metal barrier layer is disposed between the source/drain electrodes and the gate electrode insulating layer, and the first metal barrier layer is arranged on the same layer as the semiconductor layer and configured to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode.

The first metal barrier layer in the two types of TFTs provided by the present invention is configured to prevent the material for forming the source/drain electrodes from being diffused to the gate electrode insulating layer and/or the gate electrode, and to prevent the material for forming the gate electrode from being diffused to the semiconductor layer and/or the source/drain electrode layer.

In order to further prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode in the two types of TFTs provided by the present invention, for instance, preferably, a second metal barrier layer is provided between the first metal barrier layer and the source/drain electrode layer. The second metal barrier layer not only can prevent the material for forming the source/drain electrodes and the material for forming the gate electrode from being diffused to the semiconductor layer but also can prevent the material for forming the source/drain electrodes from being diffused to the gate electrode insulating layer and the gate electrode.

One preferred embodiment of the first type of TFT is as follows: the TFT comprises a substrate, and a gate electrode, a source/drain electrode layer and a semiconductor layer which are formed on the substrate, a gate electrode insulating layer formed on the substrate and disposed between the gate electrode and the semiconductor layer, an etching barrier layer disposed between the semiconductor layer and the source/drain electrode layer, and a first metal barrier layer disposed between the source/drain electrode layer and the gate electrode insulating layer, in which the first metal barrier layer is arranged on the same layer as and insulated from the semiconductor layer.

The source electrode and the drain electrode are made of copper. In order to prevent copper ions from being diffused to the gate electrode insulating layer and the gate electrode to contaminate the gate electrode and the gate electrode insulating layer and hence reduce the performances of the TFT, the first metal barrier layer is formed between the source/drain electrode layer and the gate electrode insulating layer to prevent the diffusion of the metal ions in the source/drain electrode layer.

Detailed description will be given below for the TFT, the manufacturing method thereof, the array substrate, the display device and the barrier layer provided by the present invention with reference to the accompanying drawings and different embodiments.

The TFT provided by the embodiment of the present invention may be a bottom-gate TFT or a top-gate TFT. Detailed description will be given below to the bottom-gate TFT and the top-gate TFT provided by the embodiments of the present invention with reference to the accompanying drawings.

The structure of the bottom-gate TFT provided by embodiment 1 is as follows: the gate electrode is disposed on the substrate; the gate electrode insulating layer is disposed on the gate electrode; the semiconductor layer and the first metal barrier layer are disposed on the gate electrode insulating layer; the etching barrier layer is disposed on the semiconductor layer; and the source electrode and the drain electrode are disposed on the etching barrier layer.

The structure of the top-gate TFT provided by embodiment 1 is as follows: the source electrode and the drain electrode are disposed on the substrate; the etching barrier layer is disposed on the source electrode and the drain electrode; the semiconductor layer and the first metal barrier layer are disposed on the etching barrier layer; the gate electrode insulating layer is disposed on the semiconductor layer and the first metal barrier layer; and the gate electrode is disposed on the gate electrode insulating layer.

The semiconductor layer and the first metal barrier layer may be arranged on the same layer or may be arranged on different layers. In order to reduce the overall thickness of the TFT as much as possible, for instance, preferably, the semiconductor layer and the first metal barrier layer are arranged on the same layer.

It should be noted that: unless otherwise specified, the vertical positional relationship between various film layers in the structure of all the TFTs provided by the present invention only refers to that the film layers are disposed on the same layer or disposed on different layers and does not refers to the specific structures of the film layers and the specific relative positions of the film layers with other film layers. For instance, “the etching barrier layer is disposed on the source electrode and the drain electrode” only refers to that the etching barrier layer is arranged on different layers with the source electrode and the drain electrode, and the etching barrier layer is disposed on the source electrode and the drain electrode with respect to the substrate, and that is the etching barrier layer is far away from the substrate compared with the source electrode and the drain electrode.

Detailed description will be given below with reference to the accompanying drawings. FIG. 1 is a top view of an array substrate, comprising a TFT, provided by embodiment 1, and FIG. 2 is a sectional view of the TFT as shown in FIG. 1 in the A-B direction.

The TFT as shown in FIG. 1 comprises a gate electrode 2, a source electrode 8, a drain electrode 9, an etching barrier layer 6 and a semiconductor layer. The array substrate as shown in FIG. 1 further comprises a data line 81 connected with the source electrode 8 and a gate line 21 connected with the gate electrode 2. The source electrode 8 and the drain electrode 9 may be collectively referred to as the source/drain electrode layer, and a film layer of the TFT, in which the source/drain electrode layer is disposed, is referred to as an SD layer.

Description will be given below by taking a bottom-gate TFT as an example. The bottom-gate TFT as shown in FIG. 2 comprises: a substrate 1; a gate electrode 2 formed on the substrate 2; a gate electrode insulating layer 3 formed on the substrate and disposed on the gate electrode 2; a semiconductor layer 4 and a first metal barrier layer 5 formed on the substrate and disposed on the gate electrode insulating layer 3, in which the semiconductor layer 4 and the first metal barrier layer 5 are arranged on the same layer; an etching barrier layer 6 formed on the substrate and disposed on the semiconductor layer 4, in which the etching barrier layer 6 is disposed on a channel of the semiconductor layer 4 and configured to protect the channel from being affected during the etching; and a source electrode 8 and a drain electrode 9 formed on the substrate 1 and disposed on the first metal barrier layer 5.

As the first metal barrier layer is disposed between the source/drain electrode layer (the SD layer) and the gate electrode insulating layer 3, metal ions in the source/drain electrode layer are prevented from entering the gate electrode insulating layer and the gate electrode layer. Similarly, metal ions in the gate electrode layer are also prevented from entering the semiconductor layer and the source/drain electrode layer, and hence the performances of the TFT can be improved.

In the TFT as shown in FIG. 2, preferably, the semiconductor layer 4 and the first metal barrier layer 5 are arranged on the same layer. In addition, the semiconductor layer 4 and the first metal barrier layer 5 may be also arranged on different layers, which will not be specifically limited herein.

When at least one of the material for forming the source/drain electrodes and the material for forming the gate electrode is copper or copper alloy, in order to further prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode, for instance, preferably, the TFT provided by embodiment 1 further comprises: a second metal barrier layer disposed between the first metal barrier layer and the source/drain electrodes and configured to prevent the interdiffusion between the material for forming the source/drain electrodes and the material for forming the gate electrode.

For instance, the structure of the bottom-gate TFT is as follows: the gate electrode is disposed on the substrate; the gate electrode insulating layer is disposed on the gate electrode; the semiconductor layer and the first metal barrier layer are disposed on the gate electrode insulating layer; the etching barrier layer is disposed on the semiconductor layer; the second metal barrier layer is disposed on the semiconductor layer and the first metal barrier layer; and the source/drain electrode layer is disposed on the second metal barrier layer.

The structure of the top-gate TFT is as follows: the source/drain electrode layer is disposed on the substrate; the second metal barrier layer is disposed on the source/drain electrode layer; the etching barrier layer is disposed on the second metal barrier layer; the semiconductor layer and the first metal barrier layer are disposed on the etching barrier layer; the gate electrode insulating layer is disposed on the semiconductor layer; and the gate electrode is disposed on the gate electrode insulating layer.

Detailed description will be given below with the accompanying drawing. As illustrated in FIG. 3, the TFT provided by embodiment 1 further comprises: a second metal barrier layer 7 disposed between the source/drain electrode layer and the first metal barrier layer 5.

The TFT comprises: a gate electrode 2 disposed on a substrate 1; a gate electrode insulating layer 3 disposed on the gate electrode 2; a semiconductor layer 4 and a first metal barrier layer 5 disposed on the gate electrode insulating layer 3; an etching barrier layer 6 disposed on the semiconductor layer 4; a second metal barrier layer 7 disposed on the semiconductor layer 4 and the first metal barrier layer 5; and a source electrode 8 and a drain electrode 9 disposed on the second metal barrier layer 7.

In the TFT as shown in FIG. 3, the second metal barrier layer 7 is disposed between the source/drain electrode layer and the first metal barrier layer 5, and further prevents metal ions in the SD layer from being diffused to the gate electrode insulating layer and/or the gate electrode and further improves the performances of the TFT.

In the TFT as shown in FIGS. 2 and 3, at least one of the source/drain electrode layer and the gate electrode is made of metallic copper (Cu) or copper alloy. For instance, preferably, the material for forming t

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey