tft lcd controller vhdl free sample

If we know how the LCD is receiving the data, we need to think how we can create an IP block that generates the same waveform. For that, we need at least 3 modules. SPI TX (spi_4l_8b.v) and memory module (spi_4l_8b_fifo.v) for configuration data. Some commands require a delay before sending the next command, for example,"software reset" or "sleep off". For that, we will add another module (spi_4l_8b_cmd_delay.v) that detects a particular command and stalls SPI transactions for a fixed amount of time.

First, let"s start with TX module. This module only responsibility is sending data to the LCD. When input AXI4-stream interface is valid, the module copies data to "command" reg and sends the data bit by bit.module spi_4l_8b(

With power of Vivado we have a possibility to define sequence of ili operations and use Verilog tasks in initial block like a software function that sends command to the LCD. Normally we should use $readmemh for sake of project portability as not all vendors support initial begin - task memory initialization.`define ili_NOP 8"h00 // No Operation - NOP

The testbench is really simple, as the FIFO needs to program LCD, it generates a known list of vectors that need to be serialized and displayed at SPI output. If input data is a command, we should see no operation in the simulation waveform for a while.`timescale 1ns / 1ns

Add SPI modules to block design, by dragging them from sources and other IPs for generating LCD signal and also a VIO for reset control. Minized PS IP FCLK_CLK0 is 50Mhz. LCD module maximum frequency is 10Mhz, so we need to use clocking wizard IP to lower clock frequency.

Generate bitstream and program Minized. If you have problems with VIO control, try to lower JTAG frequency. Use VIO to control the reset bit, as reset is active low, set this bit to high and look at the LCD.

In this article, you will learn how to use TFT LCDs by Arduino boards. From basic commands to professional designs and technics are all explained here.

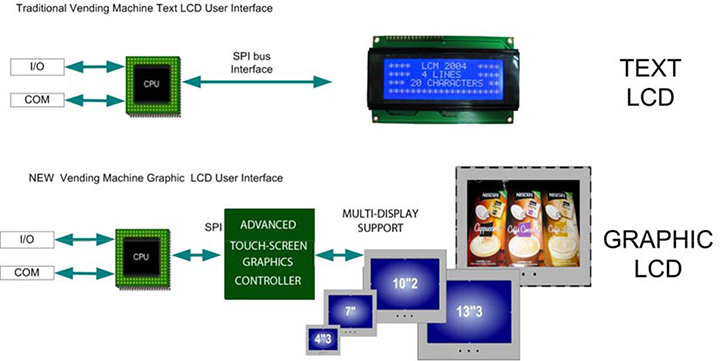

There are several components to achieve this. LEDs, 7-segments, Character and Graphic displays, and full-color TFT LCDs. The right component for your projects depends on the amount of data to be displayed, type of user interaction, and processor capacity.

TFT LCD is a variant of a liquid-crystal display (LCD) that uses thin-film-transistor (TFT) technology to improve image qualities such as addressability and contrast. A TFT LCD is an active matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven LCDs with a few segments.

In Arduino-based projects, the processor frequency is low. So it is not possible to display complex, high definition images and high-speed motions. Therefore, full-color TFT LCDs can only be used to display simple data and commands.

There are several components to achieve this. LEDs, 7-segments, Character and Graphic displays, and full-color TFT LCDs. The right component for your projects depends on the amount of data to be displayed, type of user interaction, and processor capacity.

TFT LCD is a variant of a liquid-crystal display (LCD) that uses thin-film-transistor (TFT) technology to improve image qualities such as addressability and contrast. A TFT LCD is an active matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven LCDs with a few segments.

In Arduino-based projects, the processor frequency is low. So it is not possible to display complex, high definition images and high-speed motions. Therefore, full-color TFT LCDs can only be used to display simple data and commands.

After choosing the right display, It’s time to choose the right controller. If you want to display characters, tests, numbers and static images and the speed of display is not important, the Atmega328 Arduino boards (such as Arduino UNO) are a proper choice. If the size of your code is big, The UNO board may not be enough. You can use Arduino Mega2560 instead. And if you want to show high resolution images and motions with high speed, you should use the ARM core Arduino boards such as Arduino DUE.

In electronics/computer hardware a display driver is usually a semiconductor integrated circuit (but may alternatively comprise a state machine made of discrete logic and other components) which provides an interface function between a microprocessor, microcontroller, ASIC or general-purpose peripheral interface and a particular type of display device, e.g. LCD, LED, OLED, ePaper, CRT, Vacuum fluorescent or Nixie.

The LCDs manufacturers use different drivers in their products. Some of them are more popular and some of them are very unknown. To run your display easily, you should use Arduino LCDs libraries and add them to your code. Otherwise running the display may be very difficult. There are many free libraries you can find on the internet but the important point about the libraries is their compatibility with the LCD’s driver. The driver of your LCD must be known by your library. In this article, we use the Adafruit GFX library and MCUFRIEND KBV library and example codes. You can download them from the following links.

Upload your image and download the converted file that the UTFT libraries can process. Now copy the hex code to Arduino IDE. x and y are locations of the image. sx and sy are size of the image.

while (a < b) { Serial.println(a); j = 80 * (sin(PI * a / 2000)); i = 80 * (cos(PI * a / 2000)); j2 = 50 * (sin(PI * a / 2000)); i2 = 50 * (cos(PI * a / 2000)); tft.drawLine(i2 + 235, j2 + 169, i + 235, j + 169, tft.color565(0, 255, 255)); tft.fillRect(200, 153, 75, 33, 0x0000); tft.setTextSize(3); tft.setTextColor(0xffff); if ((a/20)>99)

while (b < a) { j = 80 * (sin(PI * a / 2000)); i = 80 * (cos(PI * a / 2000)); j2 = 50 * (sin(PI * a / 2000)); i2 = 50 * (cos(PI * a / 2000)); tft.drawLine(i2 + 235, j2 + 169, i + 235, j + 169, tft.color565(0, 0, 0)); tft.fillRect(200, 153, 75, 33, 0x0000); tft.setTextSize(3); tft.setTextColor(0xffff); if ((a/20)>99)

Abstract: vhdl code for lcd of xilinx vhdl code for lcd display XAPP149 handspring vhdl code for digital to analog converter analog to digital converter vhdl coding serial analog to digital converter vhdl code XAPP355 oscilloscope

Text: designs. A detailed understanding of the VHDL code is not needed. Rather, the designer needs only to , "constants" section of the VHDL code can then be modified to accordingly. This reference design shows how to , executes its next line of code . The PocketC code that is used to retrieve, compute and display the , to measure and display voltage at a particular source. The Handspring VisorTM line of personal , source code will also be provided for download. To obtain the VHDL code described in this document, go

Abstract: vhdl code manchester encoder VHDL Coding for Pulse Width Modulation XAPP339 ook modulation vhdl code matrix converting circuit VHDL or CPLD code VHDL code of lcd display vhdl manchester DR300 DR3000

Text: of keyboard control is also covered in this document. The VHDL code is not provided for this portion , power capabilities of a CoolRunner CPLD. To obtain the VHDL code described below go to the section , specific application. The addition of keyboard control is also covered in this document. The VHDL code is , power capabilities of a CoolRunner CPLD. To obtain the VHDL code described below go to the section , specific application. The addition of keyboard control is also covered in this document. The VHDL code is

Abstract: vhdl code for lcd display LCD module in VHDL 3D LCD controller UART using VHDL vhdl code for game vhdl code for sdram controller 3D Accelerator fpga TFT altera processor control unit vhdl code

Text: . We developed the LCD Controller module in VHDL , created a Symbol File of it, and connected it to the , address of the frame buffer, which is placed in SDRAM. The thin-film transistor (TFT) LCD controller , -D graphic display system is the speed of computing and displaying a frame of 3-D graphics. The general unit of 3-D graphic display speed is frames per second (fps). We tested the speed of our system , Process The LCD Control module displays the data of the frame buffer to the screen of the TFT LCD . It

Abstract: XAPP381 COOLRUNNER-II 7 segment program VHDL code of lcd display COOLRUNNER-II 7 segment pciii COOLRUNNER-II examples low pass Filter VHDL code vhdl code for lcd display Xilinx lcd

Text: roughly 100 Hz. Each segment of the display is bonded out to a pin on the LCD , which is then driven , code , examine the previous rate at which the LCD display enables the individual segments. After , CoolRunner-II CPLD, a boost power regulator, display unit(s), a small amount of user I/O, and two clock , which will accommodate a standard, twodigit by seven-segment LCD display (such as the Varitronix VI , higher drive voltage, the contrast of the display may be somewhat diminished. Power Jumpers JP1/JP2 Two

Abstract: led sign board circuit diagram SD178A VHDL code of lcd display vhdl code SD178 led sign diagram sign board LED DISPLAY CIRCUIT diagram EP2C20F484C7 Altera DE1 Board Using Cyclone II FPGA Circuit

Text: sub-module using the C language Functions/objectives achieved Display the main interface of smart , (compiled from VHDL code ) SD178A voice circuit and program SD178A CNTR (compiled from VHDL code , of Technology Participants: Jian Jinrong, Zhan Yilin, Lin Taida Instructor: Xiao Ruxuan , station sign system that can be used on all roads, improving the convenience and safety of bus passengers. Target Users The smart bus station sign"s main interface has a variety of buttons. When a user activates

Abstract: vhdl code for i2c Slave VHDL code of lcd display verilog code for transmission line vhdl code for lcd display vhdl code for i2c verilog code lcd digital radio verilog code I2C CODE OF READ IN VHDL vhdl source code for i2c memory read and write

Text: trademarks of their respective owners. Source code : VHDL Source Code or/and VERILOG Source Code or/and , easy connection to target device e.g. memory, LCD display , pressure sensors etc. Fully , license for VHDL , Verilog source code called HDL Source Encrypted, or plain text EDIF called , the core to a passive devices e.g. memory, LCD display , pressure sensors, I/O devices etc , serial bus that provides a simple and efficient method of data transmission over a short distance

Abstract: VHDL code of lcd display I2C CODE OF READ IN VHDL vhdl code for lcd display verilog code for shift register verilog code for i2c communication fpga DI2CM vhdl code for i2c Slave verilog code lcd verilog code for i2c

Text: trademarks of their respective owners. Source code : VHDL Source Code or/and VERILOG Source Code or/and , . Allows easy connection of the core to a passive devices e.g. memory, LCD display , pressure sensors, I/O , . memory, LCD display , pressure sensors etc. and an I2C bus. It can works as a slave receiver or , interface allows easy connection to target device e.g. memory, LCD display , pressure sensors etc , VHDL , Verilog source code called HDL Source Encrypted, or plain text EDIF called Netlist

Abstract: ook modulation vhdl code VHDL code of lcd display vhdl code for lcd display vhdl code manchester and miller encoder LCD module in VHDL vhdl code manchester encoder vhdl code miller encoder vhdl manchester encoder XAPP353

Text: capabilities of a CoolRunner CPLD. To obtain the VHDL code described below go to the section titled " VHDL , . The VHDL code is not provided for this portion of the design. With keyboard control, a user can enter a text string into the transmitter and the string would be display on the receive side of the , times. This insures the data has time to be displayed on the LCD of the CPLD demo board and allows for , block diagram is shown in Figure 3. Transmission comprises of three VHDL entities; DISPLAY_COUNT

Abstract: UART using VHDL vhdl code for uart communication verilog code for uart communication uart verilog code verilog code lcd interface of rs232 to UART in VHDL block diagram UART using VHDL program uart vhdl fpga uart vhdl fpga

Text: code in the display of an integer variable. The following sample code segment demonstrates sending the , The UltraController Software UART was simulated in Verilog and VHDL with the LCD display routines and , example source files for both Verilog and VHDL implementations of the Software UART, C source files for , . NOTICE OF DISCLAIMER: Xilinx is providing this design, code , or information "as is." By providing the design, code , or information as one possible implementation of this feature, application, or standard

Abstract: free verilog code of median filter obstacle detection through ultrasonic sensors and verilog code for median filter free vHDL code of median filter verilog median filter sharp gp2d150a vhdl code for lcd display VHDL code of lcd display obstacle sensors

Text: the vibrotactors through the UltraController interface. Vibrotactors LEDs LCD Display 17 3 , component instantiations in the top-level VHDL module. The number and names of input and output signals are also specified in this module, as shown in the code below. The top-level VHDL system with , blind-spot detector, as well as C code that maintains awareness of the presence or absence of an obstacle , microcontroller that enables quick development of PowerPC applications. (For additional information on the

Abstract: CMOS sensor 2 megapixel 1600 x 1200 pixels K2607 transistor XAPP390 ALPHANUMERIC DISPLAY image ccd image sensor CMOS image sensor PAL Micron 0343 optrex lcd VGA RGB LCD control

Text: connect in a grid pattern to access all pixels in the display . With this type of integration, the LCD can , the Optrex LCD . An inverter controls the voltage applied to the CCT of the Optrex display , The counters shown in Figure 18 are used for creating the timing specifications of the LCD display , -bit counter that keeps track of the number of lines for the LCD display . CLK_CNT is a general purpose 17 , is available for download in " VHDL Code ," page 18. Introduction Digital cameras have become

Abstract: 20X4 LCD display 20x4 line lcd 20X4 LCD vhdl code for lcd display 20X4 LCD ic BLCD VHDL audio codec 20x4 lcd line address C0805X7R251-223KNE

Text: TDC1 Schematics Appendix B TDC1 Bill of Material Appendix C Keypad & LCD CPLD VHDL Code Appendix D Keypad & LCD CPLD Schematic MOTOROLA Table of Contents For More Information On This Product, Go , Appendix C, Keypad & LCD CPLD VHDL Code - contains source code for keypad and LCD . · Appendix D, Keypad & LCD CPLD Schematic - includes aa schematic of the keypad and LCD . Suggested Reading More , , a telecommunications codec, 5x5 push-button keypad, a 20x4 LCD display and a set of daughter card

Abstract: LCD module in VHDL LFXP2-5E-5TN144C lcd module verilog "1 wire slave interface" verilog wishbone vhdl for lcd lfxp25e5tn144c Driver/S6A0069 LCMXO2280C-3T100C

Text: Liquid Crystal Display ( LCD ) is a flat display device used in many electronic products. These slim and , controller and driver are able to display a wide variety of symbols through the interpretation of a simple 4 , (RTL) Implementation The RTL block diagram of the LCD module interface is shown in Figure 2. It consists of three modules, the top-level module, the WISHBONE slave module and the LCD interface module , . The timing of the signals meets the access time requirements for read and write of the LCD . It

Abstract: lcd module verilog verilog code lcd vhdl code 8 bit microprocessor XAPP672 verilog code 16 bit processor PPC405 VHDL code of lcd display Xilinx lcd display controller vhdl code for lcd of xilinx

Text: reference design are module examples of LED and LCD display drivers, square-wave sound generation , function, and function to write two strings; one each to the upper and lower lines of the LCD display , showed that 2,400 logic cells equated to 16k Bytes of code /data storage. Trade-offs of this type can , demonstrated in the reference design, this is easily done in a few lines of C code . The UltraController , code examples in Verilog and VHDL . The PowerPC software reference design example is in C code . The

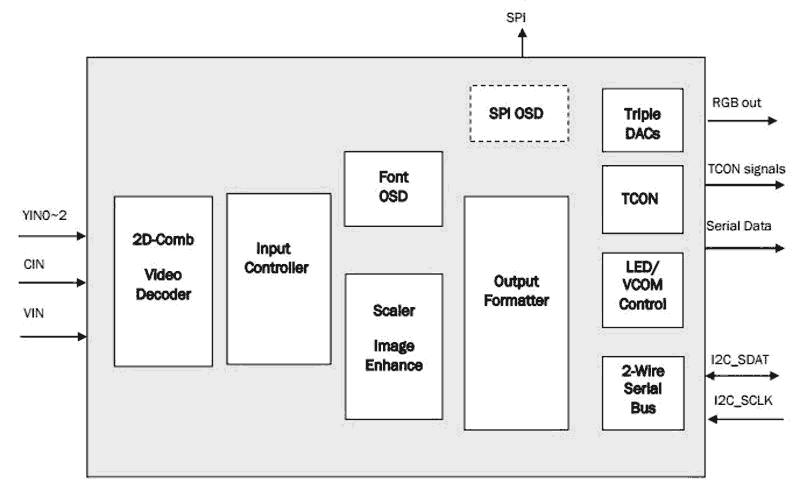

Text: or SDRAM. Figure 1 depicts the system view of the DB9000AVLN TFT LCD Controller IP Core embedded , System Diagram Features Wide range of programmable LCD Panel resolutions: o Maximum programmable , . DB9000AVLN Avalon Bus LCD Controller Fully-synchronous, synthesizable Verilog or VHDL RTL core, with , to the LCD panel is listed in Table 1. Note that if the panel is 18-bits data, the lower 6-bits of , variety of methods for prospective customers to evaluate the DB9000AVLN. These include Verilog or VHDL

Abstract: VHDL code of lcd display 7 segment display 5611 Xilinx lcd display controller video pattern generator vhdl ntsc VHDL code for interfacing renesas with LCD bitblt raster PAL to ITU-R BT.601/656 Decoder Xilinx lcd display controller design fpga frame buffer vhdl examples

Text: designer to reuse processor solutions and still take full advantage of the latest development in display , and the LCD /TFT displays. BADGE includes a number of GPUs (Graphics Processing Units). See fig 1 , memory sizes and types. A variety of host controllers aimed at different CPU buses and display , supported on request. Display Controller The display controller handles the interface to the LCD /TFT , BADGE BitSim Accelerated Graphics Display Engine May 7, 2008 Product Specification

Abstract: block diagram of MP3 player block diagram mp3 player MAS3507D xilinx mp3 vhdl decoder VHDL code of lcd display vhdl code for lcd of xilinx mp3 player mp3 decoder chip Xilinx lcd display controller design

Text: Flash memory. This design assumes that an LCD display could be designed with unique icons for the , Note (XAPP328) · VHDL Source Code · VHDL Testbenches 35 Xilinx , Diagram The block diagram of the CoolRunner MP3 Portable Player is shown in Figure 1. The shaded area , following functions: · The Main Control Logic provides the intelligence of the CPLD logic and controls all of the various functions. · The Parallel Port Interface is used to downloading MP3 data files to

Abstract: vhdl code for deserializer verilog code for lvds driver sdi verilog code vhdl code for lvds driver SDI pattern generator vhdl code for rs232 altera audio file in vhdl code vhdl code scrambler Altera Cyclone III

Text: graphics LCD display 16 x 2 line character display 4 user pushbutton switches 8 user DIP switches 8 user LEDs and 1 x 7-segment LED display Altera HSMC SDI I/O Card 1 x SDI input, 1 x SDI loop output , 27MHz VCXO for genlock Clock input/ouput connectors Firmware Components Source code provided in both Verilog & VHDL Support for all major SD, HD, and 3Gb/s type A SDI formats: 486i, 576i, 720p , containing source code and documents -

Text: Error Detection Video Frame Buffer Dual Display Controller Graphics LCD Controller LCD Controller , -character 16-segment LCD display ⢠4 capacitive touch sense buttons ⢠1 Mbit SPI Flash ⢠I2C , P 4-Character LCD display plus 4 capacitive touch sense buttons and I2C temperature sensor Up , Lattice products in a growing number of applications. Weâve shipped over a billion devices to customers , . Our low density LatticeECP3⢠family is comprised of the lowest power, SERDES-enabled FPGAs in the

Abstract: microblaze XC2V1000 XC2V1000-4FG456C virtex memec xilinx vhdl rs232 code vhdl code for rs232 XC2V1000 XC2V1000 complete lcd module verilog architecture in 4289

Text: port, USB port, RS-232 port, I2C and SPI ports, programmable LCD display connector and a PS/2 keyboard , designs with source code ( VHDL and Verilog HDL) Virtex-II MicroBlaze Development Kit s SelectMap , 10/100 Ethernet USB port RS-232 port PS/2 Keyboard port I2C and SPI ports LCD display , RISC architecture supporting both on-chip and off-chip memory for code and data storage. The compact size of the processor core requires only 900 logic cells, yet delivers 82 Dhrystone MIPs, making it

Text: related source code will also be provided for download. To obtain the VHDL code described in this document, go to section VHDL Code Download, page 9 for instructions. Overview Operation of the Digital , understanding of the VHDL code is not needed. Rather, the designer needs only to focus on the details of the ADS7870. If certain aspects of the ADS7870 need to be adjusted, the "constants" section of the VHDL code , next line of code . The PocketC code that is used to retrieve, compute and display the results for

Text: Appendix B TDC1 Bill of Material Appendix C Keypad & LCD CPLD VHDL Code Appendix D Keypad & LCD CPLD , LCD CPLD VHDL Code contains source code for keypad and LCD . · Appendix D, Keypad & LCD CPLD Schematic includes a schematic of the keypad and LCD . Suggested Reading More documentation on the , keypad, a 20x4 LCD display and a set of daughter card expansion connectors. The daughter card expansion , C Keypad & LCD CPLD VHDL Code Appendix C, Rev. 2 Freescale Semiconductor C-1 - Vhdl

Abstract: COOLRUNNER-II 7 segment COOLRUNNER-II ucf file application for lcd digital thermometer circuit diagram for lcd digital thermometer Xilinx lcd display controller NTC25 Xilinx lcd display controller design adc controller vhdl code design and implementation of digital thermometer

Text: CoolRunner-II data sheet concerning information on maximum power consumption. Drive a LCD Display To drive an LCD , a clock at the common pin of the display is required. The following example shows how to enable , shows how to connect the Sensor and LCD Display according the .ucf File. D Connector of CoolRunner-II , example shows how to display the temperature on a 7-segment Liquid Crystal Display ( LCD ): 1. For the , the temperature, a simple "BIN2BCD" decoder can be used in the design. Note: For an LCD display , a

Abstract: 10.1 inch lcd with led backlight 40 pin connector pinout vhdl code for rs232 receiver philips lcd 15.4 pinout PL041 vhdl code for a 16*2 lcd schematic diagram tv sharp LM-XCV2000 schematic diagram lcd tv sharp inverter 9PIN MMC socket

Text: Limited and third parties that provide additional information on developing code for the ARM family of , Features The main features of the interface module are as follows: · display support: - interface to , of display is the PrimeCell CLCD controller (PL110). RED Video DAC (U20) B24 GREEN , ] VGA connector (J30) Figure 3-17 shows the architecture of the display interface. The diagram shows , dedicated connector for a 8.4 inch Sharp LCD display and the second (J27) provides a generic interface

Abstract: lcd module verilog binary to lcd verilog code embedded c program for LED interfacing with ARM vhdl code for lcd display vhdl sdram VHDL code of lcd display vhdl code for ddr sdram controller

Text: , the seven segment display , and the LCD . Four push buttons are used to control output to these , . This action makes only the LED display the counting result instead of all devices (seven segments display , LCD , and Nios II Console). Figure 18 shows the operation when interrupt occurred. Notice that , Builder system module, it is easy to open the Verilog or VHDL source code created by the SOPC Builder to , */: In VHDL : signal my_reg: stdlogic; attribute preserve : boolean; attribute preserve of my_signal

Text: buffer memory via the Avalon Bus to a TFT LCD panel. In an Altera FPGA , typically, the microprocessor is , within a FPGA . FPGA Avalon-MM System DB9000AVLN TFT LCD Controller Processor TFT LCD Panel , of Altera FPGA devices. Table 2 list example FPGA implementation results using Altera Quartus II , : DB9000AVLN Altera FPGA Utilization & Performance Verification Method The DB9000AVLN contains a test , DB9000AVLN has been verified in an Altera FPGA instantiated with a NIOS II processor, driving a variety of

Abstract: Cyclone TFT interface of TFT lcd with microcontroller car navigation system alpha blending bt.656 parallel to RGB bt.656 parallel to serial conversion vga VGA VIDEO CONTROLLER SPI to vga lcd driver

Text: graphics implementation in an Altera Cyclone II FPGA . The video-in could be BT.656 input (YUV 4:2:2 , Implementation Using Cyclone II FPGA (EP2C5) To Remote Display To TFT Display Graphics Rear Seat , been absorbed by the FPGA , in this case provided by Altera "s 32-bit Nios II RISC processor. The CAN , How FPGAs Enable Automotive Systems Tapan A. Mehta Sr. Strategic Marketing Manager Altera , . Talking to these processors are various peripherals such as keyboards and TFT displays. Graphics

Abstract: fpga TFT altera block diagram of Video graphic array Judd Wire Cyclone TFT bt.656 to RGB GRAPHICAL LCD DIAGRAM bt.656 to RGB LCD display FPGA-based LCD driver circuit E144

Text: buffer memory via the Avalon Bus to a TFT LCD panel. In an Altera FPGA , typically, the microprocessor is , includes an Altera FPGA and TFT LCD panel. Deliverables The DB9000AVLN is available in synthesizable , within a FPGA . FPGA Avalon-MM System DB9000AVLN TFT LCD Controller Processor TFT LCD Panel , checks expected results. The DB9000AVLN has been verified in an Altera FPGA instantiated with a NIOS II , Digital Blocks DB9000AVLN Semiconductor IP Avalon Bus TFT LCD Controller General

Abstract: vhdl code for lcd display LCD module in VHDL 3D LCD controller UART using VHDL vhdl code for game vhdl code for sdram controller 3D Accelerator fpga TFT altera processor control unit vhdl code

Text: Figure 1. Altera Corporation 109 Nios II Embedded Processor Design Contest-Outstanding Designs , address of the frame buffer, which is placed in SDRAM. The thin-film transistor ( TFT )LCD controller module independently reads the frame buffer and displays the 3-D graphics on the TFT LCD repeatedly. The , displaying a cube spinning on an x, y diagonal axis, as shown in Figure 2. 110 Altera Corporation , Diagram FPGA Nios II Processor Avalon Bus 1 Ext_ram_bus Flash Memory Flash Memory

Text: Altera "s free Quartus® 2 Web Edition tools for FPGA programming The CAP7 Starter Kit Standalone Board , Technical Support www.atmel.com/products/AT91CAP Altera FPGA PIOA MPIO SPI JT AG FPGA USB , FPGA that emulates the functionality of the CAP MP Block, while at the same time providing a , Flash, 3.3V n Altera ® Cyclone® II EP2C8F256C7N(256BGA) n Altera Configuration PROM -EPCS4SI8N n 0-Lead Extension Connector (x3) for I/O 4 Access n 2.8 inch TFT Color LCD n wo Serial Ports (One Connected

Abstract: lvds 1080p point-to-point mini-lvds lvds 1080p panel mini-lvds source driver ttl to mini-lvds fpga TFT altera CYCLONE3 DATA VISION LCD MODULE mini-lvds driver

Text: , low-cost Cyclone III FPGA Altera complete low-cost display solutions at your fingertips: 152 The Cyclone III FPGA is an image enhancement engine that drives a typical liquid crystal display (LCD , Altera Cyclone III FPGAs in display applications Displays Design for the largest displays or , will you convert your vision for the future into reality? Choose Altera ® Cyclone® III FPGAs, with , . Cyclone III FPGA highlights The Cyclone III family offers features beyond any other low-cost FPGA

Text: Structures With Open-System Architectures Altera Corporation automotive microcontroller will soon be , ariant - C Basic I/O V ariant - A Scalable FPGA / HardCopy Memory System 2 Function , ariant - B Embedded CPU Subsystems Altera Corporation Enabling New Infotainment-Equipment Cost , building blocks (such as Altera ® Cyclone III® or Stratix III® FPGAs), the synthesized prototypes are , , which then costs only a fraction of the FPGA . The production building block may be a HardCopy

Text: targeted for Altera "s FPGA , using Altera tools. In our opinion, we have extensively utilized the versatile , ( TFT ) LCD controller and YUV-to-RGB color space converter to display decoded pictures. An expansion prototype connector links our TFT LCD panel to the Nios II development board. Performance Parameters Our , 30 frames per second (fps) decoding capability based on a 200-MHz SOPC solution. With the FPGA , Controller with Color Space Conversion TFT LCD Module rd_addres sstall wrclock rdclock rdclocken

Abstract: VHDL code for ADC and DAC SPI with FPGA usb 2.0 implementation using verilog Xilinx Ethernet development nanoboard vhdl code for i2c XC3S1500 SPARTAN-3 BOARD SPARTAN 6 Configuration SPARTAN 6 peripherals datasheet XILINX SPARTAN XC3S1500

Text: · FPGA design entry in C, OpenBus, Schematic, VHDL and Verilog · Supports range of swappable , processors for use in FPGA design · Automatic peripheral and daughter board detection and configuration , board specifications · Integrated color TFT LCD panel (320x240) with touch screen that facilitates , FPGA-based instruments for hardware debug and deployment · Support for importing third-party FPGA IP cores , target FPGA · Power sensing system allows real-time monitoring of system and device power consumption

Text: scaling function, easily employed in a Cyclone III FPGA along with a core from the Altera ® Video and , existing FPGA design with no additional cost. 2 Altera Corporation Using Cyclone III FPGAs for , the panel size. Those challenges are easily managed with the new low-cost Cyclone® III FPGA family , signals onto the display panel. In addition, designers can take advantage of the Cyclone III FPGA , flexibility for digital televisions and displays. Manufacturers of LCD TVs can use a Cyclone III FPGA as a

Text: introduction rates of new models are fueling increased FPGA use within high-definition television electronics , requirements are video processing and high bandwidth chip-to-chip communication. Altera has developed and , manufacturers have designed using Altera ® Cyclone® FPGAs include: Timing controller (TCON), using , Altera Corporation Picture quality enhancement, such as frame rate conversion and local dimming for , DisplayPort Figure 2 illustrates how these sub-functions are interrelated. Figure 2. FPGA Implementation

Text: Complete Reference Design and source code for NTSC/PAL TV Player and Pattern Generator using Altera DE2 , everything you need to develop applications using a digital panel on the Altera DE2/DE1 board. The kit , Generator using the TRDB_LCM and Altera DE2/DE1. This chapter provides users key information about the kit , below: 1. Equipped with Toppoly TD036THEA1 compact TFT LCD module. 2. Handle digital signals , Figure 3.1. The YUV 4:2:2 data is sent from TV decoder to the cyclone II 2C35 FPGA . The FPGA on the DE2

Text: Features 24 bit TFT LCD Controller 16x32 Pixel FIFO SOCTFTLCD-AHB TFT LCD Controller , is a configurable TFT LCD Controller. The Core interfaces to an AHB or generic microprocessor bus and provides all the timing control and pixel serialization for controlling various TFT LCD Display , and simulation test-benches. The SOC-TFTLCD-AHB can also be delivered as an FPGA Netlist for Xilinx, Altera and Actel FPGAs. Support The SOC-TFTLCD-AHB core as delivered is warranted against defects for

Abstract: EP3C120F780C7N Cyclone TFT JTAG CONNECTOR cyclone iii fpga scrolling message display in fpga push button switch 4 pin fpga orcad schematic symbols 7-segment-display pin configuration cyclone III datasheet DDR2 x16

Text: . Figure 1. Altium"s Altera Cyclone II daughter board DB31. Key features · · Altera Cyclone II FPGA , Common-Bus SRAM Motherboard Resources Accessible by FPGA Design (e.g. TFT LCD panel, CAN, RS , ® Technical Reference for Altium"s Altera ® Cyclone II Daughter Board DB31 Summary This reference document provides detailed information on Altium"s Altera Cyclone II daughter board DB31, including the physical FPGA device it offers and any additional resources available to an FPGA design

Abstract: Verilog code for ADC and DAC SPI with FPGA vhdl code for rs232 receiver using fpga nanoboard 3000 240x320 Color LCD schematic motherboard coil EP3C40F780C8N nanoboard XC3S1400AN-4FGG676C VHDL code for PWM

Text: Designer · High-capacity FPGA located on the motherboard, and provision for a single plug-in peripheral , user FPGA 256KB x 32-bit common-bus SRAM (1MB), 16M x 32-bit common-bus SDRAM (64MB), 8M x 16 , golden boot image for Host Controller, two for use by user FPGA (for boot/embedded purposes) · SPI , managing JTAG communications (with Altium Designer/User FPGA /connected peripheral board), as well as , the board (and GND) - anoBoard 3000AL with fixed Altera ® CycloneTM III device N (EP3C40F780C8N

Abstract: 128X64 graphical LCD display specifications 128X64 graphical LCD EP3C120F780C7N 128X64 graphical LCD screen rohs 128X64 graphical LeD screen AC12 AH15 cycloneIII DDR2 chip

Text: reference designs have been evaluated in a variety of technologies. The following are sample Altera results optimized for speed with a FIFO size of 512x48 bits implemented. Altera Device Cyclone-II , megafunction is available in ASIC (synthesizable HDL) and FPGA (netlist) forms, and includes everything required for successful implementation. The Altera version includes: · Post-synthesis EDIF netlist · , monitor, or a TFT panel. The CPU controls the configuration of the megafunction and process interrupt

Abstract: kingston SD card kingston sd lcd tcb8000a kingston sd SPI LCD Module topway datasheet by topway mmc kingston VGA TO AV CONVERTER Nixie kingston mmc card 512

Text: Altera "s FPGA development boards can implement multimedia playing. Considering the pressure on the , network module control board for the GPIO interface and LCD display FPGA : Altera Cyclone® II , demands. Because Altera provides an abundant intellectual property (IP) core library, we can implement , )-The complete Altera ®-provided IDE, from the Quartus® II software to SOPC Builder and to the Nios II , Altera "s FPGAs, we can complete the system configuration and implementation with higher performance and

Digital Blocks TFT LCD Controller reference design enables you to accelerate the design-in of TFT LCD panel displays in your system. The reference design centers on the Digital Blocks DB9000AVLN TFT LCD Controller intellectual property (IP) core, which is available in netlist or VHDL/Verilog HDL register transfer level (RTL) formats.

The DB9000AVLN core contains an Avalon® Memory-Mapped system interconnect for interfacing to the Nios® II embedded processor and SDRAM or SRAM controllers (either memory can serve as the frame buffer). Software supplied with this reference design runs on the Nios II embedded processor to place an image in the frame buffer memory and invokes the DB9000AVLN core to drive the LCD panel.

Using the Intel® Quartus® Design Software, you can instantiate the TFT LCD Controller reference design in a Cyclone®, Cyclone® II, or Cyclone® III FPGA development kit. See the Demonstrated Intel® Technology section for a complete list of supported Intel® FPGA development kits.

You can connect your LCD panel to the Intel FPGA development kit with the fabrication of an appropriate cable. Please contact Digital Blocks for more details.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey