lcd panel edid eeprom error quotation

Does anybody happen to have a full EEPROM dump (4 KB) for the AUO B156HTN03.8 LED panel? I"d need not only the EDID part (first 128 bytes), but also the rest of the LCD FW, which seems to be located on the same EEPROM chip as the EDID but from offset 0x100.

Interestingly, it seems as though the EEPROM was "randomly" overwritten at offsets 0x0, 0x100 and 0x200 with some garbage data of ca 15-16 bytes. Could be, that the previous owner had removed the connector, while still under power and thus wiping some EEPROM address areas with garbage...

The panel does light up and changes the backlight, but only with a black screen with no picture. I wonder if those wiped areas within the FW might contain the detailed timing infos needed to provide the right timing data.

The present invention relates to a display apparatus and a method of controlling the same, and more particularly, to a display apparatus and a method of controlling the same, which can prevent error data from being stored in an extended display identification data (EDID) storage.

To provide the Plug and Play functionality to the display apparatus, the display apparatus must previously store extended display identification data (EDID), such as a manufacturer identification (ID), a model name ID, a display power management signaling function supportability, etc., and a protocol for data communication between the display apparatus and the computer must be previously set.

In the DDC1, the display data is transmitted from the display apparatus to the computer one bit by one bit in correspondence to a vertical synchronous signal transmitted from the computer. As long as the vertical synchronous signal is inputted to the display apparatus, the display apparatus continuously and circularly transmits the EDID having a data size of 128-bytes to the computer.

In the DDC2B, when the computer asks for the EDID of the display apparatus through a serial data line (SDA) and a serial clock line (SCL), the display apparatus transmits the EDID to the computer through the SDA.

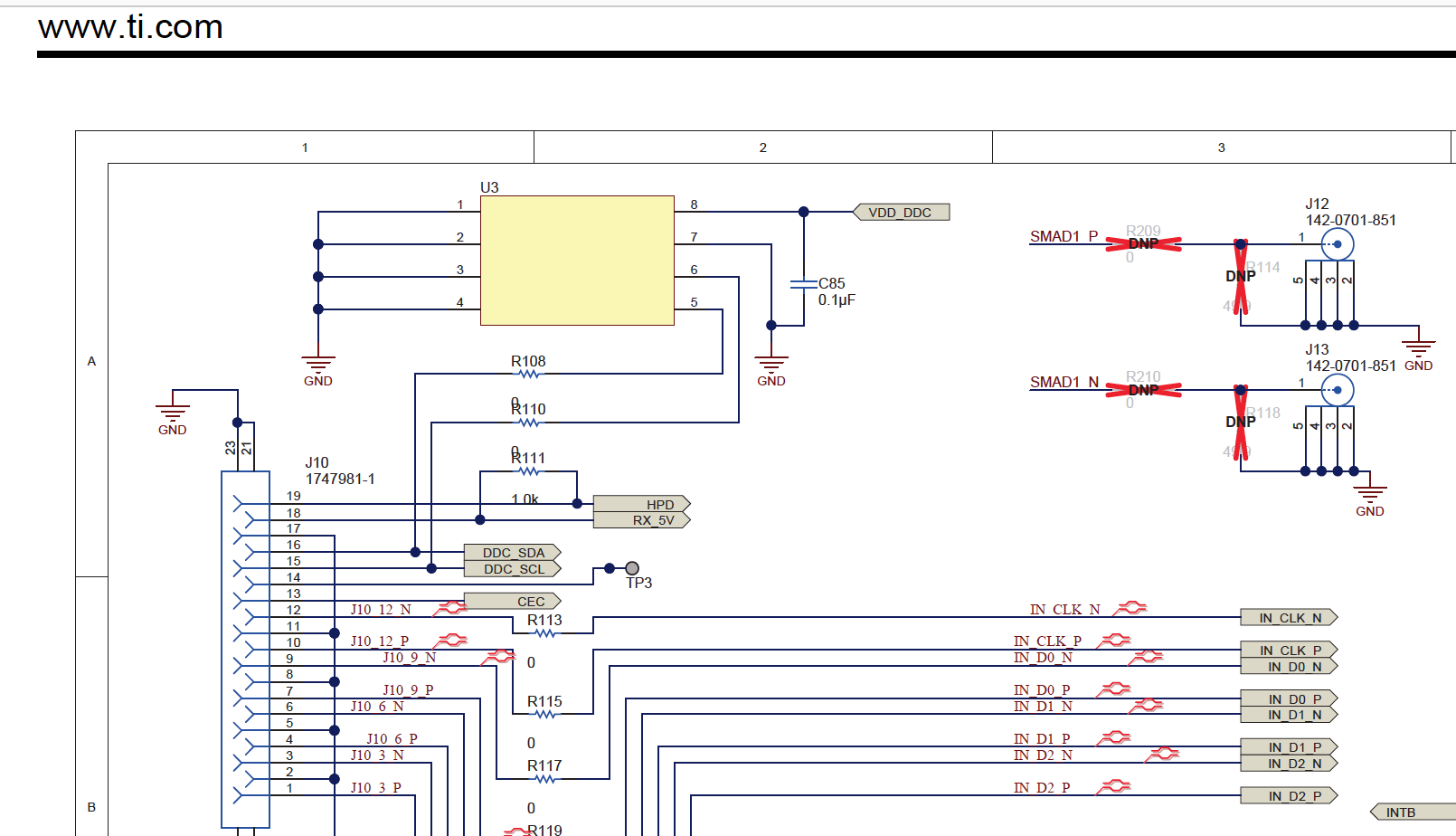

As shown in FIG. 1, in a conventional display apparatus, an EDID storage 110 is operated by at least one of a display power and a computer power. Further, the EDID storage 110 includes a write-protect (WP) port being grounded.

Here, when the WP port is in a high state, it is allowed to only read data from the EDID storage 110. In contrast, when the WP port is in a low state, it is allowed to read data from and write data to the EDID storage 110.

However, the conventional display apparatus is allowed to write data to the EDID storage 110 so long as the computer power is supplied to the EDID storage 110 regardless of the display power. Therefore, error data may be unexpectedly written to the EDID storage 110 because of an electrostatic discharge (ESD) or application malfunction while the computer is being used.

Further, in a case when the computer is turned off while accessing the EDID storage 110 to read the EDID, the data communication is interrupted and therefore the EDID storage 110 cannot receive a clock signal from the computer through the SCL, so that the EDID storage 110 becomes abnormal.

Further, in a case when the computer is turned on while the EDID storage 110 is operated by the display power, the EDID storage 110 may be supplied with an unstable power due to the computer power. In this case, if the computer accesses the EDID storage 110, the data communication is inaccurately performed.

In order to solve the above-mentioned and/or other problems, it is an aspect of the general inventive concept to provide a display apparatus and a method of controlling the same, which can prevent error data from being stored in an EDID storage.

The foregoing and/or other aspects of the general inventive concept are achieved by providing a display apparatus including a connector, a readable/writable EDID storage to store EDID, and a controller to control the EDID storage to be write-protected from error data transmitted from a computer through the connector.

According to an aspect of the general inventive concept, the connector can be selectively connected with a video card of the computer or an EDID storage jig to store the EDID, and can output a determining signal according to a determination of what is connected to the connector, and the controller can control the EDID storage to be write-protected from the error data when the controller determines that the video card is connected, and can control the EDID storage to store the EDID transmitted from the EDID storage jig when the controller determines that the EDID storage jig is connected, on the basis of the determining signal.

According to another aspect of the general inventive concept, the EDID storage may include a write-protect (WP) port, and the controller may include a microcomputer to transmit an enable signal or a disable signal to the WP port according to the determining signal of the connector.

According to another aspect of the general inventive concept, the controller can control the EDID storage to initialize a communication condition of the EDID storage when the controller determines that the video card is connected, on the basis of the determining signal.

According to yet another aspect of the general inventive concept, the EDID storage may include an I2C line port, and the controller can determine whether an I2C line is accessible when the video card is connected, and can transmit a driving signal to the I2C line port to initialize the communication condition of the EDID storage when the I2C line is accessible.

According to still another aspect of the general inventive concept, the EDID storage may include a power input port to receive a display power or a computer power, and the controller can control the EDID storage to be write-protected from the error data when the controller determines that the computer power is supplied through the power input port.

According to still another aspect of the general inventive concept, the EDID storage may include a WP port, and the controller may include a current passage to connect a computer power line with the WP port.

According to still another aspect of the general inventive concept, the EDID storage may include a WP port, and the controller may include a microcomputer to transmit an enable signal or a disable signal to the WP port according to a determination of whether the computer power is supplied.

According to still another aspect of the general inventive concept, the controller can control the EDID storage to initialize a communication condition of the EDID storage when the controller determines that the computer power is supplied.

According to still another aspect of the general inventive concept, the EDID storage may include an I2C line port, and the controller can determine whether an I2C line is accessible when the computer power is supplied, and transmits a driving signal to the I2C line port to initialize the communication condition of the EDID storage when the I2C line is accessible.

According to still another aspect of the general inventive concept, the EDID storage may include a power input port to receive display power or computer power, and a WP port being enabled when the computer power is supplied through the power input port, and the controller can control the EDID storage to be write-protected from the error data when the controller determines that the display power is supplied while the computer power is supplied.

The above and/or other aspects of the general inventive concept may also be achieved by providing a method of controlling a display apparatus having a connector and a readable/writable EDID storage to store EDID, the method including controlling the EDID storage to be write-protected from error data transmitted from a computer through the connector.

According to an aspect of the general inventive concept, the controlling of the EDID storage may include allowing the connector to output a determining signal according to a determination of whether the connector is selectively connected with a video card of the computer or an EDID storage jig, to store the EDID, and controlling the EDID storage to be write-protected from the error data when it is determined that the video card is connected, and controlling the EDID storage to store the EDID transmitted from the EDID storage jig when it is determined that the EDID storage jig is connected, on the basis of the determining signal of the connector.

According to an aspect of the general inventive concept, the method may further include controlling the EDID storage to initialize a communication condition of the EDID storage when it is determined that the video card is connected, on the basis of the determining signal of the connector.

According to another aspect of the general inventive concept, the controlling of the EDID storage may include controlling the EDID storage to be write-protected from the error data when it is determined that computer power is supplied.

According to yet another aspect of the general inventive concept, the method may further includes controlling the EDID storage to initialize a communication condition of the EDID storage when it is determined that the computer power is supplied.

According to still another aspect of the general inventive concept, the controlling of the EDID storage may include enabling a WP port when the EDID storage is supplied with computer power, and controlling the EDID storage to be write-protected from the error data transmitted from the computer when it is determined that display power is supplied.

FIGS. 7A and 7B illustrate waveforms of signal levels of a port of a microcomputer and a WP port of the EDID storage in the display apparatus of FIG. 6;

FIG. 9 illustrates waveforms of signal levels of a computer power, a port of the microcomputer, and a WP port of the EDID storage in the display apparatus of FIG. 8;

FIGS. 2 and 3 are block diagrams of a display apparatus according to an embodiment of the general inventive concept. As shown in FIGS. 2 and 3, the display apparatus may include a connector 11 to which a video card 18 of a computer or an EDID storage jig 28 can be selectively connected, an EDID storage 10 to store the EDID, and a microcomputer 12 to control the EDID storage 10 according to a determination of what is connected to the connector 11.

It is noted that other external devices can be connected to the display device alternatively. The connector 11 may be a D-sub connector, a digital video interface (DVI) connector, etc., to which the video card 18, the EDID storage jig 28, etc., is selectively connected through one or more lines coupled between the display apparatus and the external device.

As shown in FIG. 2, when the video card 18 is connected to the connector 11, the connector 11 can output a ground voltage as a ground terminal of the video card 18 and a part of the connector 11 are connected. Further, as shown in FIG. 3, when the EDID storage jig 28 is connected to the connector 11, the connector 11 can output a predetermined voltage due to a resistor 26 provided in the EDID storage jig 28. That is, the connector 11 generates one of the grounded voltage and the predetermined voltage as a determining signal according to the determination of what is connected to the connector 11, thereby transmitting the determining signal to the microcomputer 12.

The EDID storage 10 may include an electrically erasable programmable read only memory (EEPROM) to store the EDID therein. In an aspect of this embodiment of the general inventive concept, the data size of the EDID is 128-byte as shown in the following

The EDID storage 10 may include a Vcc port to receive a display power or a computer power, a write-protect (WP) port, and a serial clock line (SCL) port and a serial data line (SDA) port used as an I2C line port to communicate with the microcomputer 12 and the video card 18.

The display power transmitted through a diode 14 or the computer power transmitted from the video card 18 and through a diode 16 can be supplied to the EDID storage 10 through the Vcc port. Here, the EDID storage 10 can be operated by at least one of the display power and the computer power.

Further, when the WP port is in a high state, it is allowed to only read data from the EDID storage 10. In contrast, when the WP port is in a low state, it is allowed to read and write data to the EDID storage 10.

The SCL and SDA ports of the EDID storage 10 can be connected to the video card 18 through the connector 11, thereby forming an I2C communication interface between the EDID storage 10 and the video card 18. Further, the SCL and SDA ports can be connected to the microcomputer 12, thereby allowing the EDID storage 10 to communicate with the microcomputer 12.

The microcomputer 12 can determine whether the video card 18 or the EDID storage jig 28 is connected to the connector 11, on the basis of the determining signal generated by the connector 11.

As shown in FIG. 2, in the case where it is determined that the video card 18 is connected to connector 11, the microcomputer 12 can transmit a high signal as an enable signal to the WP port of the EDID storage 10.

On the other hand, as shown in FIG. 3, in the case where it is determined that the EDID storage jig 28 is connected to the connector 11, the microcomputer 12 can transmit a low signal as a disable signal to the WP port of the EDID storage 10.

Thus, in the case where the video card 18 is connected to the connector 11, write-protection of the EDID storage 10 can be enabled, thereby preventing accidental error data transmitted from the computer from being stored in the EDID storage 10. Further, in the case where the EDID storage jig 28 is connected to the connector 11, the write-protection of the EDID storage 10 can be disabled, thereby allowing the normal EDID to be stored in the EDID storage 10. The normal EDID is transmitted from the EDID storage jig 28 to the SCL and SDA ports of the EDID storage 10 through SCL and SDA of the connector 11.

Further, in the case where it is determined that the video card 18 is connected to the connector 11, the microcomputer 12 determines whether an I2C line is accessible. As a result of the determination, when the I2C line is accessible, the microcomputer 12 transmits a stop condition signal to both SCL and SDA ports so as to initialize a communication condition of the EDID storage 10.

That is, the microcomputer 12 can transmit several times the SCL and SDA signals corresponding to the stop condition to the SCL and SDA ports of the EDID storage 10, thereby initializing the communication condition of the EDID storage 10.

FIG. 11 is a control flowchart of operations performed in the display apparatus of FIG. 2 when the video card 18 is connected to the connector 11, and FIG. 12 is a control flowchart of operations performed in the display apparatus of FIG. 3 when the EDID storage jig 28 is connected to the connector 11.

As shown in FIG. 11, the microcomputer 12 can determine whether the video card 18 is connected to the connector 11, on the basis of the determining signal generated by the connector 11 in operation S10. When it is determined that the video card 18 is connected to the connector 11, the microcomputer 12 can transmit the enable signal to the WP port of the EDID storage 10 in operation S12, thereby preventing the error data from being written on the EDID storage 10. The microcomputer 12 can initialize the communication condition of the EDID storage 10 in operation S14.

Further, as shown in FIG. 12, the microcomputer 12 can determine whether the EDID storage jig 28 is connected to the connector 11, on the basis of the determining signal generated by the connector 11 in operation S20. When it is determined that the EDID storage jig 28 is connected to the connector 11, the microcomputer 12 can transmit the disable signal to the WP port of the EDID storage 10 in operation S22, thereby allowing the EDID transmitted from the EDID storage jig 28 to be written on the EDID storage 10.

FIG. 4 is a block diagram of a display apparatus according to another embodiment of the general inventive concept. As shown in FIG. 4, the display apparatus may include an EDID storage 30 having a Vcc port to receive a display power or a computer power through diodes 34 and 36, respectively, a WP port connected to a computer power line 38, a SCL port and a SDA port to form an I2C communication interface; and a current passage 32 to control the EDID storage 30 according to a determination of whether the computer power is supplied or not.

The current passage 32 can connect the computer power line 38 with the WP port and can lower a level of the computer power into a predetermined level through a resistor 32 bwhen the computer power is supplied to the EDID storage 30 through the Vcc port, thereby transmitting a signal having a predetermined level to the WP port.

Thus, when the computer power is supplied to the EDID storage 30 as a computer is turned on, accidental error data transmitted from the computer is prevented from being stored in the EDID storage 30.

FIG. 5 is a block diagram of a display apparatus according to another embodiment of the general inventive concept. As shown in FIG. 5, the display apparatus may include an EDID storage 40 having a Vcc port to receive a display power or a computer power through diodes 44 and 46, respectively, a WP port, and a SCL port and a SDA port to form an I2C communication interface, and a microcomputer 42 to control the EDID storage 40 according to whether the computer power is supplied or not.

The microcomputer 42 can determine whether the computer power is supplied from a video card 48 connected with a connector (not shown) through the Vcc port of the EDID storage 40, by an interrupt method or a polling method.

As a result of the determination, when it is determined that the computer power is supplied from the video card 48 to the EDID storage 40, the microcomputer 42 can transmit a high signal to the WP port, thereby preventing accidental error data transmitted from the computer from being stored in the EDID storage 40.

Further, in the case where it is determined that the computer power is supplied to the EDID storage 40, the microcomputer 42 determines whether an I2C line is accessible. As a result of this determination, when the I2C line is accessible, the microcomputer 42 can transmit a stop condition signal to both SCL and SDA ports so as to initialize a communication condition of the EDID storage 40.

First, the current passage 32 of FIG. 4 and the microcomputer 42 of FIG. 5 sense whether the computer power is supplied to the Vcc port in operation S30. When it is determined that the computer power is supplied to the Vcc port, the enable signal is transmitted to the WP port of the EDID storage 30 and 40 in operation S32, thereby preventing the error data from being written on the EDID storage 30 and 40. A communication condition of the EDID storage 30 and 40 can be initialized in operation S34, wherein the initialization is implemented by the microcomputer 42 of FIG. 5. Further, in the embodiment of FIG. 4, a controller may be provided to sense whether the computer power is supplied or not and to initialize a communication condition of the EDID storage 30.

FIG. 6 is a block diagram of a display apparatus according to another embodiment of the general inventive concept. As shown in FIG. 6, the display apparatus may include an EDID storage 50 having a Vcc port to receive a display power or a computer power through diodes 54 and 56, respectively, a WP port, a SCL port and a SDA port to form an I2C communication interface, a switch 64 switching the WP port between enable and disable modes, a selector 58 selecting the WP port to be disabled, and a microcomputer 52 to control the switch 64 according to supplying of the display power and selection of the selector 58.

In this embodiment, the WP port connected to the Vcc port becomes a high level when the computer power is supplied, so that accidental error data transmitted from the computer is prevented from being stored in the EDID storage 50.

Here, the selector 58 is achieved by a hidden key combination of the display apparatus or a command of an EDID storage jig (not shown), etc. Therefore, the selector 58 may not be easily selected by a user, and can be selected in a manufacturing process or after-sales service.

Further, supposing that the EDID storage 50 of FIG. 6 is not supplied with the display power but the computer power, the WP port of the EDID storage 50 can be the high level, thereby preventing the error data from being written on the EDID storage 50.

However, when the EDID storage 50 is initially supplied with the display power while being supplied with the computer power, the microcomputer 52 can be reset, and an output port of the microcomputer 52 connected to the switch 64 can become a high level.

When the output port of the microcomputer 52 becomes a high level, the switch 64 illustrated as an NPN transistor in FIG. 6 is turned on. Hence, the WP port of the EDID storage 50 is grounded, so that there occurs a problem that a time interval in which writing is allowed is generated.

FIGS. 7A and 7B illustrate waveforms of signal levels of the port of the microcomputer 52 and the WP port of the EDID storage 50 of FIG. 6, and FIGS. 7A and 7B refer to a push-pull port and an open-drain port of the microcomputer 52, respectively.

As shown in a waveform of a signal level (a) of FIGS. 7A and 7B, when the EDID storage 50 is initially supplied with the display power while being supplied with the computer power, the port of the microcomputer 52 instantly becomes the high level during a time interval t1. Correspondingly, as shown in a waveform of a signal level (b) of FIGS. 7A and 7B, the WP port instantly becomes the low level during the time interval t1, thereby making the EDID storage 50 be writable. Therefore, error data may be written on the EDID storage 50.

Accordingly, in this embodiment of the present general inventive concept, when the display power is supplied to the EDID storage 50, the microcomputer 52 can be reset and can transmit the low signal to the switch 64, thereby turning off the switch 64. Therefore, the WP port can be connected to the Vcc port and can become a high level, and thus error data transmitted from the computer can be prevented from being written on the EDID storage 50 when the EDID storage 50 is initially supplied with the display power while being supplied with the computer power.

When an EDID storage 70 is supplied with the display power while being supplied with the computer power through a Vcc port, a port of the microcomputer 72 connected to the first switch 88 can instantly become a high level, and thus the first switch 88 is turned on and transmits a ground signal to the second switch 84. When the second switch 84 receives the ground signal and is turned off, the WP port can be connected to the Vcc port and can become a high level. Therefore, a writable time interval in which the EDID storage 70 is writable, like the time interval t1 shown in a waveform of a signal level (b) of FIGS. 7A and 7B, can be prevented from being generated.

Meanwhile, when the microcomputer 72 determines that the WP port is selected to be disabled by the selector 78, the microcomputer 72 can transmit a low signal to the first switch 88, thereby turning off the first switch 88. Then, a high signal can be transmitted to the second switch 84, thereby turning on the second switch 84. Thus, the WP port can be grounded and can be disabled as necessary (for example, in the case when the EDID is stored in the EDID storage in the manufacturing process).

FIG. 9 illustrates waveforms of signal levels of the computer power, the port of the microcomputer 72, and the WP port of the EDID storage 70 according to another embodiment of the present general inventive concept. While the computer power is supplied as shown in a waveform of a signal level (a) of FIG. 9, the WP port may have a high level as shown in a waveform of a signal level (c), thereby protecting the EDID storage 70 from writing.

With this configuration, operations of the display apparatus of FIGS. 6 and 8 will be described hereinbelow with reference to FIG. 14. Assuming that the computer power is being supplied to the EDID storage 50 and 70.

First, the display power can be supplied to the EDID storage 50 and 70 in operation S40, and thus, the microcomputer 52 and 72 can be initialized in operation S42. Then, the microcomputer 52 and 72 can control the enable signal to be transmitted to the WP port of the EDID storage 50 and 70 in operation S44, thereby solving the problem that the WP port is disabled when the microcomputer 52 and 72 is reset.

In the above-described embodiments, the high signal is employed as the enable signal, and the low signal is employed as the disable signal. However, in the case where the WP port of the EDID storage is a low active port, a low signal may be employed as the enable signal, and a high signal may be employed as the disable signal.

Thus, the EDID storage is controlled to prevent error data transmitted from the computer through the connector from being stored in the EDID storage, thereby protecting the EDID storage from storing abnormal data.

As described above, the present general inventive concept provides a display apparatus and a method of controlling the same, which can prevent error data from being stored in an EDID storage.

The EDID is indeed just a I2C EEPROM on the lines, you can find the data structure that needs to be written into them on the internet, since you have a different resolution on the new display means you have to modify the data to report the correct thing. However there is no grantee that the motherboards BIOS actually reads the EDID. On boot the BIOS will set up the graphics card to output the correct LVDS format and in motherboards that are only ever supposed to have one display connected this is sometimes hardcoded in. Or perhaps it might use the EDID to determine from say a list of 4 different displays that this laptop model comes with and choose the right hardcoded initialization routine for it. So check that you can actually convince your motherboard into outputting the correct resolution first.

If not then you can still tap into something like a HDMI port where EDID is always used so you can make it give you any resolution you want. But that involves HDMI to LVDS conversion too.

After replacing the motherboard, i now have a different issue where i can not get a display on the LCD. I am able to hook up an external LCD and get the display to work on it.

I was able to run the Dell diagnostics and im getting an error code of 0413. The code means LCD cable not detected. I reseated the cable and still have the same issue. The cable and connector look fine and none of the pins look damaged.

Im getting what appears to be 2 different BIOS beep codes when first starting the laptop. The first one is a series of 3 short beeps, followed by 2 quick beeps and then repeats. This happens several times and then i get 8 beeps which repeat several times as well. Beep codes stop and it does boot to the Windows 7 login screen on the external LCD.

So something more than the LCD cable seems to be at fault here. Looking at the Service Manual from here: M5030 Service Manual the display cable does attach to the back of the LCD panel and is replaceable. Before i jump through the hoops of getting it replaced, i thought i would get someone elses opinion.

Reading EDID data from DVI monitor EEPROM is a common use case for the Aardvark I2C/SPI Host Adapter and DVI DDC Breakout Cable. Although the following describes DVI monitor, similar steps can be used for other DVI devices. The goal of this article is to demonstrate how to read several bytes from DVI monitor EEPROM.

The DVI Monitor EEPROM I2C target address is 0x50. The DVI Monitor EEPROM EDID length is 128 byte. In this article, Aardvark adapter reads from DVI Monitor EEPROM EDID data: 128 bytes from memory address 00 I2C target address 0x50. For additional information take a look at the EDID Documentation.

I"m faced with an interesting issue! One of our client Dell laptop does not show POST/Dell splash screen when powered on. Eventually, after a minute or two, the Windows login screen appears. I"ve replaced the LCD panel, updated BIOS, drained power, reseated everything possible, and even re-imaged the HD. Dell diagnostics gives me this error: LCD EDID - Unable to access EDI EEPROM, even after replacing the LCD panel. I"m beginning to suspect that the motherboard is the culprit here. Anyone seen this type of issue before?Just out of curiosity, what does Dell Support have to say about that error?

I"m faced with an interesting issue! One of our client Dell laptop does not show POST/Dell splash screen when powered on. Eventually, after a minute or two, the Windows login screen appears. I"ve replaced the LCD panel, updated BIOS, drained power, reseated everything possible, and even re-imaged the HD. Dell diagnostics gives me this error: LCD EDID - Unable to access EDI EEPROM, even after replacing the LCD panel. I"m beginning to suspect that the motherboard is the culprit here. Anyone seen this type of issue before?Just out of curiosity, what does Dell Support have to say about that error?

SOLVED! I replaced the LVDS cable, and I am now able to see the Dell splash screen and also access BIOS and PXE boot. Diagnostics no longer reports an error. It"s a beautiful day - birds are chirping, flowers are blooming, people are happy. Thank you all for the support!!!

Thanks for your help so far ! It does not come up in the Nividia settings but in the monitor settings if i apply it from the monitor settings and reboot i get an error saying the X sever does not support the mode.

The config file was blank so I ran sudo Nvidia-xconfig once i"d rebooted the gnome Panel had gone so remove nvidia 96 and this fixed this. I removed everything the nvidia-xconfig command put and add what you said but i get the following error :

Pi4 is using the Linux kernel standard drm/kms interface now for display mode setup, and it has far more comprehensive edid parsing than the firmware does. If the edid describes the mode correctly, then it should drive it directly.

If your display doesn"t have a valid edid, then you can add a mode via xrandr if using X. There are similar low level calls to update the framebuffer size if not running X, but I can"t quote them off the top of my head.

Pi4 is using the Linux kernel standard drm/kms interface now for display mode setup, and it has far more comprehensive edid parsing than the firmware does. If the edid describes the mode correctly, then it should drive it directly.

If your display doesn"t have a valid edid, then you can add a mode via xrandr if using X. There are similar low level calls to update the framebuffer size if not running X, but I can"t quote them off the top of my head.

let me add to this: both displays are identical (10in WXGA resolution); EDID data can be found here (that"s the file which I"m using https://drive.google.com/open?id=1ITc_e ... 420KWPr4vq

I do exactly what you"re prposing here https://www.raspberrypi.org/forums/view ... 0#p1486790 - means using EDID.dat file - but that"s doesn"t solve the problem as you can see from my recent postings here

I do exactly what you"re prposing here https://www.raspberrypi.org/forums/view ... 0#p1486790 - means using EDID.dat file - but that"s doesn"t solve the problem as you can see from my recent postings here

This would explain why legacy driver doesn"t work as expected, but still doesn"t explain why new FMKS/DRM driver - with custom resolution and timing from EDID file - fails to work (doesn"t work "out of the box" on old devices when new driver is enabled).

aBUGSworstnightmare wrote:This would explain why legacy driver doesn"t work as expected, but still doesn"t explain why new FMKS/DRM driver - with custom resolution and timing from EDID file - fails to work (doesn"t work "out of the box" on old devices when new driver is enabled).

I could expend the time downloading your EDIDs to try to replicate thereby delaying implementing propagation of hdmi_timings, or you can run "xrandr" for yourself to see where X is dumping the displays.

I could expend the time downloading your EDIDs to try to replicate thereby delaying implementing propagation of hdmi_timings, or you can run "xrandr" for yourself to see where X is dumping the displays.

Which EDID did you use? The problem is with 2x 10.1in WXGA resolution displays, one is connected to HDMI, the other one to DPI. Both displays are the same, EDID data of the display is this one https://drive.google.com/open?id=1ITc_e ... 420KWPr4vq

I"ve pointed out this issue several times already but all that has been suggested isn"t working (i.e. using EDID.dat file to get FMKS running with custom timing). There is an issue with the dpi24 overlay doing nothing (also reported).

I could expend the time downloading your EDIDs to try to replicate thereby delaying implementing propagation of hdmi_timings, or you can run "xrandr" for yourself to see where X is dumping the displays.

Which EDID did you use? The problem is with 2x 10.1in WXGA resolution displays, one is connected to HDMI, the other one to DPI. Both displays are the same, EDID data of the display is this one https://drive.google.com/open?id=1ITc_e ... 420KWPr4vq

aBUGSworstnightmare wrote:I"ve pointed out this issue several times already but all that has been suggested isn"t working (i.e. using EDID.dat file to get FMKS running with custom timing).

aBUGSworstnightmare wrote:I"ve pointed out this issue several times already but all that has been suggested isn"t working (i.e. using EDID.dat file to get FMKS running with custom timing). There is an issue with the dpi24 overlay doing nothing (also reported).

I know how to deal with custom timings and how to create EDID data, so I"m fine with both. I also have a EDID EEPROM on my board, but why should I bother myself with programming it if uisng the file fails to configure the driver correctly.

Custom hdmi timings is what is documented here, there is nothing on EDID. As there are lots of examples on the forum for hdmi_timings as well I surely want to keep it.

As suggested initially to add new mode via xrandr incase EDID was unavailable. I am facing some issues in adding a new mode below is the error I face. Can you please help me resolve this.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey