lvds lcd panel pinout brands

This is a page where you can find common laptop/desktop LCD panel pinouts and see if your laptop screen"s pinout matches any one of them (it likely does!).

This is a very common pinout for higher-resolution CCFL displays. If you have a 1440x900, 1400x1050 or 1680x1050 panel, it"s likely using this pinout.

This is a pinout for desktop LCD monitor screens - laptop panels do not use this pinout (if there are some, let me know). If you"re ordering a MT6820 (MT561) board, it will arrive with a cable that has this specific pinout and is therefore incompatible with laptop screens - as you"re likely here to reuse a laptop screen, you will want to either rewire the cable you get, or order a suitable cable (for either A or B pinout, whichever you need) from the beginning.

This is a pinout for older, 1024x768 and similar laptop screens, CCFL-equipped ones. 1024x768 screens used both the A pinout, this pinout and even a different pinout with a connector I haven"t made a description for yet, so if you have a 1024x768 screen you"d like to reuse, there"s three possible options and you need to check which one you have before you buy/reuse/build a cable.

This is a pinout that"s, apparently, specific to a select range of 18.5" 1366x768 displays used in desktop LCD monitors. It"s not compatible with either A, B or C pinouts, and requires a specifically wired cable.

In some datasheets, the pinout will list extra pins - one before and one after the main pins, both would be described something like "shield GND". So, for a FI-X 30-pin connector, you might find a pinout in your datasheet that lists 32 pins instead of 30. These two pins are not "real" connector pins and you shouldn"t worry about them - they"re pins that the manufacturer decided to mention for some reason, but they"re not relevant when you are actually connecting to the panel.

I have heard, though haven"t yet confirmed, that sometimes manufacturers mean different things by "odd" and "even" when it comes to LVDS links. If you connect your display and it works great but has swapped lines, you will likely need to rewire your cable =(

LCD panel interfaces have changed over the years as resolutions have moved from 640×480 to 3840×2160. The following outlines the common ones that we support with our LCD controllers and cable kits. They cover most of the large size and higher resolution LCD panels on the market:

LVDS: LVDS was introduced in the late 1990’s and enabled connection for higher resolution panels with the benefit of reducing EMI. The LVDS interface is supported by most Digital View LCD controllers and covers panel resolutions from 640×480 to 3840×2160 though newer formats are replacing it for higher resolutions. It remains very popular for HD type resolutions, ie up to around 1920×1200. Most LCD panel manufacturers have LCD panels supporting LVDS, including AUO, BOE, Innolux, JDI, Kyocera, LG, Mitsubishi, Sharp, Tianma. LVDS is Low Voltage Differential Switching.

V-by-One: Increasingly common on 4K resolution panels typically 55″ and larger though I did find a 32″ 1920×1080 panel and 28″ 3840×2160 panel listed as in production. A benefit of V-by-One compared to LVDS is the reduction in cables for high resolution signal support and reduced EMI. LCD panel brands using V-by-One include AUO, BOE, Innolux, LG, Samsung, Sharp. I thought of V-by-One as replacing LVDS but apparently it was developed to replace FPD-Link.

eDP: First introduced in 2008 it is widely adopted by LCD panels used in laptops and similar devices. We are also now seeing it being used in higher resolution and brightness LCD panels but still typically smaller sizes, ie 30″ or smaller. Digital View LCD controller models supporting eDP include SVX-4096, SVX-2560, SVH-1920v2 and the new DD-1920-HDMI-EDPT. Brands using it include AUO, BOE, Innolux, LG, Panasonic, Samsung, Sharp, Tianma.

TTL: Supported by the ALR-1400v2 and HLR-1400v2 controllers this was the common panel interface when Digital View was founded in 1995. VGA (640×480) to XGA (1024×768) resolutions were mainstream at that time. Still used in commercial and industrial display applications AUO, Innolux, Kyocera, Mitsubishi, Samsung, Sharp, Tianma have LCD panels in production with resolutions such as 640×480, 800×480, 800×600, 1024×768. The name TTL is short for Transistor-Transistor Logic.

FPD-Link: The original low voltage differential switching signal but not to be confused with the LVDS interface on many panels as described above. It is now often used in the automotive market and currently up to FPD-Link III. It is not currently supported by any Digital View’s standard controller models though we are looking at it as a custom development option.

First, let us start with dividing internal and external interfaces in LCD modules. Internal interface of display means it used inside the device. Those are usually the embedded interfaces that are not visible, and we do not have access to them as the users of the device. External interfaces, on the other hand, are connected to the device using a cable. Once we have defined internal and external interfaces, both of these categories come as universal or image transfer interfaces.

These Riverdi products are very advanced Intelligent Displays, made with Bridgetek controllers. The controllers use SPI and QSPI for communication. That means your software, your system, your microcontroller can be simple. You can use SPI interface to drive them, and you can still have high resolution image, even as high as 1280 by 800 pixels in 10.1-inch LCD displays. So, please remember that if you want to use a slow universal interface and have a high-resolution image, you need to use an Intelligent Display.

There are also the internal image transfer interfaces. The image transfer interface allows continuous high speed image transfer. Internal transfer is high enough to refresh the display many times per second. This is called the refresh rate of a display. When you go to a display, monitor, or TV set specification, you will see refresh rate or maximum refresh rate parameter. If it’s 60 Hertz, that means the display image is refreshed 60 times per second. More advanced displays would have higher values, like 100 Hertz. The refresh rate means we need to send full image 60 times or 100 times in each second. To visualize this amount of data, we need to multiply refresh rate by the resolution of the screen. For example, for a 7-inch Riverdi LVDS display with resolution 1024 by 600 it is roughly 600 thousand pixels.

The most common internal image transfer interface in industrial LCD displays nowadays is LVDS – Low Voltage Differential Signal. A crucial feature of this interface is that it is differential. It means that the signal is immune to interference and we can use a twisted pair of wires to transfer the data. We can send data fast and it will not be corrupt by any noise, interference. This kind of data corruption is quite common in other interfaces.Key Takeaway: In LVDS display interface the differential signal allows you to send the signal at a very high speed and keep it safe from noise.

The next, older image transfer interface is called RGB. Name comes from the colors sent parallelly to the display: red, green and blue. LVDS is a serial interface and the RGB is a parallel interface. The main difference is that RGB is not differential, so it is easier to disturb signal with noise and you configure the speed of this interface too high. Parallel interface means that we send every bit in a separate line. In theory this interface could be fast, but because it is not differential, the transfer speed is limited. Moreover, the RGB display interface will work with rather small screen sizes – usually up to 7-inch or 10-inch.

12 inch screen size is the total maximum for a LCD display with RGB interface, but the resolution will be lower, like 800 by 600. For this display size it is very low resolution. This is the reason why the 7-inch is size above which the LCD displays are being switched from RGB to LVDS interface. Among Riverdi products (if you go to the Riverdi website and to the IPS display tab), there are displays without the controller, and the small displays like 3.5-inch, 4.3-inch and 5-inch are equipped with RGB interface. But when you go to the 7-inch LCD displays tab on Riverdi website, you will find RGB, LVDS and MIPI displays. But when you go to the 10-inch or bigger displays, you will only find the LVDS displays because our 10-inch LCD displays are high resolution 1280 by 800, and it is impossible to build it with the RGB interface.Key Takeaway: RGB is low speed and not immune to noise. Use it for the smaller size displays or with lower resolution.

Next interface is the Vx1. It is similar to LVDS and MIPI, so it’s low voltage differential signal. Vx1 is a very high-speed interface, usually used in large high-resolution screens, like 55-inch 4K TVs or even larger ones. If you buy this kind of a TV set right now, probably the embedded interface inside will be the Vx1.Key takeaway: Vx1 is a super-fast interface used for high bandwidth image transfer, with high refresh rate and high-resolution displays, used in 4K screens and above.

The last internal image transfer interface is Embedded DisplayPort (eDP). We call it the new LVDS, because many new industrial displays are equipped with the eDP. If you go through industrial manufacturers of TFT LCD displays, you will notice increasing number of models available with the eDP. eDP is also a native interface in new Intel or AMD based processors.Key Takeaway: With the embedded DisplayPort as a native display interface you can cut down costs, because you do not need anything extra to connect a display to the processor.

Now, with the processors on the market, we need displays with embedded DisplayPort. Many laptops or monitors already use embedded DisplayPort as an internal interface instead of LVDS. LVDS still is the most popular industrial LCD display interface. All the internal image transfer interfaces like MIPI, Vx1 and eDP are variations of LVDS, where the protocols and the signals are a little bit different. For example, for eDP we can have lower noise and reduced power consumption. All of them have advantages over regular LVDS, but they are all LVDS type.

The connector is little bit different in each, but the pinout and everything else stays the same.Key Takeaway: HDMI is an extremely popular and easy to use interface. It can send both multimedia A/V data.

Two common high-speed communication protocols for displays are MIPI DSI and LVDS. The Mobile Industry Processor Interface, also known as MIPI, is a high-speed differential protocol that is commonly used in cellphones. Specifically, the MIPI Display Serial Interface (DSI) technology is designed for display communication. LVDS is a technique that uses differential signaling at low voltages to transmit display data. While LVDS is a broad technical specification for signaling, it has become synonymous in the display industry with the FPD-Link protocol (Flat Panel Display Link). MIPI DSI and FPD-Link are both communication protocols that use LVDS as their standard.

The MIPI DSI was designed to interface display’s for cellphones and smart devices and is the most common connection interface for these devices today. This interface uses LVDS signaling over a D-PHY layer to communicate with the display over two or four data pairs. In addition to the data lines, the MIPI interface has a differential clock pair that times the signals at a high frequency.

These clock and data lanes are triggered at low voltages which make these displays low powered. Because this interface can signal data at a very high speed, a large amount of data can be sent over the minimum frame rate requirements. This means that MIPI interface displays can be high resolution, render high color, and can be used for high-speed applications such as video transmission. Below is an example of a Focus LCDs MIPI interfaced display,. This display is a 4.3” TFT with 480x800 pixels and is connected through a 2-lane MIPI interface. Additional features of this display are reviewed below.

The Flat Panel Display Link interface (FPD-Link) has become synonymous with the LVDS interface in the display industry. The LVDS interface explained in this note will be in reference to the FPD-Link protocol. This protocol was the original high speed display interface that uses differential signaling at very low voltages to transmit data at a high frequency. This interface is most commonly used for connecting laptops and televisions to their graphics controllers. The LVDS interface transmits data over four differential data pairs six or eight bits at a time.

One example of a display that is connected through an LVDS interface is E70RA-HW520-C. This display is a 7.0” TFT with 1024x600 pixels and can display up to 16.7M colors. This display has embedded gate and a source driver IC’s that can be programmed from a standard graphics controller. Below are additional features of this LVDS display.

The display communicates over an LVDS interface to an attached HDMI module, which supports the gate and driver signaling as well as the capacitive touch interface. The LVDS interface of this display accepts RGB data in sequences of six or eight bits corresponding to the 16-bit, 18-bit and 24-bit color depths. This display has four differential data pairs and one differential clock pair.

Similar to the MIPI DSI interface, this protocol is low voltage and uses differential signaling. Additionally, this interface has low EMI noise and has a high frequency. This display operates at a clock frequency of 65MHz for the LVDS interface. The clock frequency is determined by the interface capabilities and the resolution of the display in order to maintain a refresh rate of 60Hz.

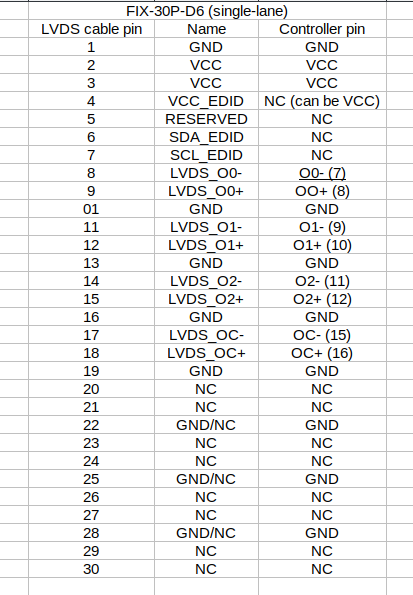

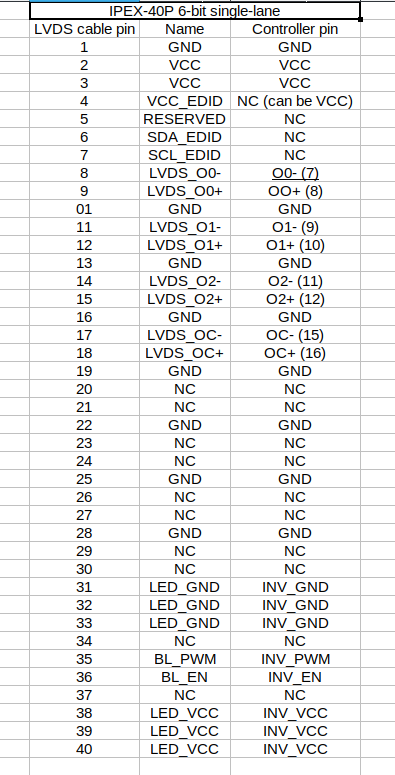

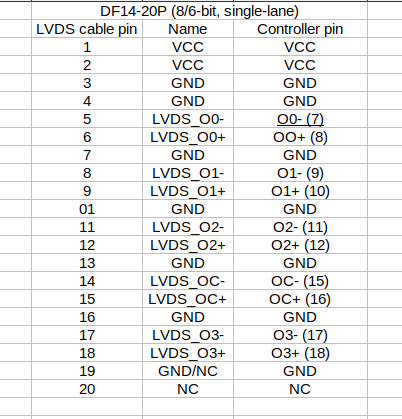

Below is a description of each of the pins that you can find on an LVDS interface display. This is a typical pin configuration for an LVDS interface display. It is important to verify that the pin connection matches with the graphics controller before connection because some LVDS displays may have alternative pin mappings and features.

The LVDS interface for displays reduces the pin count of the RGB signals to a few differential pairs. This is beneficial for hardware connection while still maintaining the large amount of data transmitted. The differential signaling also reduces EMI noise because the signals are equal and opposite and cancel out electromagnetic radiation effects. Another benefit for LVDS displays is the standard pinout for the connection cable. This makes these displays accessible to many graphic controllers and predesigned systems.

As technology advances with display communication interfaces, so do the methods of reducing the complexity of the system. MIPI DSI and LVDS have collaborated with VESA (Video Electronics Standards Association) to integrate video compression with their interfaces, which reduces the memory constraint of the display. The display technology itself is low cost, power efficient and high performing. The devices used to communicate with these displays are making progress on reducing cost and increasing availability over time.

Buyers and others who are developing systems that incorporate FocusLCDs products (collectively, “Designers”) understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers" applications and compliance of their applications (and of all FocusLCDs products used in or for Designers’ applications) with all applicable regulations, laws and other applicable requirements.

Designer agrees that prior to using or distributing any applications that include FocusLCDs products, Designer will thoroughly test such applications and the functionality of such FocusLCDs products as used in such applications.

Basic LVDS circuit operation showing current flowing in a loop back to the driver and the resulting lower radiated emission (EMI) due to field coupling within the differential pair

Low-voltage differential signaling (LVDS), also known as TIA/EIA-644, is a technical standard that specifies electrical characteristics of a differential, serial signaling standard. LVDS operates at low power and can run at very high speeds using inexpensive twisted-pair copper cables. LVDS is a physical layer specification only; many data communication standards and applications use it and add a data link layer as defined in the OSI model on top of it.

LVDS was introduced in 1994, and has become popular in products such as LCD-TVs, in-car entertainment systems, industrial cameras and machine vision, notebook and tablet computers, and communications systems. The typical applications are high-speed video, graphics, video camera data transfers, and general purpose computer buses.

Early on, the notebook computer and LCD display vendors commonly used the term LVDS instead of FPD-Link when referring to their protocol, and the term LVDS has mistakenly become synonymous with Flat Panel Display Link in the video-display engineering vocabulary.

LVDS is a differential signaling system, meaning that it transmits information as the difference between the voltages on a pair of wires; the two wire voltages are compared at the receiver. In a typical implementation, the transmitter injects a constant current of 3.5 mA into the wires, with the direction of current determining the digital logic level. The current passes through a termination resistor of about 100 to 120 ohms (matched to the cable"s characteristic impedance to reduce reflections) at the receiving end, and then returns in the opposite direction via the other wire. From Ohm"s law, the voltage difference across the resistor is therefore about 350 mV. The receiver senses the polarity of this voltage to determine the logic level.

As long as there is tight electric- and magnetic-field coupling between the two wires, LVDS reduces the generation of electromagnetic noise. This noise reduction is due to the equal and opposite current flow in the two wires creating equal and opposite electromagnetic fields that tend to cancel each other. In addition, the tightly coupled transmission wires will reduce susceptibility to electromagnetic noise interference because the noise will equally affect each wire and appear as a common-mode noise. The LVDS receiver is unaffected by common mode noise because it senses the differential voltage, which is not affected by common mode voltage changes.

The fact that the LVDS transmitter consumes a constant current also places much less demand on the power supply decoupling and thus produces less interference in the power and ground lines of the transmitting circuit. This reduces or eliminates phenomena such as ground bounce which are typically seen in terminated single-ended transmission lines where high and low logic levels consume different currents, or in non-terminated transmission lines where a current appears abruptly during switching.

The low common-mode voltage (the average of the voltages on the two wires) of about 1.2 V allows using LVDS with a wide range of integrated circuits with power supply voltages down to 2.5 V or lower. In addition, there are variations of LVDS that use a lower common mode voltage. One example is sub-LVDS (introduced by Nokia in 2004) that uses 0.9 V typical common mode voltage. Another is Scalable Low Voltage Signaling for 400 mV (SLVS-400) specified in JEDEC JESD8-13 October 2001 where the power supply can be as low as 800 mV and common mode voltage is about 400 mV.

The low differential voltage, about 350 mV, causes LVDS to consume very little power compared to other signaling technologies. At 2.5 V supply voltage the power to drive 3.5 mA becomes 8.75 mW, compared to the 90 mW dissipated by the load resistor for an RS-422 signal.

LVDS became popular in the mid 1990s. Before that, computer monitor resolutions were not large enough to need such fast data rates for graphics and video. However, in 1992 Apple Computer needed a method to transfer multiple streams of digital video without overloading the existing NuBus on the backplane. Apple and National Semiconductor (NSC) created QuickRing, which was the first integrated circuit using LVDS. QuickRing was a high speed auxiliary bus for video data to bypass the NuBus in Macintosh computers. The multimedia and supercomputer applications continued to expand because both needed to move large amounts of data over links several meters long (from a disk drive to a workstation for instance).

The first commercially successful application for LVDS was in notebook computers transmitting video data from graphics processing units to the flat panel displays using the Flat Panel Display Link by National Semiconductor. The first FPD-Link chipset reduced a 21-bit wide video interface plus the clock down to only 4 differential pairs (8 wires), which enabled it to easily fit through the hinge between the display and the notebook and take advantage of LVDS"s low-noise characteristics and fast data rate. FPD-Link became the de facto open standard for this notebook application in the late 1990s and is still the dominant display interface today

The applications for LVDS expanded to flat panel displays for consumer TVs as screen resolutions and color depths increased. To serve this application, FPD-Link chipsets continued to increase the data-rate and the number of parallel LVDS channels to meet the internal TV requirement for transferring video data from the main video processor to the display-panel"s timing controller. FPD-Link (commonly called LVDS) became the de facto standard for this internal TV interconnect and remains the dominant interface for this application in 2012.

The next target application was transferring video streams through an external cable connection between a desktop computer and display, or a DVD player and a TV. NSC introduced higher performance follow-ons to FPD-Link called the LVDS Display Interface (LDI) and OpenLDI standards. These standards allow a maximum pixel clock of 112 MHz, which suffices for a display resolution of 1400 × 1050 (SXGA+) at 60 Hz refresh. A dual link can boost the maximum display resolution to 2048 × 1536 (QXGA) at 60 Hz. FPD-Link works with cable lengths up to about 5 m, and LDI extends this to about 10 m. However, Digital Visual Interface (DVI) using TMDS over CML signals won the standards competition and became the standard for externally connecting desktop computers to monitors, and HDMI eventually became the standard for connecting digital video sources such as DVD players to flat panel displays in consumer applications.

Another successful LVDS application is Camera Link, which is a serial communication protocol designed for computer vision applications and based on the NSC chipset called Channel Link that uses LVDS. Camera Link standardizes video interfaces for scientific and industrial products including cameras, cables, and frame grabbers. The Automated Imaging Association (AIA) maintains and administers the standard because it is the industry"s global machine vision trade group.

More examples of LVDS used in computer buses are HyperTransport and FireWire, both of which trace their development back to the post-Futurebus work, which also led to SCI. In addition, LVDS is the physical layer signaling in SCSI standards (Ultra-2 SCSI and later) to allow higher data rates and longer cable lengths. Serial ATA (SATA), RapidIO, and SpaceWire use LVDS to allow high speed data transfer.

Intel and AMD published a press release in December 2010 stating they would no longer support the LVDS LCD-panel interface in their product lines by 2013. They are promoting Embedded DisplayPort and Internal DisplayPort as their preferred solution.

LVDS was originally introduced as a 3.3 V standard. Scalable low voltage signaling (SLVS) has a lower common-mode voltage of 200 mV and a reduced p-p swing, but is otherwise the same as LVDS.: 9

LVDS works in both parallel and serial data transmission. In parallel transmissions multiple data differential pairs carry several signals at once including a clock signal to synchronize the data. In serial communications, multiple single-ended signals are serialized into a single differential pair with a data rate equal to that of all the combined single-ended channels. For example, a 7-bit wide parallel bus serialized into a single pair that will operate at 7 times the data rate of one single-ended channel. The devices for converting between serial and parallel data are the serializer and deserializer, abbreviated to SerDes when the two devices are contained in one integrated circuit.

As an example, FPD-Link actually uses LVDS in a combination of serialized and parallel communications. The original FPD-Link designed for 18-bit RGB video has 3 parallel data pairs and a clock pair, so this is a parallel communication scheme. However, each of the 3 pairs transfers 7 serialized bits during each clock cycle. So the FPD-Link parallel pairs are carrying serialized data, but use a parallel clock to recover and synchronize the data.

LVDS does not specify a bit encoding scheme because it is a physical layer standard only. LVDS accommodates any user-specified encoding scheme for sending and receiving data across an LVDS link, including 8b/10b encoded data. An 8b/10b encoding scheme embeds the clock signal information and has the added benefit of DC balance. DC balance is necessary for AC-coupled transmission paths (such as capacitive or transformer-coupled paths). There are also DC-balance encoding methods for the start bit/stop bit embedded clock, which usually include a data scrambling technique. The key point in LVDS is the physical layer signaling to transport bits across wires. It is compatible with almost all data encoding and clock embedding techniques.

When a single differential pair of serial data is not fast enough there are techniques for grouping serial data channels in parallel and adding a parallel clock channel for synchronization. This is the technique used by FPD-Link. Other examples of parallel LVDS using multiple LVDS pairs and a parallel clock to synchronize are Channel Link and HyperTransport.

There is also the technique to increase the data throughput by grouping multiple LVDS-with-embedded-clock data channels together. However, this is not parallel LVDS because there is no parallel clock and each channel has its own clock information. An example of this technique is PCI Express where 2, 4, or 8 8b/10b encoded serial channels carry application data from source to destination. In this case the destination must employ a data synchronization method to align the multiple serial data channels.

The original LVDS standard only envisioned driving a digital signal from one transmitter to one receiver in a point-to-point topology. However, engineers using the first LVDS products soon wanted to drive multiple receivers with a single transmitter in a multipoint topology. As a result, NSC invented Bus LVDS (BLVDS) as the first variation of LVDS designed to drive multiple LVDS receivers. It uses termination resistors at each end of the differential transmission line to maintain the signal integrity. Double termination is necessary because it is possible to have one or more transmitters in the center of the bus driving signals toward receivers in both directions. The difference from standard LVDS transmitters was increasing the current output in order to drive the multiple termination resistors. In addition, the transmitters need to tolerate the possibility of other transmitters simultaneously driving the same bus.

Bus LVDS and LVDM (Low-Voltage Differential Multipoint) (by TI) are MLVDS) is the TIA standard (TIA-899). The AdvancedTCA standard specified MLVDS for clock distribution across the backplane to each of the computing module boards in the system.

MLVDS has two types of receivers. Type-1 is compatible with LVDS and uses a +/− 50 mV threshold. Type-2 receivers allow Wired-Or signaling with M-LVDS devices. For M-LVDS:

The present form of LVDS was preceded by an earlier standard initiated in Scalable Coherent Interface (SCI). SCI-LVDS was a subset of the SCI family of standards and specified in the IEEE 1596.3 1995 standard. The SCI committee designed LVDS for interconnecting multiprocessing systems with a high-speed low-power interface to replace positive emitter-coupled logic (PECL).

The ANSI/TIA/EIA-644-A (published in 2001) standard defines LVDS. This standard originally recommended a maximum data rate of 655 Mbit/s over twisted-pair copper wire, but data rates from 1 to 3 Gbit/s are common today on high-quality transmission mediums.

Hmmm. I am thinking that perhaps you used the wrong type cable, they are specific! Typically when this is done there will be components near the LVDS connector on the logic board that may get damaged or perhaps a chip onboard will fry instantly. However, since you still have signs of life I suggest that the connector in the logic board is damaged, look carefully (with a magnifying glass and a strong light to see if any conectiins to the connector is damaged. Also you can look inside the connector on logic board to see if any black areas are preventing a connection. There is also a fuse in that location but since you have lines this fuse should be good but there is one line obviously not making contact. Perhaps you used a used defective cable but since using the old cable gives you the same results I"m tho king it"s in either the connector inside the screen or where it attaches to logic board. I have used the striker from a book of matches to wedge inside the connector and rub gently back and forth to clean the contacts as the striker is a very fine sandpaper. You can download free Board view schematics but you may have to watch Louis Rossmann videos to get tips and if you see his board views the name of the free Board view websites is on his screen sort of a water mark. This will give you ideas of what voltages are supposed to be.

I would suggest you let someone else handle this as they will have test parts etc to eliminate the possibility of a bad cable or a bad LCD. Knowledge rules but without proper tools knowledge is almost useless.

NOT recommended procedure but while the laptop is on I have removed the LVDS cable from the logic board and slipped it in and out a few time until it worked. When and if it does work if you turn it off and on and it reverts back to lines them a diode or capacitor is likely damaged and this is a technical repair requiring SMD and a microscope, as well as a donor board to rescue parts from.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey