oxide tft lcd quotation

The interest in oxide semiconductor-based thin-film transistors (TFTs) for applications in active matrix displays (AMDs) has generated a large body of experimental and theoretical studies devoted to oxide materials; particularly amorphous-InGaZnO (a-IGZO). For applications in AMDs, reliability and stability of the TFTs used as pixel switching and driving elements are of primary concern. Although the effect of the combined negative gate bias and light stress (NBLS) has been recently investigated in a-IGZO TFTs and found to cause persistent negative threshold-voltage (VTH) shift, ways of completely eliminating this NBLS-induced instability are key to the development of AMDs such as AMLCD and AMOLED displays. The stability issues on oxide TFTs will be reviewed and discussed based on a-IGZO TFTs.

(6 November, 2017) – Oxide thin-film transistor (TFT) liquid crystal display (LCD) panels are increasingly adopted in mobile PCs due to their feature of high resolution while consuming low power. Global shipments of large oxide TFT LCD panels of 9 inches or larger are expected to grow from 20 million units in 2016 to 55.6 million units in 2017, according to new analysis from

. “Apple’ and Microsoft’s use of oxide TFT LCD panels for products – iPad, iPad Pro, and Surface, respectively – helped increase the oxide mobile PC panel market and encouraged other PC brands to follow suit.”

Low-temperature polysilicon (LTPS) and oxide TFT LCD solutions are major candidates for displaying high-resolution images, and they are expected to account for more than 19 percent of the entire mobile PC display market in 2017, according to the

While LTPS can deliver higher resolution images and consume less power than oxide TFT LCD or a-Si TFT LCD, it has its own limits: its production cost is high and the yield rate is low. In addition, it is less efficient to produce large panels. Albeit not as high resolution as LTPS, oxide TFT LCD panels still display high-resolution images better than the a-Si solution, and they are suitable to produce large panels at lower production cost than LTPS.

LG Display and Sharp have expanded their oxide mobile PC panel shipments aggressively by 180 percent and 370 percent, respectively. CEC Panda in China is estimated to increase its shipments from about 600,000 units in 2016 to 4.2 million in 2017. As some oxide panel suppliers are reducing their focus on the mobile PC display business, display makers in China and Taiwan, such as BOE and Innolux, are expected to produce more oxide panels in future, IHS Markit said.

Japan Display Inc. (JDI) has successfully developed the world"s first backplane technology to radically improve the properties of conventional oxide semiconductor thin film transistors (OS-TFT) at its G6 Plant in Mobara, Japan, and will begin immediate commercialization of this new technology.

JDI"s new OS-TFT technology generates high-mobility oxide semiconductors (HMO), which have 2X the field-effect mobility of conventional OS-TFTs, and ultra-high mobility oxide semiconductors (UHMO), which have 4X higher field-effect mobility than conventional OS-TFT (hereafter, HMO/UHMO collectively referred to as "HMO"). UHMO"s field-effect mobility on JDI"s G6 mass production line is 52cm2/Vs, an extraordinarily high level. More broadly, HMO enables the same level of on-current flow as LTPS, while maintaining low off-leak current.

Transistor I-V Characteristic ComparisonJDI believes HMO will drastically accelerate display technology innovation and contribute to significant improvements in both OLED and LCD display performance, including:

Conventional OS-TFTs have a problem of bias temperature stress (BTS), which causes poor reliability and image deterioration when trying to obtain high field-effect mobility.

However, by leveraging the manufacturing process know-how JDI has developed over many years, JDI has overcome these challenges with HMO, which is a new, breakthrough OS-TFT with superior characteristics. HMO achieves both high field-effect mobility and stable BTS to concurrently realize OS-TFT"s low off-leak current and LTPS"s image driving stability.

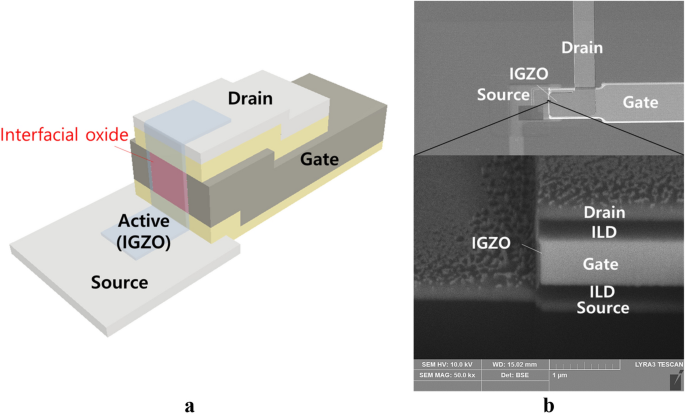

The structure of the vertical TFT with interfacial oxidation is shown in Fig. 1a. The source electrode at the bottom was made of indium tin oxide (ITO) to prevent the formation of a metal oxide insulator between the source and IGZO layer during the interfacial oxidation. The first interlayer dielectric (ILD) of SiO2 and metal gate electrode were deposited by successive sputtering, and then dry etched at one time with one photo mask. A second ILD of SiO2 and drain electrode of ITO were formed by a lift-off process, and then the gate and first ILD were dry etched by self-alignment with the drain pattern to form the vertical side wall.

After deposition of the IGZO by radio frequency (RF) magnetron sputtering, it was annealed under the oxygen atmosphere for the interfacial oxide on the side walls. As a result, the gate insulator was formed at the interface between the metal gate and IGZO active layer. The interfacial oxidation was done before the etching of the IGZO for the active layer to avoid the thick oxidation of the metal electrode which occur if the metal was not covered by the IGZO layer.

Figure 1b shows secondary electron microscope (SEM) images of the plane view and cross-sectional structure of the fabricated TFT. The vertical channel is shown between the bottom ITO electrode and top ITO electrode on the vertical side wall of the 600 nm thick gate electrode. An offset region was formed by 250 nm thick ILD layers while 600 nm channel length was defined by the 600 nm thick gate metal.

Figure 2 shows that the width of the MoOx region increases when increasing the annealing temperatures from 250 to 450 °C. At low temperatures, the interstitial oxygen can contribute to the oxidation by temperature-dependent diffusion to the interface because oxygen bond breaking from metal ions is difficult at low temperatures. The bond breaking requires much higher temperatures, so interstitial oxygen plays an important role in forming metal oxide at low temperatures. This means the oxygen ambient is very important because the oxygen continuously diffuses into the IGZO layer and migrates to the metal-IGZO interface to form metal oxide. Therefore, the adsorption and diffusion of the ambient oxygen into the IGZO layer is important for the interfacial oxidation.

To verify the effect of the oxygen atmosphere, the interfacial oxidation was examined for both oxygen and nitrogen atmospheres. Figure 3a shows HR-TEM results of the interfacial oxidation under nitrogen atmosphere, and Fig. 3b shows the result under the oxygen atmosphere. The ambient oxygen diffused into the IGZO layer by surface reaction and migrated to the IGZO layer to form metal oxide, so the oxygen atmosphere is very useful for obtaining a thicker interfacial metal-oxide for the gate insulator. The atomic percentage from the EDS analysis shows a larger oxygen ratio at the interface for the sample annealed under oxygen than that annealed under nitrogen.

The reaction of oxygen at the metal surface is important for a thicker metal-oxide at low temperatures below 400 °C For a thicker metal oxide, Ta was used instead of Mo because of its lower Gibbs free energy than that of Mo. The Gibbs free energies for MoO2 and Ta2O5 are − 533.0 and − 1911.2 kJ/mol, respectively.

Figure 4 shows the HR-TEM images of interfaces between Ta and IGZO layers for various annealing temperatures under oxygen atmosphere. The thickness of the interfacial oxide was expected to be larger in Ta than Mo due to the lower Gibbs free energy. When increasing the annealing temperatures, the interfacial oxide becomes clearer, and the thickness increases. The EDS result also matches with the HR-TEM images and shows a change of the Ta and oxygen atoms at the interface. When annealed at 450 °C anneal, the thickness of tantalum oxide was 29 nm.

Since the Ta gives thicker oxide than Mo, we choose Ta for the gate material. To avoid peel off, we keep the low thermal stress during the process. The VTFT was fabricated with interfacial oxidation between IGZO and Ta gate metal as shown in Fig. 1. The interfacial oxidation temperature was 400 °C. The transfer curves of the fabricated VTFT is shown in Fig. 5. The source-drain voltage was varied from 0.1 V to 1.0 V and the gate sweep was from − 1.0 V to 1.5 V for low-voltage operation. The thickness of the gate insulator was 15 nm, as shown in Fig. 4. The channel length was defined by the thickness of the gate metal, which was 600 nm. The channel width was defined by the photolithography and was 10 µm. The threshold voltage of the VTFT was 0.3 V, and the subthreshold slope was 0.2 V/dec. The mobility extracted from saturation region was 0.29 cm2/Vs with the gate insulator thickness of 15 nm as shown in Fig. 4. Conventional oxide VTFTs show better performances of field effect mobilities larger than 5.7 cm2/Vs

The offset is a disadvantage which should be solved to get high performance of the TFT. Since the gate metal separated source drain structure is applicable to vertical NAND flash memory, reduction of the offset effect is important. Large offset can be reduced using by decreasing the thickness of interlayer dielectric. The doping effect on the offset region is useful and can be achieved by the proper choice of the insulator which can impinge the doping elements into the IGZO layer.

For low voltage circuit applications, an inverter with the VTFT by interfacial oxidation was evaluated, as shown in Fig. 7. The channel lengths were kept the same for both the drive and load transistors, while the widths of the channel were 50 and 5 µm for the drive and load transistors, respectively.

Currents for Vds = 0.0, 0.1, 1.0 and 2.0 V are shown. Leakage currents are for the Vds = 0 V. Negative shift was observed. The process should be optimized in two aspects, one is the IGZO layer optimization for the high mobility and the other is interfacial oxide for the low leakage current and less defects. The interfacial oxidized gate insulator is the first trial and need further research to improve the characteristics of it. One drawback of the developed VTFT is the large offset length compared to the channel length which also results in a large offset AC output low. Further development on a short offset or doped offset is required.

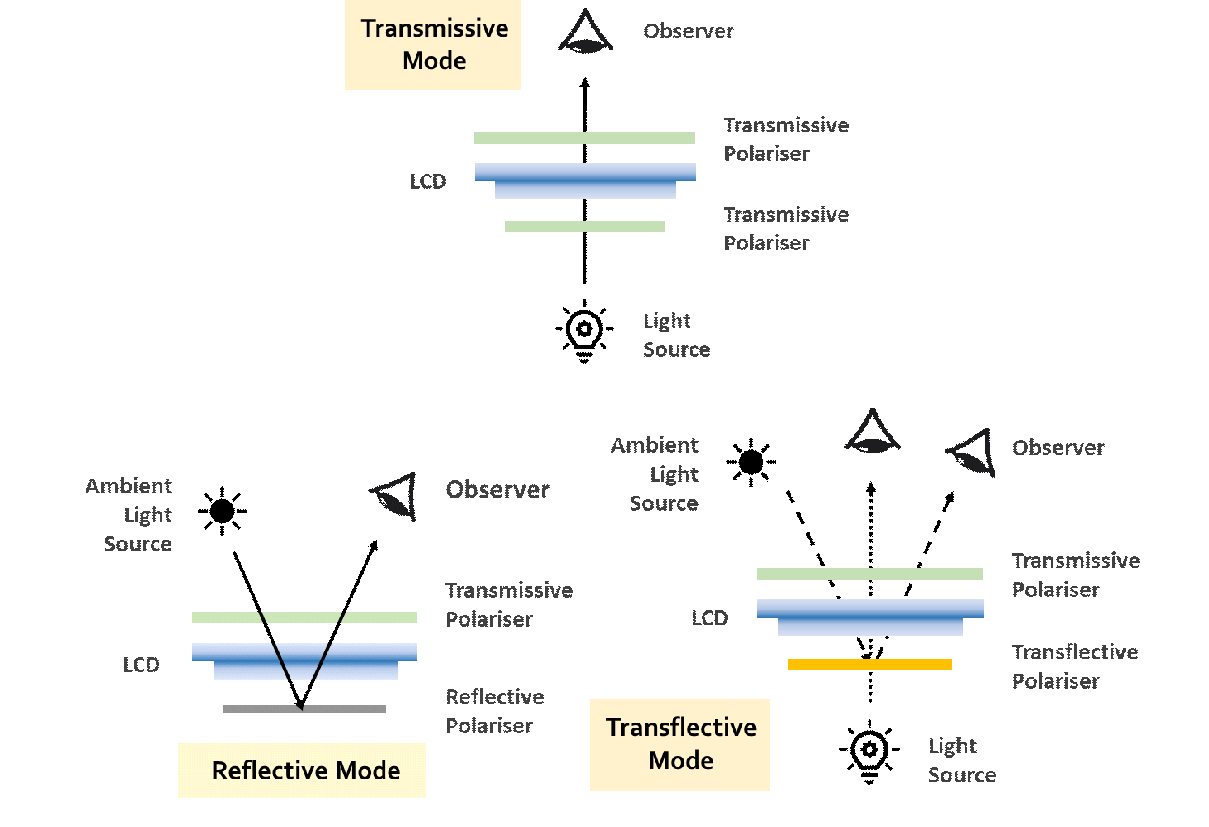

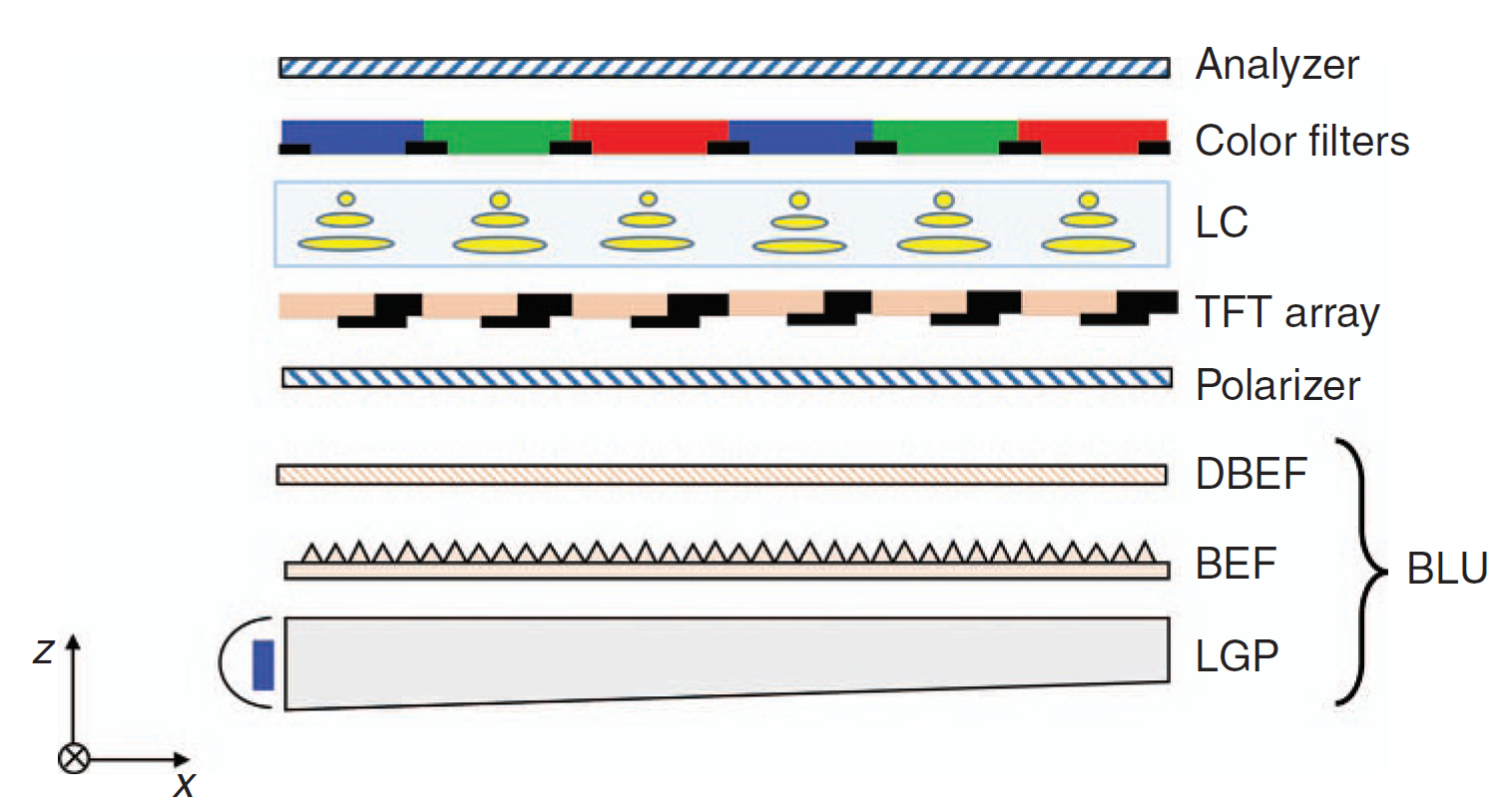

Thin-Film Transistor Liquid Crystal Displays use thin-film transistors to control the voltage applied to the liquid crystal layer at a sub-pixel level. The structure of TFT LCDs consists of a TFT “sandwich” and a BLU (Backlight Unit). A typical configuration is shown in the schematic diagram below.

Firstly, between the back and front polarizers, TFT LCD cells are made with two glass substrates – one for color filters, the other for a TFT array – and a liquid crystal layer sandwiched in between.

For normally black TFT LCDs, if we follow along a piece of light setting off from its backlight source, it will bea)guided uniformly by LGP;b)reflected and enhanced by BEF and DBEF;c)polarized by the back polarizer;d)polarization changed by twisted LC under the voltage applied by TFT arrays;e)“tinted” red/green/blue by corresponding color filter of the subpixel;f)let through the front polarizer by matched polarization; andg)finally, it will reach the surface and appears in viewer’s eyes.

Normally black LCDs have higher contrast and wider viewing angles without grayscale inversion phenomenon compared to their normally white relatives. And whether TFT LCDs are normally black or white depends on their LC switching mode:

.jpg)

We present high performance back channel etch (BCE) oxide TFT of which overlap capacitance between source/drain and gate is minimized. With considering application to the plastic LCD, we fabricated BCE TFT under 250oC with PECVD SiNx/PEALD SiO2 gate insulator and its mobility, S.S, Vth are 28.7 cm2/V.s, 0.1 V/dec, and 1.06 V, respectively. Its Vth shift under positive bias stress for 10,000 seconds is 0.75 V at 20V. BCE TFT…Expand

In an organic light-emitting diode display, hybrid thin-film transistor structures may be formed that include semiconducting oxide thin-film transistors, silicon thin-film transistors, and capacitor structures. The capacitor structures may overlap the semiconducting oxide thin-film transistors. Capacitor structures may also be formed from multiple overlapping electrode layers formed from source-drain metal layers, a polysilicon layer, and a gate metal layer may be used.

Organic light-emitting diode display pixels may have combinations of oxide and silicon transistors. Transistors such as drive transistors that are coupled to light-emitting diodes may be formed from oxide transistor structures and switching transistors may be formed from silicon transistor structures.

In a liquid crystal display, display driver circuitry may include silicon thin-film transistor circuitry and display pixels may be based on oxide thin-film transistors. A single layer or two different layers of gate metal may be used in forming silicon transistor gates and oxide transistor gates. A silicon transistor may have a gate that overlaps a floating gate structure. Oxide transistors may be incorporated into display driver circuitry.

Display driver circuitry may be configured to expose silicon transistor circuitry to lower voltage swings than oxide transistor circuitry in an array of display pixels. BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 2 is a diagram of an illustrative organic light-emitting diode display pixel of the type that may be used in an organic light-emitting diode with semiconducting oxide thin-film transistors and silicon thin-film transistors in accordance with an embodiment.

FIG. 5 is a diagram of an illustrative organic light-emitting diode display pixel of the type that may include oxide and silicon thin-film transistors in accordance with an embodiment.

FIG. 9 is a diagram of an illustrative complementary metal-oxide-semiconductor transistor inverter of the type that may be formed from a hybrid silicon-oxide transistor structure in accordance with an embodiment.

FIG. 10 is a cross-sectional side view of an illustrative thin-film transistor structure of the type that may be used to form a hybrid complementary metal-oxide-semiconductor transistor inverter in accordance with an embodiment.

FIG. 15 is a cross-sectional side view of illustrative thin-film transistor circuitry that includes a top gate semiconducting oxide transistor in a liquid crystal display in accordance with an embodiment.

FIG. 16 is a cross-sectional side view of illustrative thin-film transistor circuitry that includes a top gate semiconducting oxide transistor with a light shield in a liquid crystal display in accordance with an embodiment.

FIG. 17 is a cross-sectional side view of illustrative thin-film transistor circuitry that includes a top gate semiconducting oxide transistor in a liquid crystal display in accordance with an embodiment.

FIG. 18 is a cross-sectional side view of illustrative thin-film transistor circuitry that includes a top gate semiconducting oxide transistor in an organic light-emitting diode display in accordance with an embodiment.

Display driver circuitry such as demultiplexer circuitry 20 and gate line driver circuitry 18 may be formed from thin-film transistors on substrate 24. Thin-film transistors may also be used in forming circuitry in display pixels 22. To enhance display performance, thin-film transistor structures in display 14 may be used that satisfy desired criteria such as leakage current, switching speed, drive strength, uniformity, etc. The thin-film transistors in display 14 may, in general, be formed using any suitable type of thin-film transistor technology (e.g., silicon-based, semiconducting-oxide-based, etc.).

With one suitable arrangement, which is sometimes described herein as an example, the channel region (active region) in some thin-film transistors on display 14 is formed from silicon (e.g., silicon such as polysilicon deposited using a low temperature process, sometimes referred to as LTPS or low-temperature polysilicon) and the channel region in other thin-film transistors on display 14 is formed from a semiconducting oxide material (e.g., amorphous indium gallium zinc oxide, sometimes referred to as IGZO). If desired, other types of semiconductors may be used in forming the thin-film transistors such as amorphous silicon, semiconducting oxides other than IGZO, etc. In a hybrid display configuration of this type, silicon transistors (e.g., LTPS transistors) may be used where attributes such as switching speed and good drive current are desired (e.g., for gate drivers in liquid crystal diode displays or in portions of an organic light-emitting diode display pixel where switching speed is a consideration), whereas oxide transistors (e.g., IGZO transistors) may be used where low leakage current is desired (e.g., in liquid crystal diode display pixels and display driver circuitry) or where high pixel-to-pixel uniformity is desired (e.g., in an array of organic light-emitting diode display pixels). Other considerations may also be taken into account (e.g., considerations related to power consumption, real estate consumption, hysteresis, etc.).

Oxide transistors such as IGZO thin-film transistors are generally n-channel devices (i.e., NMOS transistors). Silicon transistors can be fabricated using p-channel or n-channel designs (i.e., LTPS devices may be either PMOS or NMOS). Combinations of these thin-film transistor structures can provide optimum performance.

Thin-film transistor structures 52 may include silicon transistor 58. Transistor 58 may be an LTPS transistor formed using a “top gate” design and may serve as a switching transistor in an organic light-emitting diode display pixel (see, e.g., transistor 30 in pixel 22-1 of FIG. 2). Transistor 58 may have a polysilicon channel 62 that is covered by gate insulator layer 64 (e.g., a layer of silicon oxide). Gate 66 may be formed from patterned metal (e.g., molybdenum, as an example). Gate 66 may be covered by a layer of interlayer dielectric (e.g., silicon nitride layer 68 and silicon oxide layer 70). Source-drain contacts 74 and 76 may contact opposing sides of polysilicon layer 62 to form the silicon thin-film transistor 58.

Thin-film transistor structures 52 may also include thin-film transistor and capacitor structures 60. Structures 60 may include a storage capacitor (i.e., storage capacitor Cst of FIG. 2) and an oxide thin-film transistor structure. The storage capacitor may have a first terminal (sometimes referred to as a plate, electrode, or electrode layer) that is formed from polysilicon layer 62′ (patterned as part of the same layer as layer 62). Gate insulator layer 64′, which may be an extended portion of gate insulator layer 64, may cover terminal 62′. The capacitor may have a second terminal formed from metal layer 66′. Metal layer 66′ may be patterned from the same metal layer that is used in forming gate 66 of transistor 58. Dielectric layers 68 and 70 may cover metal layer 66′. The thin-film transistor in structures 60 may be a “bottom gate” oxide transistor. Layer 66′, which serves as the second terminal of capacitor Cst (i.e., node A of FIG. 2) may also serve as the gate of the oxide transistor. The oxide transistor may serve as drive transistor 28 of FIG. 2. The “gate insulator” of the oxide transistor may be formed from the layer of interlayer dielectric (i.e., layers 68 and 70). The channel semiconductor of the oxide transistor may be formed from oxide layer 80 (e.g., IGZO). Oxide layer 80 may overlap polysilicon capacitor electrode layer 62′ (i.e., the oxide transistor may overlap the capacitor), thereby saving space. Source-drain terminals 82 and 84 may be formed from metal contacting opposing ends of semiconducting oxide layer 80.

Transistors such as LTPS transistors and oxide transistors may be formed with different layouts. For example, LTPS transistors tend to have high carrier mobilities. As a result, LTPS transistors may have relatively long gate lengths L and relatively short gate widths to ensure appropriately low ratios of W/L to compensate for the relatively high mobility of these transistors. This may cause LTPS transistors to be relatively inefficient for pixel layout. Oxide transistors may be constructed with W/L ratios with smaller aspect ratios (e.g., 4/4 for oxide relative to 3/30 for LTPS). Due to these layout efficiency considerations, it may be preferred to use oxide transistors as the drive transistors in display pixels 22-1. The relatively fast switching speed provided by LTPS transistor may make it preferable to use LTPS transistors for switching transistors such as transistor 30 of FIG. 2.

In display pixels with more transistors (e.g., three or more, four or more, five or more, six or more, seven or more, or eight or more), the selection of which transistors are implemented using LTPS technology and which transistors are implemented using oxide technology may be made so as to balance transistor performance considerations between the two types of transistors.

When implementing driving transistors, LTPS transistors tend to exhibit larger size (longer channel length) than oxide transistors, tend to exhibit larger dark currents than oxide transistors, and may exhibit poorer uniformity than oxide transistors. LTPS driving transistors may also exhibit more hysteresis than oxide driving transistors. As a result of these factors, it may often be advantageous to form driving transistors in an organic light-emitting diode display pixel from oxide transistors. The oxide driving transistors may exhibit low leakage current and minimal hysteresis.

When implementing switching transistors, LTPS transistors may be smaller than oxide transistors, may exhibit smaller amounts of parasitic capacitance than oxide transistors, and may exhibit lower power consumption than oxide transistors. As a result of factors such as these, it may often be advantageous to form switching transistors in an organic light-emitting diode display pixel from LTPS transistors. The LTPS switching transistors may exhibit high switching speed and low parasitic capacitance.

An illustrative hybrid thin-film transistor structure that may be used in implementing both LTPS and oxide transistors in a single organic light-emitting diode display pixel (e.g., to implement a circuit such as display pixel circuit 22-1 of FIG. 2) is shown in FIG. 4. Hybrid thin-film transistor structures 114 of FIG. 4 include silicon thin-film transistor 108, capacitor (Cst) 110, and oxide transistor 112. Silicon transistor 108 is formed from polysilicon layer 90. Gate insulator layer 92 covers polysilicon layer 90. A layer of gate metal is patterned on top of gate insulator layer 92 to form gate 94, capacitor electrode 96, and gate electrode 98. A layer of interlayer dielectric material such as silicon nitride layer 116 and silicon oxide layer 118 may cover the patterned gate metal structures. Source-drain contacts 100 and 94 for silicon transistor 108 may contact (i.e., may be shorted to) polysilicon layer 90 in the vicinity of channel region 106. Gate 94 of transistor 108 may serve as an implant mask to allow low-density drain implants to be formed in polysilicon layer 90 in regions 104 adjacent to polysilicon channel region 106 of transistor 108.

Source-drains 100 and 102 of silicon transistor 108, capacitor electrode 120, and source-drains 122 and 124 of oxide transistor 112 may be formed from patterned portions of a common metal layer on interlayer dielectric 116 and 118.

Oxide transistor 112 may have a semiconductor oxide layer such as an IGZO layer 128, source-drain contacts 122 and 124, and gate 98. Gate 98 is separated from semiconductor oxide 128, which serves as the channel region for transistor 112 by dielectric 116 and 118. Dielectric 116 and 118 therefore serves as the gate insulator for oxide transistor 112.

To optimize performance in display pixel 22-2, it may be desirable to use hybrid structures of the type shown in FIGS. 3 and 4 or other configurations for forming silicon and/or oxide thin-film transistors and capacitors. For example, it may be desirable to form drive transistor 28 from an oxide transistor (e.g., an NMOS oxide transistor), while forming switching transistors such as transistors 30-1 and 30-2 from silicon transistors or from a mixture of silicon (NMOS and/or PMOS) and oxide (NMOS) transistors.

With a first illustrative configuration, transistor 30-1 is an oxide transistor, transistor 30-2 is an oxide transistor, and transistor 28 is an oxide transistor. With a second illustrative configuration, transistor 30-1 is a silicon transistor, transistor 30-2 is a silicon transistor, and transistor 28 is an oxide transistor. A hybrid transistor structure such as the structure of FIG. 3 or the structure of FIG. 4 may be used in this scenario (e.g., to implement transistors 30-1 and 28 and capacitor Cst). With an illustrative third configuration, transistor 30-1 is a silicon transistor, transistor 30-2 is an oxide transistor, and transistor 28 is an oxide transistor. As with the second illustrative configuration, a hybrid transistor structure such as the structure of FIG. 3 or the structure of FIG. 4 may be used to implement transistors 30-1 and 28 and capacitor Cst.

If desired, display 14 may be a liquid crystal display. In this type of scenario, each pixel of display 14 may contain an electrode structure for applying an electric field to an associated portion of a liquid crystal layer in the display, a capacitor for storing charge on the electrode between frames of image data, and a thin-film transistor for controlling the application of the electric field to the electrodes. With one suitable arrangement, gate driver circuitry 18 and demultiplexer circuitry 20 (FIG. 1) in the liquid crystal display may be formed from silicon transistors and the thin-film transistors in display pixels 22 may be formed from oxide transistors. The silicon transistors have high mobility channel regions and are well suited for fast switching speeds and high drive currents while operating at low voltages and low power. The oxide thin-film transistors in display pixels 22 exhibit low leakage currents.

Thin-film transistor structures of the type that may be used in forming a liquid crystal display with both silicon and oxide transistors are shown in FIG. 6. As shown in FIG. 6, thin-film transistor structures 242 may include silicon thin-film transistor structures 216 (e.g., for forming parts of peripheral circuits such as display driver circuitry 18 and demultiplexer circuitry 20) and oxide thin-film transistor structures 240 (e.g., for forming display pixels 22 in a liquid crystal display having a layout of the type shown by display 14 of FIG. 1).

Structures 216 and 240 may be formed on buffer layer 202 on substrate 24. Polysilicon layer 204 may be deposited on buffer 202. Gate insulator layer 206 may be formed on polysilicon layer 204. A common layer of metal may be patterned to form metal structures 218, 220, and 228. Structure 218 may serve as the gate for a silicon transistor that includes source-drain contacts 212 and 214 and a channel formed from polysilicon 204. Metal structure 228 may serve as a gate for an oxide transistor formed from semiconducting oxide layer 224 (e.g., IGZO) and source-drain terminals 222 and 226. Metal structure 228 may also serve as a light shield that helps block backlight in display 14 from reaching oxide layer 224, so no separate light shielding structures need be incorporated in structures 240. Interlayer dielectric such as silicon nitride layer 208 and 210 may cover gate 218 in structure 216 and may serve as a gate insulator for gate 228 in the oxide transistor of structures 240.

Metal 230 contacts source-drain 226 of the display pixel thin-film oxide transistor that is formed from oxide layer 224. Metal 230 may be supported by organic layer 232. On the surface of organic layer 232, metal 230 may form an electrode with multiple fingers. Dielectric layer 236 may isolate electrode 230 from common electrode (Vcom) 234. During operation, electric fields are produced between electrode 230 and electrode 234. These fields pass through the liquid crystal material in the display. If desired, display 14 may incorporate capacitive touch sensors that are formed from portions of Vcom electrode 234. In this type of configuration, optional metal lines such as line 238 may be used to help reduce the resistance of the material used in forming electrode 234 (which may be, for example, a somewhat resistive conducting material such as indium tin oxide).

The thickness of layers 208 and 210 may be about 6000 angstroms. This relatively large thickness may help minimize capacitance between gate 218 and nearby metal structures such as source-drain 214, but may limit switching speeds in the oxide transistor. To address this concern, a design of the type used by structures 242′ in FIG. 7 may be used. With the FIG. 7 arrangement, an additional semiconductor fabrication mask may be used to create a gate for the oxide transistor that is formed from a separate layer of metal from the metal layer used in forming gate 218. With this approach, only a single 3000 angstrom dielectric layer 210′ (formed, e.g., from sublayers of silicon nitride and silicon oxide) is used to separate oxide transistor gate 228′ from oxide layer 224, so oxide transistor switching speed may be enhanced. The arrangement of structures 242′ of FIG. 7 allows gate 218 and gate 228′ to be formed from different metals. For example, gate 218 may be formed from a refractory metal such as Mo to accommodate the elevated temperatures associated with activating the silicon transistor, whereas gate 228′ may be formed from a lower resistance metal such as copper.

In some applications, the handling of high drive voltages (gate-to-source and drain) may need to be considered. Transistor structures 242″ of FIG. 8 may be used in scenarios in which it is desired to handle relatively large (e.g., 20 volt) swings on the silicon transistor gate. In this situation, gate insulator layer 206 may be insufficiently thin to withstand damage from a 20 volt signal. For example, gate insulator 206 may be about 800 angstroms thick, which may not be sufficiently thick to reliably handle 20 volt drive voltages. To ensure that gate insulator layer 206 is not overly stressed, gate structure 218 may be converted into a floating (electrically isolated) metal structure and an additional metal layer (i.e., part of the same metal layer that is patterned to form gate 228′ of oxide transistor 240) may be used in forming silicon transistor gate 218′. Floating gate 218 may be retained to serve as a mask for low density drain (LDD) implants made into the source and drain contact portions of polysilicon layer 204, even though floating gate 218 is not driven with control signals during operation of silicon transistor 216.

In a hybrid silicon/oxide liquid crystal display, it is not necessary to form display driver circuitry such as gate driver circuitry 18 and demultiplexer circuitry 20 from silicon transistors. If desired, some of this display driver circuitry may be formed from oxide transistors. For example, low drive current CMOS-type circuits in the peripheral circuitry of display 14 such as illustrative CMOS inverter 300 of FIG. 9 may include oxide transistors. It may be challenging to form PMOS oxide transistors, so circuits such as inverter 300 may, if desired, be formed using an NMOS oxide transistor and a PMOS silicon transistor (as an example).

Hybrid oxide-silicon thin-film transistor structures such as illustrative thin-film transistor structures 302 of FIG. 10 may be used in forming CMOS-type circuitry in display driver circuitry such as gate driver circuitry 18 and demultiplexer circuitry 20. As shown in FIG. 10, structures 302 may have a polysilicon layer 308 that is formed on substrate 24. P-channel active area 310 may be formed under gate 312. Gate insulator layer 306 (e.g., silicon oxide) may separate gate 312 from silicon channel region 310 in silicon layer 308. Dielectric layer 302 (e.g., sublayers of silicon oxide and silicon nitride) may cover gate 312. Dielectric layer 306 may separate gate 312 from overlapping oxide layer 312. Oxide layer 312 may be a semiconducting oxide such as IGZO material. Gate 312 may be formed from a first patterned metal layer. A second patterned metal layer may be used in forming output terminal 322, source terminal 316, and drain terminal 318. Passivation layer 320 may cover terminals 316 and 312. Gate 312 may be formed from materials such as molybdenum, molybdenum tungsten, tungsten, or other metals. Metal for forming structures such as metal structures 322, 316, and 318 may be formed from metal such as aluminum, molybdenum, etc.

With the arrangement of FIG. 10, gate 314 serves as a common (shared) gate for two transistors. In particular, gate 314 (see, e.g., terminal Vin of FIG. 9) serves as both a gate for a PMOS silicon transistor (transistor TP of FIG. 9) that is formed from silicon layer 308 and as a gate for an NMOS oxide transistor (transistor TN of FIG. 9) that is formed from oxide layer 312. Oxide layer 312 is located above gate 314 and silicon layer 310 is located below gate 314. The shared gate arrangement of FIG. 10 allows a CMOS inverter of the type shown in FIG. 9 to be implemented compactly.

FIG. 11 shows illustrative gate driver circuitry 18 that may be used on a liquid crystal display. Circuitry 18 may use signals with a relatively small voltage swing (e.g., a 15 volt or 16 volt swing) for silicon transistors while producing gate signals G with a larger voltage swing (e.g., a 20 volt swing or more) to ensure satisfactory operation of oxide thin-film transistors in display pixels 22 that are being driven by the gate signals.

Output signal OUT ranges from a high voltage of 15 V (or other suitable voltage) to 0 volts (or other suitable voltage). The 15 volt swing that is associated with this type of configuration can be tolerated by silicon thin-film transistors in latches 400, whereas larger voltage swings such as 20 volt swings might overly stress the silicon thin-film transistors. Level shifter 402 shifts the 15 volt to 0 volt signal OUT from latch 400 so that the output on path 406 from level shifter 402 ranges from 5 volts to −11 volts (i.e., a swing of 16 volts that can be tolerated by the silicon transistors in level shifter 402). Buffer 404 receives the 15 volt to 0 volt signal OUT from latch 400 as input signal IN_H and receives the 5 volt to −11 volt signal as input signal IN_L. Buffer 404 preferably contains silicon thin-film transistors. The design of buffer 404 allows buffer 404 to produce an output signal (gate line signal G) with a large voltage swing (e.g., 15 volts to −11 volts) of the type that is appropriate for controlling oxide transistors in the array of display pixels 22 on the liquid crystal display.

If desired, other circuit configurations may be used to allow gate driver circuitry 18 to operate in an environment in which gate line signal G has a large voltage swing to accommodate oxide transistors in display pixels 22. As an example, a subset of the level shifter transistors and a subset of the output buffer transistors may be implemented using oxide thin-film transistor structures in addition to using silicon thin-film transistor structures.

FIG. 14 is a cross-sectional side view of additional thin-film transistor circuitry of the type that may be used in a liquid crystal display. As shown in FIG. 14, thin-film transistor structures 242 may include silicon thin-film transistor structures 216 (e.g., for forming parts of peripheral circuits such as display driver circuitry 18 and demultiplexer circuitry 20) and oxide thin-film transistor structures 240 (e.g., for forming display pixels 22 in a liquid crystal display having a layout of the type shown by display 14 of FIG. 1).

Structures 216 and 240 may be formed on buffer layer 202 on substrate 24. Polysilicon layer 204 may be deposited on buffer 202. Gate insulator layer 206 may be formed on polysilicon layer 204. A common layer of metal may be patterned to form metal structures 218, 220, and 228. Structure 218 may serve as the gate for a silicon transistor that includes source-drain contacts 212 and 214 and a channel formed from polysilicon 204. Metal structure 228 may serve as a gate for an oxide transistor formed from semiconducting oxide layer 224 (e.g., IGZO) and source-drain terminals 222 and 226. Metal structure 228 may also serve as a light shield that helps block backlight in display 14 from reaching oxide layer 224, so no separate light shielding structures need be incorporated in structures 240. Interlayer dielectric such as silicon nitride layer 208 and 210 may cover gate 218 in structure 216 and may serve as a gate insulator for gate 228 in the oxide transistor of structures 240.

Metal structures 218, 220, and 228 and routing lines such as interconnect line 502 may be formed from a first metal layer (sometimes referred to as an Ml layer). Metal 222 and 226, which form source-drain contacts for the oxide transistor of structures 240, and routing lines such as interconnect line 500 may be formed from a second metal layer (sometimes referred to as an SD1 layer). Metal structures 212, 214, and routing lines such as interconnect line 506 may be formed from a third metal layer (sometimes referred to as an SD2 layer). Dielectric layers 232B may separate the second metal layer from the third metal layer. Dielectric layer 232A may separate the third metal layer from metal structures such as metal layer 234.

Metal 230 contacts metal layer 504 and is thereby coupled to source-drain 226 of the display pixel thin-film oxide transistor that is formed from oxide layer 224. Metal 230 may be supported by organic layer 232B. On the surface of organic layer 232B, metal 230 may form an electrode with multiple fingers. Dielectric layer 236 may isolate electrode 230 from common electrode (Vcom) 234. During operation, electric fields are produced between electrode 230 and electrode 234. These fields pass through the liquid crystal material in the display. If desired, display 14 may incorporate capacitive touch sensors that are formed from portions of Vcom electrode 234. In this type of configuration, optional metal lines such as line 238 may be used to help reduce the resistance of the material used in forming electrode 234 (which may be, for example, a somewhat resistive conducting material such as indium tin oxide).

FIG. 15 is a cross-sectional side view of illustrative thin-film transistor circuitry for a liquid crystal display that includes a top gate semiconducting oxide transistor. As shown in FIG. 15, thin-film transistor structures 242 may include silicon thin-film transistor structures 216 and semiconducting oxide thin-film transistor structures 240. Silicon thin-film transistor structures 216 may be used in peripheral circuits such as display driver circuitry 18 and demultiplexer circuitry 20 and/or may be used in forming circuits for display pixels 22 in a liquid crystal display. Semiconducting oxide thin-film transistor structures 240 may be used in peripheral circuits such as display driver circuitry 18 and demultiplexer circuitry 20 and/or may be used in forming circuits for display pixels 22 in a liquid crystal display. Transistors such as silicon (polysilicon) transistor 216 may be n-channel or p-channel devices. Transistors such as semiconducting oxide transistor 240 may be n-channel or p-channel devices.

Polysilicon layer 204 may be deposited on buffer 202. Gate insulator layer 206 may be formed on polysilicon layer 204. Gate insulator layer 206 may be formed from a dielectric such as silicon oxide (e.g., a 100 nm silicon oxide layer). A common layer of metal may be patterned to form metal structures 218, 220, and 228. Structure 218 may serve as the gate for a silicon transistor that includes source-drain contacts 212 and 214 and a channel formed from polysilicon 204. Metal structure 228 may serve as a gate for a top gate oxide transistor (i.e., a semiconducting oxide transistor) formed from semiconducting oxide layer 224 (e.g., IGZO) and source-drain terminals 222 and 226. One or more layers of interlayer dielectric (ILD) may cover metal structures 218, 220, and 228. For example, a first dielectric layer such as layer 208 and a second dielectric layer such as layer 210 may cover metal structures 218, 220, and 228. Layer 208 may be a silicon nitride layer and layer 210 may be a silicon oxide layer (as examples). Because there is no lateral overlap between gate 228 and source-drain electrodes 222 and 226, parasitic capacitance between gate 228 and source-drain structures 222 and 226 may be minimized. Moreover, layers 208 and 210 of the oxide transistor of FIG. 15 may be thicker than layers 208 and 210 in bottom-gate oxide transistor of FIG. 14, thereby further reducing parasitic capacitances.

Metal structures 218, 220, and 228 may be formed from a first metal layer (sometimes referred to as an Ml layer). Metal 222 and 226, which form source-drain contacts for the oxide transistor of structures 240 and metal 212 and 214, which form source-drain contacts for the silicon transistor of structures 216 may be formed from a second metal layer (sometimes referred to as an SD1 layer or M2 layer). Metal structures such as metal line 238 may be formed from a third metal layer (sometimes referred to as an M3 layer). Dielectric 232 (e.g., an organic dielectric layer such as a polymer layer) may separate the second metal layer from the third metal layer.

Metal 230 contacts source-drain 226 of the display pixel thin-film oxide transistor that is formed from oxide layer 224. Metal 230 may be supported by organic layer 232. On the surface of organic layer 232, metal 230 may form an electrode with multiple fingers (e.g., a pixel electrode for a display pixel in the display). Dielectric layer 236 may isolate electrode 230 from common electrode (Vcom) 234. During operation, electric fields are produced between electrode 230 and electrode 234. These fields pass through the liquid crystal material in the display that is formed on top of the structures of FIG. 15. If desired, display 14 may incorporate capacitive touch sensors that are formed from portions of Vcom electrode 234. In this type of configuration, optional metal lines such as line 238 may be used to help reduce the resistance of the material used in forming electrode 234 (which may be, for example, a somewhat resistive conducting material such as indium tin oxide).

As shown in FIG. 16, an optional light shielding structure such as light shield 520 can be formed under semiconducting-oxide transistor 240 or elsewhere in the display. Light shield 520 may be formed from an opaque material such as a metal, an oxidized metal, a dark polymer, or other light blocking materials. The presence of light shield 520 can help prevent stray light from disrupting the operation of semiconducting oxide transistor structures 240 or other overlapping structures.

In the example of FIG. 17, dielectric layer 232 of FIG. 15 has been divided into two dielectric layers 232A and 232B. Layer 232A may overlap the source-drain electrodes of transistors 216 and 240. Layer 232B may be interposed between the source-drain electrodes and other metal structures formed form the source-drain metal layer and layers 208 and 210. As described in connection with FIG. 14, this type of two-layer approach can reduce capacitive coupling between the metal structures of devices 216 and 240. A cross-sectional side view of illustrative thin-film transistor circuitry that includes a top gate semiconducting oxide transistor in an organic light-emitting diode display is shown in FIG. 18. As shown in FIG. 18, circuitry 72 may include display pixel structures such as light-emitting diode cathode terminal 42 and light-emitting diode anode terminal 44. Organic light-emitting diode emissive material 47 may be interposed between cathode 42 and anode 44. Pixel definition layer 46 may be a dielectric layer 46 that serves to define the layout of the display pixel. Layer 46 may be formed from a polymer such as a black polymer to help block stray light.

Transistor 58 may have a polysilicon channel 62 that is covered by gate insulator layer 64 (e.g., a layer of silicon oxide having a thickness of 100 nm or other suitable thickness). Gate 66 may be formed from patterned metal (e.g., molybdenum, as an example). Gate 66 may be covered by a layer of interlayer dielectric (e.g., silicon nitride layer 68 and silicon oxide layer 70). Source-drain contacts 74 and 76 may contact opposing sides of polysilicon layer 62 to form silicon thin-film transistor 58.

Thin-film transistor structures such as semiconducting-oxide thin-film transistor structures 60 and silicon thin-film transistor structures 58 may be used in forming part of a pixel circuit in an organic light-emitting diode display and/or may be used in forming part of peripheral circuitry 18 and 20. Thin-film transistor 60 of FIG. 18 may be a top gate semiconducting-oxide transistor. The gate insulator layer 64, which serves as the gate insulator for silicon transistor 58, also serves as the gate insulator for oxide transistor 60.

Metal gate 532 forms the gate of oxide transistor 60. The channel semiconductor of the oxide transistor may be formed from semiconducting oxide layer 128 (e.g., IGZO). Source-drain terminals 534 and 536 may be formed from metal contacting opposing ends of semiconducting oxide layer 128. Metal structures 530 and 538 may be used for routing and may be formed from the same layer of metal that is pattered to form gates 66 and 532. Structures such as source-drain structures 534 and 536 may be formed from the same layer of metal that is used in forming source-drain structures 74 and 76.

A thin-film transistor (TFT) is a special type of field-effect transistor (FET) where the transistor is thin relative to the plane of the device.substrate. A common substrate is glass, because the traditional application of TFTs is in liquid-crystal displays (LCDs). This differs from the conventional bulk metal oxide field effect transistor (MOSFET), where the semiconductor material typically is the substrate, such as a silicon wafer.

TFTs can be fabricated with a wide variety of semiconductor materials. Because it is naturally abundant and well understood, amorphous or polycrystalline silicon was historically used as the semiconductor layer. However, because of the low mobility of amorphous siliconcadmium selenide,metal oxides such as indium gallium zinc oxide (IGZO) or zinc oxide,organic semiconductors,carbon nanotubes,metal halide perovskites.

Because TFTs are grown on inert substrates, rather than on wafers, the semiconductor must be deposited in a dedicated process. A variety of techniques are used to deposit semiconductors in TFTs. These include chemical vapor deposition (CVD), atomic layer deposition (ALD), and sputtering. The semiconductor can also be deposited from solution,printing

Some wide band gap semiconductors, most notable metal oxides, are optically transparent.electrodes, such as indium tin oxide (ITO), some TFT devices can be designed to be completely optically transparent.head-up displays (such as on a car windshield).The first solution-processed TTFTs, based on zinc oxide, were reported in 2003 by researchers at Oregon State University.Universidade Nova de Lisboa has produced the world"s first completely transparent TFT at room temperature.

The best known application of thin-film transistors is in TFT LCDs, an implementation of liquid-crystal display technology. Transistors are embedded within the panel itself, reducing crosstalk between pixels and improving image stability.

As of 2008LCD TVs and monitors use this technology. TFT panels are frequently used in digital radiography applications in general radiography. A TFT is used in both direct and indirect capturemedical radiography.

The most beneficial aspect of TFT technology is its use of a separate transistor for each pixel on the display. Because each transistor is small, the amount of charge needed to control it is also small. This allows for very fast re-drawing of the display.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET in which germanium monoxide was used as a gate dielectric. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. In 1966, T.P. Brody and H.E. Kunig at Westinghouse Electric fabricated indium arsenide (InAs) MOS TFTs in both depletion and enhancement modes.

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard J. Lechner of RCA Laboratories in 1968.dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).electroluminescence (EL) in 1973, using CdSe.active-matrix liquid-crystal display (AM LCD) using CdSe in 1974, and then Brody coined the term "active matrix" in 1975.

A breakthrough in TFT research came with the development of the amorphous silicon (a-Si) TFT by P.G. le Comber, W.E. Spear and A. Ghaith at the University of Dundee in 1979. They reported the first functional TFT made from hydrogenated a-Si with a silicon nitride gate dielectric layer.research and development (R&D) of AM LCD panels based on a-Si TFTs in Japan.

By 1982, Pocket TVs based on AM LCD technology were developed in Japan.Fujitsu"s S. Kawai fabricated an a-Si dot-matrix display, and Canon"s Y. Okubo fabricated a-Si twisted nematic (TN) and guest-host LCD panels. In 1983, Toshiba"s K. Suzuki produced a-Si TFT arrays compatible with CMOS integrated circuits (ICs), Canon"s M. Sugata fabricated an a-Si color LCD panel, and a joint Sanyo and Sanritsu team including Mitsuhiro Yamasaki, S. Suhibuchi and Y. Sasaki fabricated a 3-inch a-SI color LCD TV.

The first commercial TFT-based AM LCD product was the 2.1-inch Epson ET-10Hitachi research team led by Akio Mimura demonstrated a low-temperature polycrystalline silicon (LTPS) process for fabricating n-channel TFTs on a silicon-on-insulator (SOI), at a relatively low temperature of 200°C.Hosiden research team led by T. Sunata in 1986 used a-Si TFTs to develop a 7-inch color AM LCD panel,Apple Computers.Sharp research team led by engineer T. Nagayasu used hydrogenated a-Si TFTs to demonstrate a 14-inch full-color LCD display,electronics industry that LCD would eventually replace cathode-ray tube (CRT) as the standard television display technology.notebook PCs.IBM Japan introduced a 12.1-inch color SVGA panel for the first commercial color laptop by IBM.

TFTs can also be made out of indium gallium zinc oxide (IGZO). TFT-LCDs with IGZO transistors first showed up in 2012, and were first manufactured by Sharp Corporation. IGZO allows for higher refresh rates and lower power consumption.polyimide substrate.

Petti, Luisa; Münzenrieder, Niko; Vogt, Christian; Faber, Hendrik; Büthe, Lars; Cantarella, Giuseppe; Bottacchi, Francesca; Anthopoulos, Thomas D.; Tröster, Gerhard (2016-06-01). "Metal oxide semiconductor thin-film transistors for flexible electronics". Applied Physics Reviews. 3 (2): 021303. Bibcode:2016ApPRv...3b1303P. doi:10.1063/1.4953034.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Morozumi, Shinji; Oguchi, Kouichi (12 October 1982). "Current Status of LCD-TV Development in Japan". Molecular Crystals and Liquid Crystals. 94 (1–2): 43–59. doi:10.1080/00268948308084246. ISSN 0026-8941.

Mimura, Akio; Oohayashi, M.; Ohue, M.; Ohwada, J.; Hosokawa, Y. (1986). "SOI TFT"s with directly contacted ITO". IEEE Electron Device Letters. 7 (2): 134–6. Bibcode:1986IEDL....7..134M. doi:10.1109/EDL.1986.26319. ISSN 0741-3106. S2CID 36089445.

Sunata, T.; Yukawa, T.; Miyake, K.; Matsushita, Y.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A large-area high-resolution active-matrix color LCD addressed by a-Si TFT"s". 33 (8): 1212–1217. Bibcode:1986ITED...33.1212S. doi:10.1109/T-ED.1986.22644. ISSN 0018-9383. S2CID 44190988.

Sunata, T.; Miyake, K.; Yasui, M.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A 640 × 400 pixel active-matrix LCD using a-Si TFT"s". IEEE Transactions on Electron Devices. 33 (8): 1218–21. Bibcode:1986ITED...33.1218S. doi:10.1109/T-ED.1986.22645. ISSN 0018-9383. S2CID 6356531.

Nagayasu, T.; Oketani, T.; Hirobe, T.; Kato, H.; Mizushima, S.; Take, H.; Yano, K.; Hijikigawa, M.; Washizuka, I. (October 1988). "A 14-in.-diagonal full-color a-Si TFT LCD". Conference Record of the 1988 International Display Research Conference: 56–58. doi:10.1109/DISPL.1988.11274. S2CID 20817375.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey