fpga4fun tft lcd driver brands

First: There are several types of cheap touchscreens: resistive and capacitive (intro from 3m). And under touchscreen I mean touch panels (digitizers) - the thin multilayer panels which feels touches, but don"t display anything. Touchscreens can be combined with LCD/OLED screens to get display with touch capability. Resistive touchscreens are sensitive to pressure, and you can use any stick to press them, they also had problems with multitouch (sensing several touches at same time). Capacitive touchscreens are often used now in smartphones (since iPhone), and they sense capacitance of human body, working only with fingers or special conductive styli.

So, our second step is the touchscreen controller ASIC: the device between microcontroller or FPGA and the touchscreen. Controller will do all needed magic to detect touches and translate information about them into some digital protocol, like COM (RS-232) or USB in ancient controllers for PC, or simple SPI and I2C for microcontrollers and FPGAs (you should know how to implement SPI/I2C for FPGA; the fpga4fun site may help you: spi, i2c). Many small touchscreens sold now may include some controller, integrated into their PCB or flex wire.

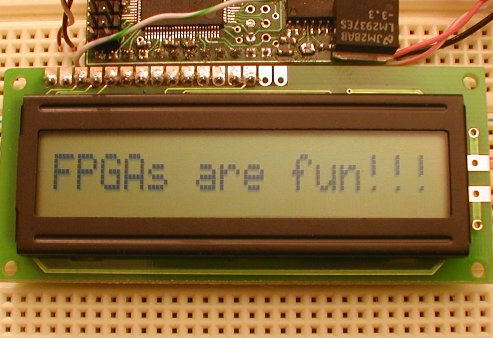

Third step: if you want to make prototype with LCD display and touchscreen, especially with small size LCD (up to 6″), the touch panel may be already integrated into display. And because virtually all LCD have the controller to output some information to display (again, fpga4fun has some introduction into using LCD with FPGAs), they probably will have integrated touchscreen controller too.

Now we can start speak about your case: "what I could buy". If you already have FPGA board, you can search for some LCD+touchscreen for some popular hardware prototyping platform, e.g. for ardoino or raspberry pi. For example, adafruit shop has both separate touch panels, lines and buttons even without controller: http://www.adafruit.com/category/60. Also they have several LCD+touch like 2.8" TFT with STMPE610 touch controller (both SPI and I2C, selectable via pin). There are several on sparkfun.com too. Make sure that you understand how to connect the LCD to FPGA, both electrical and protocol requirements. Check is there touch controller, or you need to implement it in the FPGA with ADC (and there should be ADC on your FPGA board).

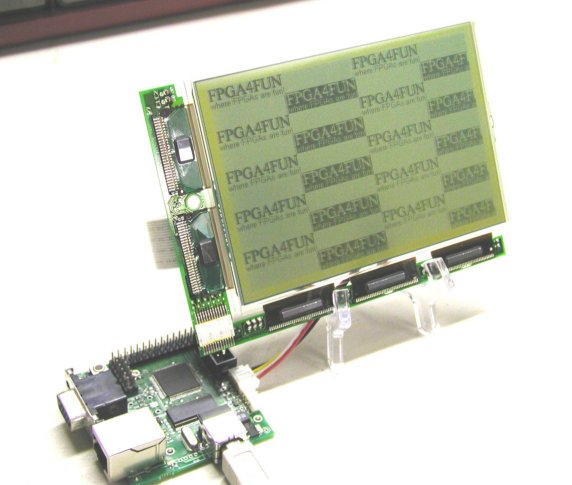

If you don"t have FPGA board or if you have no any FPGA experience, it can be better (and costly) to find FPGA kit with optional LCD+touch, but not from chinese vendors. There are lot of chinese kits in cheap section of ebay"s search "fpga touch", but they may have not so good tutorials and demo projects as right vendors. There are 7" kit from Terasic (2000 USD, VEEK-MT-C5SoC), or 7" 250USD LCD+touchpanel module for 1800 USD DE3 or 600USD DE2 FPGA boards. And for Digilent, there is 150 USD VmodTFT 4.3" TFT+touch (manual) compatible with Digilent boards with VHDCI connector, like 300 USD Nexys 3 board, 450 USD Atlys board, or 1100 USD Genesys superboard.

Digital Blocks TFT LCD Controller reference design enables you to accelerate the design-in of TFT LCD panel displays in your system. The reference design centers on the Digital Blocks DB9000AVLN TFT LCD Controller intellectual property (IP) core, which is available in netlist or VHDL/Verilog HDL register transfer level (RTL) formats.

The DB9000AVLN core contains an Avalon® Memory-Mapped system interconnect for interfacing to the Nios® II embedded processor and SDRAM or SRAM controllers (either memory can serve as the frame buffer). Software supplied with this reference design runs on the Nios II embedded processor to place an image in the frame buffer memory and invokes the DB9000AVLN core to drive the LCD panel.

Using the Intel® Quartus® Design Software, you can instantiate the TFT LCD Controller reference design in a Cyclone®, Cyclone® II, or Cyclone® III FPGA development kit. See the Demonstrated Intel® Technology section for a complete list of supported Intel® FPGA development kits.

You can connect your LCD panel to the Intel FPGA development kit with the fabrication of an appropriate cable. Please contact Digital Blocks for more details.

What are FPGAs used for in preference to microcontrollers? There are several answers to this question. Logic consolidation (where one replaces a number of digital ICs with a single IC) is a big reason for using FPGAs. Due to the large number of logic elements (LEs) and I/O pin resources in an FPGA, a number of functions can be placed inside the same FPGA. For example, an ADC controller, a number processor, and a display driver (among other functions) can be placed inside an FPGA. Many commercial products use FPGAs in this way to make products smaller, lighter, and cheaper.

Several books and websites offer help and guidance to FPGA users at all experience levels. Chief among these are FPGA manufacturer’s own websites where one can get an enormous amount of free learning resources targeting all levels of expertise; www.fpga4fun.com is a popular website with several introductory and mid-level projects for hobbyists to build.

If we know how the LCD is receiving the data, we need to think how we can create an IP block that generates the same waveform. For that, we need at least 3 modules. SPI TX (spi_4l_8b.v) and memory module (spi_4l_8b_fifo.v) for configuration data. Some commands require a delay before sending the next command, for example,"software reset" or "sleep off". For that, we will add another module (spi_4l_8b_cmd_delay.v) that detects a particular command and stalls SPI transactions for a fixed amount of time.

First, let"s start with TX module. This module only responsibility is sending data to the LCD. When input AXI4-stream interface is valid, the module copies data to "command" reg and sends the data bit by bit.module spi_4l_8b(

With power of Vivado we have a possibility to define sequence of ili operations and use Verilog tasks in initial block like a software function that sends command to the LCD. Normally we should use $readmemh for sake of project portability as not all vendors support initial begin - task memory initialization.`define ili_NOP 8"h00 // No Operation - NOP

The testbench is really simple, as the FIFO needs to program LCD, it generates a known list of vectors that need to be serialized and displayed at SPI output. If input data is a command, we should see no operation in the simulation waveform for a while.`timescale 1ns / 1ns

Add SPI modules to block design, by dragging them from sources and other IPs for generating LCD signal and also a VIO for reset control. Minized PS IP FCLK_CLK0 is 50Mhz. LCD module maximum frequency is 10Mhz, so we need to use clocking wizard IP to lower clock frequency.

Generate bitstream and program Minized. If you have problems with VIO control, try to lower JTAG frequency. Use VIO to control the reset bit, as reset is active low, set this bit to high and look at the LCD.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey