tft lcd frame buffer manufacturer

TFT LCDs have become the norm for small-to-medium size displays in a variety of products within industrial, medical, POS and consumer applications. Compared to passive-addressed monochrome LCDs, TFT displays offer higher contrast, wider viewing angles, faster response time and full color. And, TFT LCDs are now on cost parity with similar size passive LCD displays.

A typical TFT LCD module product consists of a TFT LCD panel, one or more COG (chip-on-glass) driver ICs, a backlight unit, and an interface FPC. Several TFT display interface technologies coexist today. Picking the right technology depends on specific end-product concerns. Most often the display panel input will dictate that choice since TFT panels are designed to be COG bonding pad compatible with a very limited number of driver ICs. This article discusses the interfaces between TFT LCD modules and the typical CPUs found in embedded applications.

Typical TFT interfaces are determined by the particular TFT panel size and resolution, as shown in the below table. HDMI and eDP require interface converting boards and generally are not used for small to medium-size TFT LCDs.TFT LCD SizesResolutionsTypical Interfaces UsedUp to 3.5″128×160 to 240×320SPI, parallel MPU or RGB

Only the three SPI signals, a CS, and a reset signal are needed. Drawbacks are the inability to read from the display, only write. Also, the frame rate is low and unsuitable for displaying video or high-resolution images.

The LCD controller signals are two types: data signals and control signals. The data signals are connected to the LCD data bus and depend on the LCD color depth (8-bit, 9-bit, 16-bit, 18-bit). The control signals are used to define the operation type (read or write), and whether the operation involves in addressing LCD registers or the display RAM.

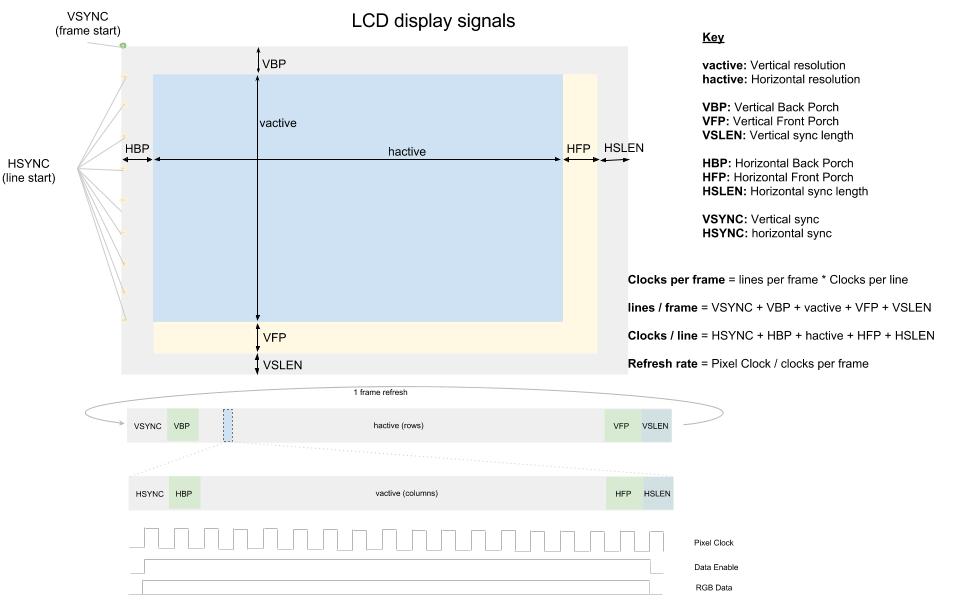

An RGB interface is a special kind of parallel interface. This interface works for displays without a frame buffer. The MCU is responsible for updating the display, by providing both the RGB sub-pixel data (16-bit, 18-bit, 24-bit) and the timing signals (HSYNC, VSYNC, DE, CLK).

LVDS interfacing has several benefits for TFT displays. It is much less susceptible to EMI and crosstalk issues, allowing the transmitting device to be located farther from the display. Also, LVDS generally consumes less power, pin counts are lower and there are far fewer worries about signal integrity.

Modern TFT driver ICs are highly integrated chips combining the source driver, gate driver and timing controller (TCON) – as well as other functional circuits such as memory, power circuit, and image processors – into one single IC die. Some driver ICs support multiple interfaces that are selectable on the module FPC or through initialization code firmware.

As a designer and manufacturer of custom LCD modules, New Vision Display works with customers to select the most appropriate and cost-effective TFT display and electronic interface solution for their particular requirement. New Vision Display has nearly 30 years of industry experience as one of the world’s leading TFT LCD screen manufacturers.

INT070ATFT and INT070ATFT-TS are embedded display driver boards based on the Displaytech 7 inch 800 x 480 RGB resolution TFT display module. This embedded driver board includes a 7" standard or resistive touchscreen display. Mounted on the embedded board is the Solomon Systech SSD1963 LCD controller that supports common RAM-less LCD drivers and offers the following features and benefits:

I"m talking about some nxp mcu like lpc1788 with the lcd controller integrated into the chip so you don"t need to use an external lcd controller. The models you are listing don"t have the lcd controller integrated,.

The main advantage of having it external is that the lcd controller has got its own memory for the frame buffer and it"s easing the load on the cpu because once you load the data it will keep refreshing the screen without calling the cpu and it doesn"t use the cpu ram memory.

In the other case if the lcd controller is integrated in the mcu you can do some nice "tricks" like using a colour look up table or palette so that your graphics takes less memory and because the framebuffer is in your internal memory it is even easier to manipulate.

Also consider that in case of lcd controller not integrated in the panel (so by using the one integrated in the mcu or another one on board as a separate chip) you can exchange panel quite easily so you are not tied to a single manufacturer as long on the lcd side you find the same interface like the 24 bit or the 18 bit.

Now, I"m considering the case of an lcd panel of 640x480 and 8 bit per colour which leads us to 640x480x8 = 2457600 bit / 8 = 307200 / 1024 = 300 KByte of ram needed for the framebuffer.

The integrated lcd controller has got a dma which will take care of transferring the data from external ram used for the frambuffer to the lcd controller which will then translate it and send to lcd but the problem is that the external bus and also the internal bus of the mcu(difficult to draw this here :-) ) is then shared by the lcd controller, which keeps accessing the memory to continuously refresh the screen, and the mcu which is fetching instructions or variables.

Because the internal bus gives priority to the mcu it means that probably you will see tearing effect on the lcd like reported by some people on the nxp question and answer (pasting the link here takes you to the general support page and not to the answer I found) because the mcu gain priority when accessing bus and memory and lcd refresh is delayed.

In the answer I found on Nxp support, they say you can actually change priority so that lcd screen has an higher priority then the cpu, problem is that in doing so the cpu and then your software will be slowed down by the lcd controller continuously refreshing and accessing memories.

The FBTFT drivers are now in the Linux kernel staging tree: https://git.kernel.org/cgit/linux/kernel/git/gregkh/staging.git/tree/drivers/staging/fbtft?h=staging-testing

![]()

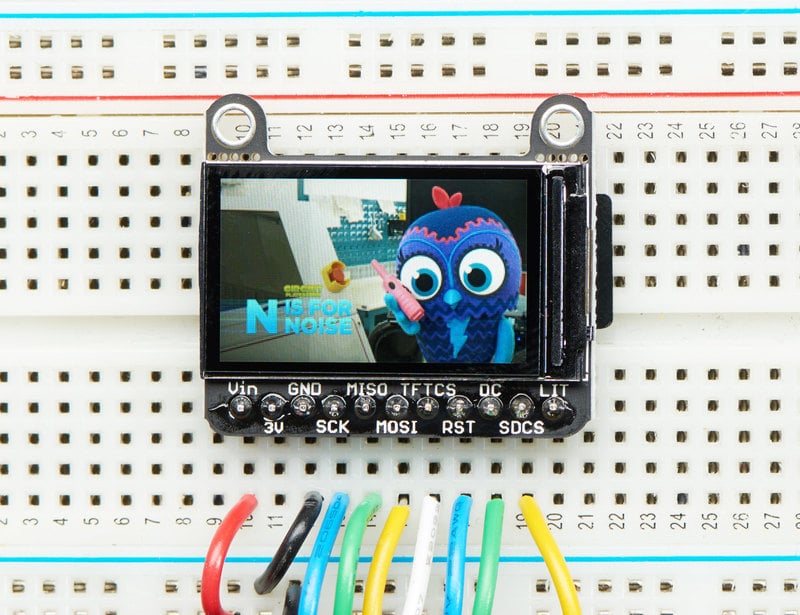

notro recently wrote in to share these drivers for small TFT LCD modules:Hi, I want to let you know that I have added Linux framebuffer support for the following Adafruit displays:

2.2″ 18-bit color TFT LCD display with microSD card breakout – ILI9340 – This lovely little display breakout is the best way to add a small, colorful and bright display to any project. Since the display uses 4-wire SPI to communicate and has its own pixel-addressable frame buffer, it can be used with every kind of microcontroller. Even a very small one with low memory and few pins available! (read more)

1.8″ 18-bit color TFT LCD display with microSD card breakout – ST7735R – This lovely little display breakout is the best way to add a small, colorful and bright display to any project. Since the display uses 4-wire SPI to communicate and has its own pixel-addressable frame buffer, it can be used with every kind of microcontroller. Even a very small one with low memory and few pins available! (read more)

The new line of 3.5” TFT displays with IPS technology is now available! Three touchscreen options are available: capacitive, resistive, or without a touchscreen.

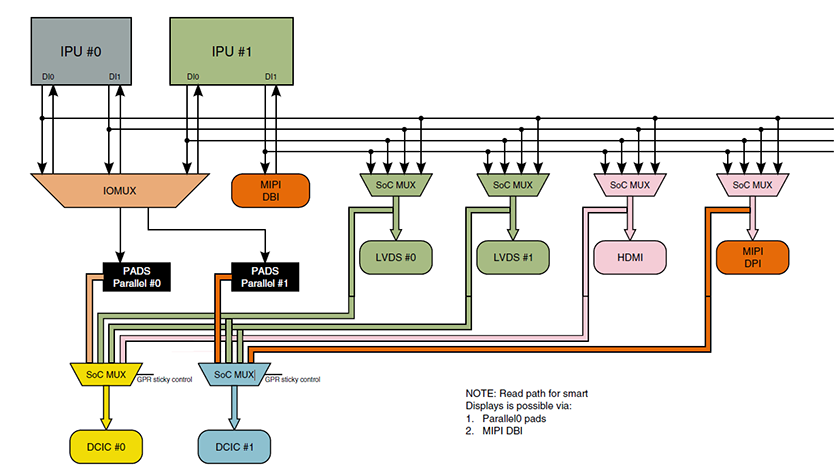

This application note describes the i.MX6 CPU graphical system and the steps to define a new custom TFT (Thin Film Transistor) display panel in Digi Embedded Yocto and discusses the most standard panels available. Some panels may need special consideration.

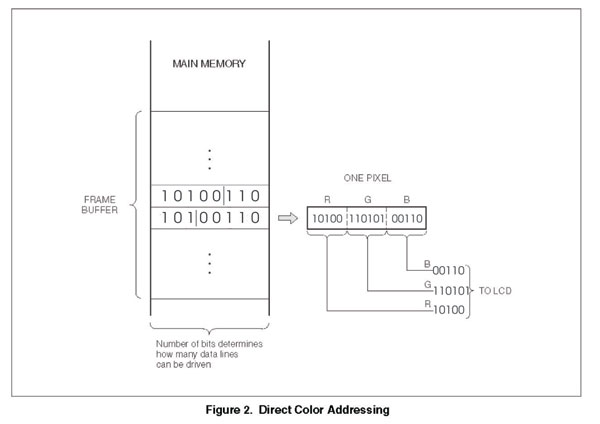

An LCD panel is a matrix of pixels that are divided into rows and columns. These pixels are individually painted according to different signals and timing parameters, and you can control each pixel"s color individually. The panel is continuously refreshed, typically at around 60 Hz, from the contents of the frame buffer memory. Each memory location on the frame buffer corresponds to a pixel on the LCD panel.

A 1024 x 600 resolution display requires 614400 memory locations, with each location having a number of possible colors. The number of bits needed to describe the available colors is called bits per pixel (bpp). For example, 16 bpp can describe 65536 colors and 24 bits can describe 16777216 colors (known as true color). A panel with 614400 24-bit locations requires a 1800 KB frame buffer.

VSYNC: Vertical synch (FPFRAME, FLM, SPS or TV) indicates the end of the current frame. The next line index should restart at zero in the upper-left corner.

Every manufacturer provides display timings in a slightly different way and some provide more detail than others. Most LCD panels work with a range of timing parameters.

The i.MX6 IPUs define a series of frame buffer devices (/dev/fbN, where N is an index number starting at zero) that correspond to the graphical capabilities of the SoC.

The i.MX6 Dual/Quad has two IPUs, each containing two DIs. Additionally, the driver allows for an overlay frame buffer per IPU (to be displayed over the frame buffer of DI0). These overlay frame buffers are also represented by nodes /dev/fbN.

Frame buffer devices provide an abstraction for the graphics hardware. You must create a frame buffer entry on your platform"s device tree file and bind it to a graphics driver through the compatible property.

The following example creates a frame buffer and binds it to the MXC frame buffer device driver (drivers/video/mxc/mxc_ipuv3_fb.c).Frame buffer node binding to MXC graphics drivermxcfb1: fb@0 {

The driver"s binding documentation at Documentation/devicetree/bindings/fb/fsl_ipuv3_fb.txt describes additional properties for the frame buffer. You must complete the node with required and optional properties that match your hardware, for example:

You can create as many frame buffer entries as you have available display interfaces in your platform. For example, the i.MX6 Dual/Quad has two IPUs, each containing two display interfaces, equaling a total of four displays:

LCD displays must be created as nodes in the device tree with a display-timings subnode. Display timings binding documentation at Documentation/devicetree/bindings/video/display-timing.txt explains the required timing properties to describe an LCD.lcdname {

hfront-porch is the horizontal front porch, the number of clock pulses (pixels) between the last valid pixel data in the line and the next HSYNC pulse. According to the LCD data format, this value is zero.

vfront-porch is the vertical front porch, the number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse. According to the LCD data format, this value is zero.

NoteThe recommended timings from the LCD datasheet often do not work perfectly, as each platform introduces noise and delays that affect the display"s signals and timings.

vfront-porch is the vertical front porch, the number of lines (HSYNC pulses) between the last valid line of the frame and the next VSYNC pulse. The datasheet does not provide this number but it provides the complete Vertical period (TV) and the Vertical period (High) (TVd) so you can calculate the vertical front porch as TV - TVd = 831 - 800 = 311.

To run the application, call fbtest from a console. The application shows the test color chart by default to frame buffer 0 (/dev/fb0). To show the test color chart on a different frame buffer, export the variable FRAMEBUFFER:export FRAMEBUFFER=/dev/fb2

This color chart displays a white one-pixel frame at the edges of the LCD (which allows you to verify correct position and width/height), and gradients of red, green, blue, and white (which allow you to verify correct color depth and format).

Digital Blocks TFT LCD Controller reference design enables you to accelerate the design-in of TFT LCD panel displays in your system. The reference design centers on the Digital Blocks DB9000AVLN TFT LCD Controller intellectual property (IP) core, which is available in netlist or VHDL/Verilog HDL register transfer level (RTL) formats.

The DB9000AVLN core contains an Avalon® Memory-Mapped system interconnect for interfacing to the Nios® II embedded processor and SDRAM or SRAM controllers (either memory can serve as the frame buffer). Software supplied with this reference design runs on the Nios II embedded processor to place an image in the frame buffer memory and invokes the DB9000AVLN core to drive the LCD panel.

Using the Intel® Quartus® Design Software, you can instantiate the TFT LCD Controller reference design in a Cyclone®, Cyclone® II, or Cyclone® III FPGA development kit. See the Demonstrated Intel® Technology section for a complete list of supported Intel® FPGA development kits.

You can connect your LCD panel to the Intel FPGA development kit with the fabrication of an appropriate cable. Please contact Digital Blocks for more details.

Digital Blocks TFT LCD Controller reference design enables you to accelerate the design-in of TFT LCD panel displays in your system. The reference design centers on the Digital Blocks DB9000AVLN TFT LCD Controller intellectual property (IP) core, which is available in netlist or VHDL/Verilog HDL register transfer level (RTL) formats.

The DB9000AVLN core contains an Avalon® Memory-Mapped system interconnect for interfacing to the Nios® II embedded processor and SDRAM or SRAM controllers (either memory can serve as the frame buffer). Software supplied with this reference design runs on the Nios II embedded processor to place an image in the frame buffer memory and invokes the DB9000AVLN core to drive the LCD panel.

Using the Intel® Quartus® Design Software, you can instantiate the TFT LCD Controller reference design in a Cyclone®, Cyclone® II, or Cyclone® III FPGA development kit. See the Demonstrated Intel® Technology section for a complete list of supported Intel® FPGA development kits.

You can connect your LCD panel to the Intel FPGA development kit with the fabrication of an appropriate cable. Please contact Digital Blocks for more details.

Supplied in 176-pin QFP package, single-chip TX4964FG drives and manages TFT LCD panels found in instrument clusters in automobiles. SoC integrates 120 MHz MIPS-based(TM) TX49/L4 64-bit CPU core, TFT LCD panel controller, digital-camera interface, peripheral controllers, and frame-buffer memory. Its 4 MB embedded DRAM eliminates need for external RAM ICs, reducing system-level power. Also included, dedicated hardware engines for cluster graphics deliver up to 32-bit RGBA colors.

SAN JOSE, Calif., June 13 -- Toshiba America Electronic Components, Inc. (TAEC)*, a committed leader that collaborates with technology companies to create breakthrough designs, today announced the expansion of the Toshiba family of automotive graphics and display controllers with a new system-on-chip (SoC) targeted at instrument-cluster applications ranging from back-up camera displays to full-size, reconfigurable instrument clusters. Designated TX4964FG, the new single-chip solution drives and manages the small-size thin-film transistor (TFT) LCD panels increasingly found in instrument clusters in medium- to high-end automobiles. The highly integrated device integrates the CPU, hardware-graphics engine, TFT LCD panel controller, digital-camera interface and frame-buffer memory in a compact 176-pin QFP package. Its 4 Mbytes of embedded DRAM eliminate the need for external RAM ICs, thereby reducing system-level power and contributing to the small footprint.

"Toshiba took an innovative system approach and developed the new IC to support growing demand from vehicle manufacturers to reduce the system cost, complexity and component count of implementing TFT displays in sizes that typically range from 3-inch to 5-inch and with up to VGA resolution," said Shardul Kazi, vice president of the ASSP Business Unit at Toshiba America Electronic Components, Inc. He said that center-stack displays are gaining acceptance for navigation systems as drivers accustom themselves to using them and reap the benefits of having needed information inside the dashboard in the driver"s focus zone.

The TX4964FG replaces four ICs and reduces design complexity through the integration of a powerful processor, an advanced graphics display controller with dedicated accelerator functions, and a comprehensive range of on-board peripherals and interfaces. The new SoC features Toshiba"s low-power, high-performance MIPS-based(TM) TX49/L4 64-bit CPU core operating at 120 megahertz (MHz). An integrated graphics display controller together with specialized accelerator engines deliver graphics processing and display-control capabilities. Dedicated hardware engines for cluster graphics can deliver up to 32-bit RGBA colors. The graphic accelerator enhances the display output and offers high-quality anti-aliasing to ensure smooth graphics display. The frame grabber works with a wide variety of input data formats; it captures and processes video images and supports applications such as rear-view monitoring.

A framebuffer is a copy of the display information that is resident within the RAM of the microcontroller. It must be as large as the display. For a 128X64 monochrome display this would be 128 * 64 = 8192 bits or 1,024 bytes (1K). A full color 240X240 TFT which uses 8 bits for red, green and blue would require 3 X 8 X 240 X 240 = 1,382,400 bits or 172K bytes.

Not all all displays need framebuffers. Some displays can take a series of vector drawing commands such as "draw line" and "draw text". These displays can be useful if you don"t have a large amount of RAM.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey